1.内部晶振参数

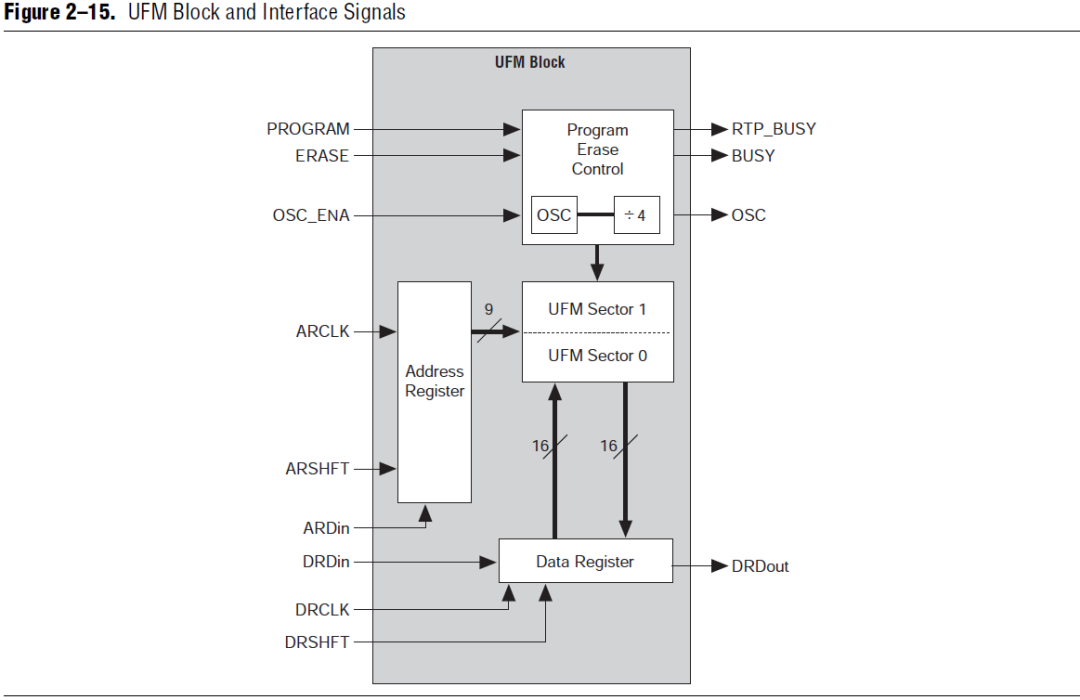

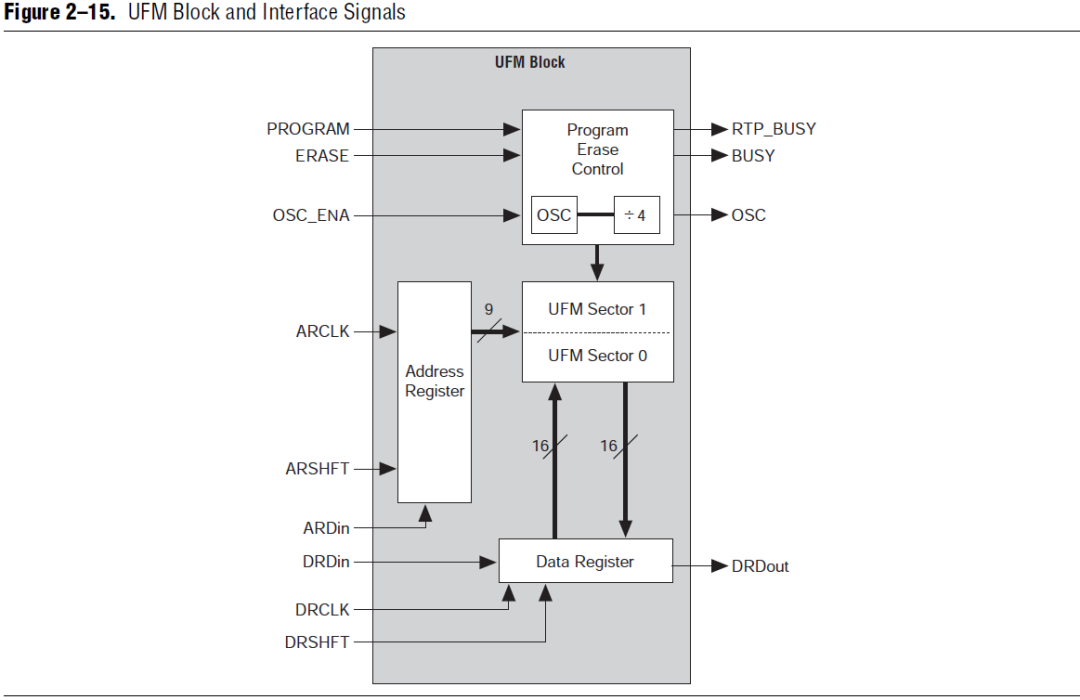

MAX II系列CPLD的UFM(user flash memory)具有振荡器,且可通过配置使能信号OSC_ENA将其4分频信号OSC引用至内部逻辑阵列。内部晶振误差较大,OSC频率在3.3MHz到5.5MHz之间,且不可通过编程调节频率,可用于精度要求不高的定时程序。

2.内部晶振调用

(1)打开Quartus II,新建verilog文档作为顶层文件

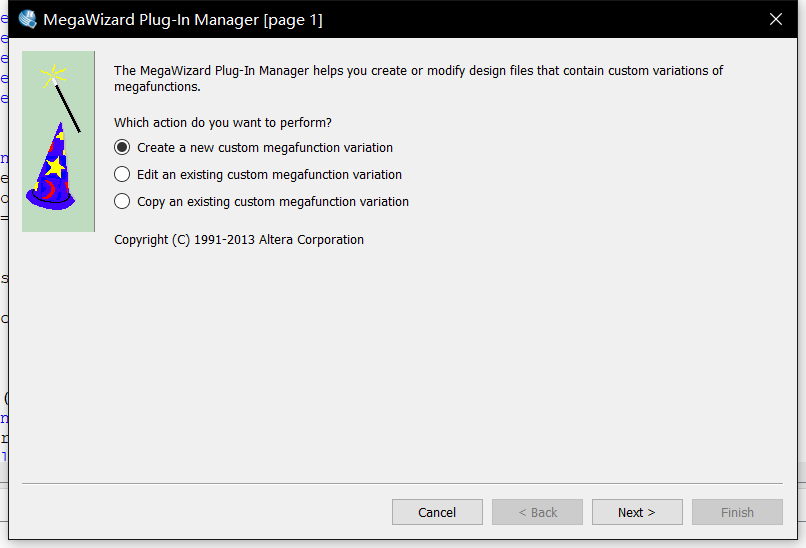

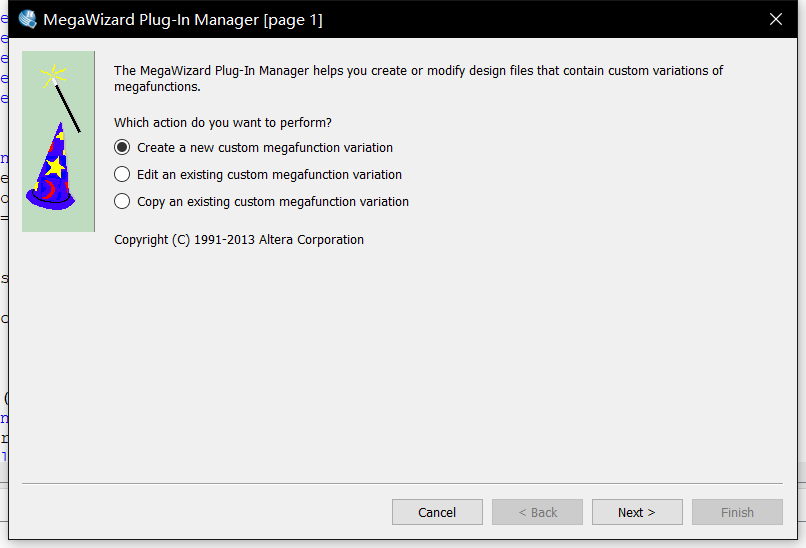

(2)点击菜单Tools->Megawizard Plug-In Manager

选第一个,点next

1.内部晶振参数

MAX II系列CPLD的UFM(user flash memory)具有振荡器,且可通过配置使能信号OSC_ENA将其4分频信号OSC引用至内部逻辑阵列。内部晶振误差较大,OSC频率在3.3MHz到5.5MHz之间,且不可通过编程调节频率,可用于精度要求不高的定时程序。

2.内部晶振调用

(1)打开Quartus II,新建verilog文档作为顶层文件

(2)点击菜单Tools->Megawizard Plug-In Manager

选第一个,点next

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?