DMA

一、 DMA的简单介绍:

DMA( Direct Memory Access ):外设与主存间不经过CPU 而直接进行数据交换的接口。

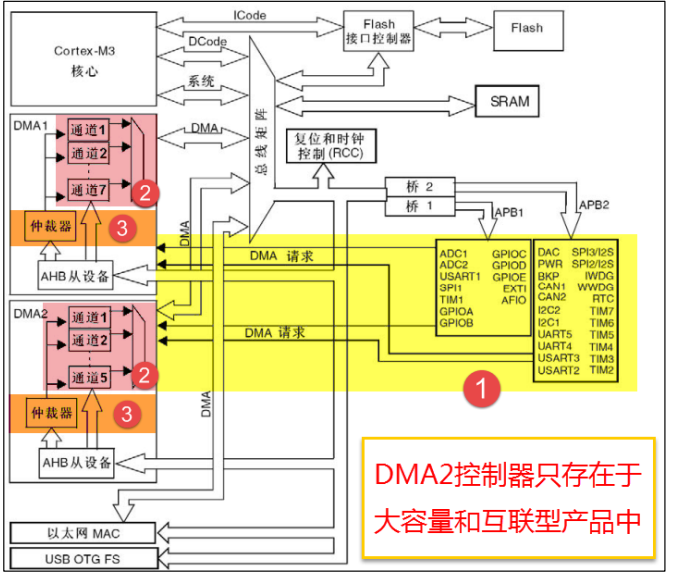

DMA控制器和Cortex™-M3核心共享系统数据总线,执行直接存储器数据传输。当CPU和DMA同时访问相同的目标(RAM或外设)时, DMA请求会暂停CPU访问系统总线达若干个周期,总线仲裁器执行循环调度,以保证CPU至少可以得到一半的系统总线(存储器或外设)带宽。

DMA支持从外设(ADC SPI I2C USART 等)到存储器(片内SRAM 外部存储器 片内FLASH 等)、存储器到外设、存储器到存储器传输的三种传输模式;

DMA 控制器独立于内核 ,控制器框图:

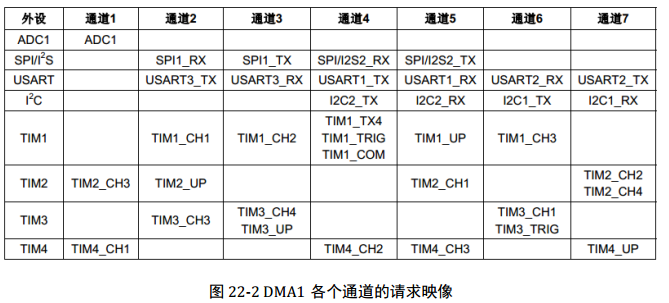

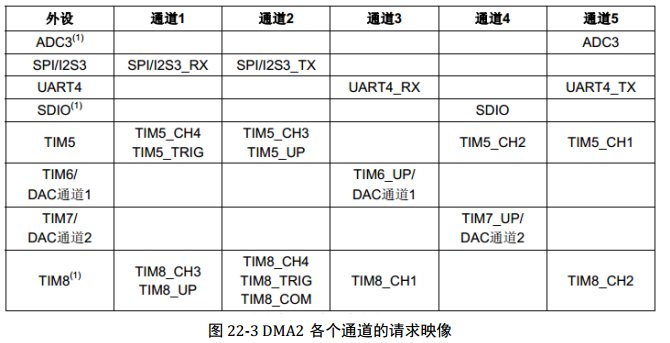

MDA 有两个DMA控制器 DMA1 和DMA2,其中DMA1有7个通道,DMA2 有5个通道.

DMA 请求

DMA 通道

每个通道可以接收多个外设的请求,但是同一时间只能接收一个,不能同时接收多个。- 仲裁器

在收到多个请求时管理响应的先后顺序;这个过程分为两个阶段:

第一阶段:通过设置寄存器,有4个优先级:非常高、 高、 中、 低

第二阶段:在硬件上 当多个请求的优先级相同时,通过判断通道编号越小优先级越高

DMA1 的优先级比 DMA2 要高

二、DMA 寄存器

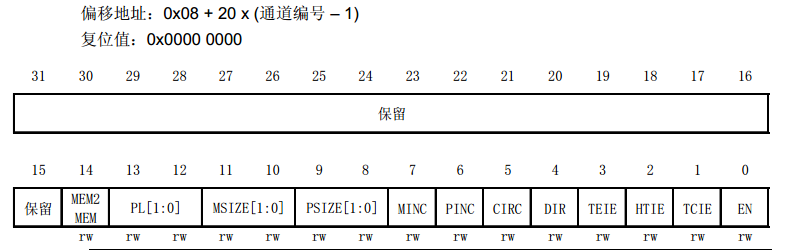

- 配置方向 DIR

存储器 <—-> 外设 :DMA_CCR 位 4 0:外设到存储器,1:存储器到外设

存储器<—–> 存储器:DMA_CCR 位 14:MEM2MEM 置1 启动M2M模式 - 配置数据宽度(size)和增量模式

外设数据宽度 : PSIZE[1:0] 可以设置为 8 16 32

存储器数据宽度 : MSIZE[1:0] 可以设置为 8 16 32

外设增量模式 : PINC

存储器增量模式: MINC - 传输完成模式

- 一次传输: 依次传输完成后 需要再次配置寄存器 CIRC 0

- 循环传输:一次传输完成后恢复第一次传输的配置 CIRC 1

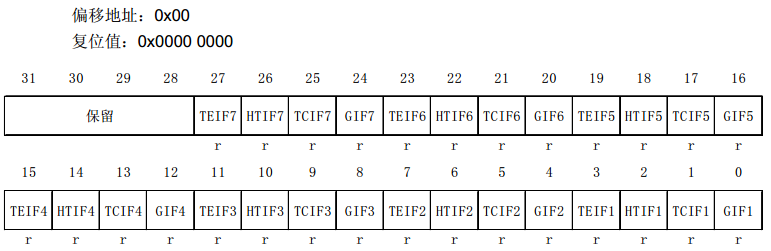

DMA中断状态寄存器(MDA_ISR)

X(1,2,3,….,7)

TEIFx(transfer error flag) : 传输错误标志位 1 有错误 0 没有错误

HTIFx(half transfer flag) : 半传送标志位

TCIFx(transfer complete flag): 传送完成标志位

GIFx (global interrupt flag) : 全局中断标志位

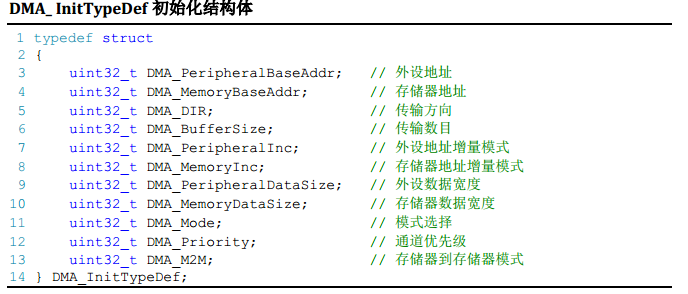

三、DMA库

Stm32F10x

1249

1249

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?