参考教材见博客中第一章内容。本课程知识点多,遇到生涩的不要害怕,先跳过去,回头就能看懂。需要整合才能体系化进行更好的复习。部分字可能打错,多多包涵。

2.1 16位微处理器编程结构

2.1.1 微型计算机基本结构

2.1.2 8086/8088 CPU的编程结构

2.3 8086/8088 CPU引脚功能

2.3.1 引脚信号和功能

2.3.2 8086/8088 构成的最大/最小系统

2.3.3 俩的主要功能

2.1 16位微处理器编程结构

2.1.1微型计算机基本结构

1.五大部件:运算器、控制器、存储器、I/O设备和系统总线

2.微处理器(CPU):芯片包含运算器、控制器与内部寄存器

3.程序:具有一定功能的指令的有序集合

4.指令:人向计算机发出、能为计算机识别的命令

5.指令执行

一般过程:取指令--指令译码--读取操作数--执行指令--存放结果

需要部件:取指部件、分析部件、执行部件

6.操作数:规定指令中数字运算的量(指出所需数据的来源)

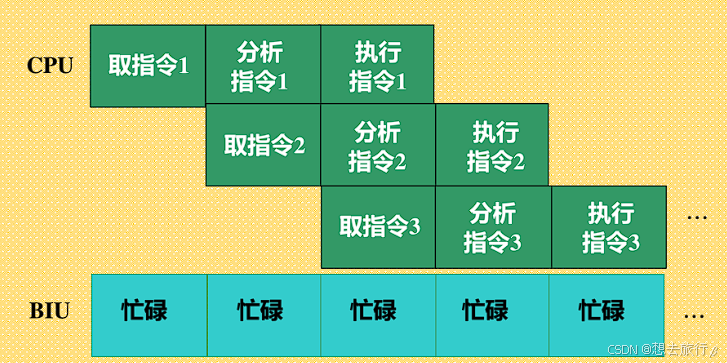

7.顺序执行方式

部件交替工作,顺序完成指令

只在取指令时BUS忙,可见执行与访问存储器分割

8.并行流水线方式

部件并行工作(我们发现串行中是BUS,而没有BIU的概念;即BIU是为并行流水线而存在的)

执行、分析、取并行进行

或者说指令1、2、3…并行进行

2.1.2 8086/8088 CPU的编程结构

9.8086/8088 CPU特点

8088,准16位(内部总线16,外部8,一个总线周期吞吐1 Byte),指令队列4字节

8086,真16(内外16,一总线周期1 Word),指令队列6字节

并行流水线工作 -- 指令预取队列(CPU中BIU中的结构)

内存空间分段管理 -- 地址段存储器(存储器寻址,参考14个寄存器篇)-- 20条地址总线 -- 1MB寻址空间

支持多处理器系统(工作模式,并行产物之一)

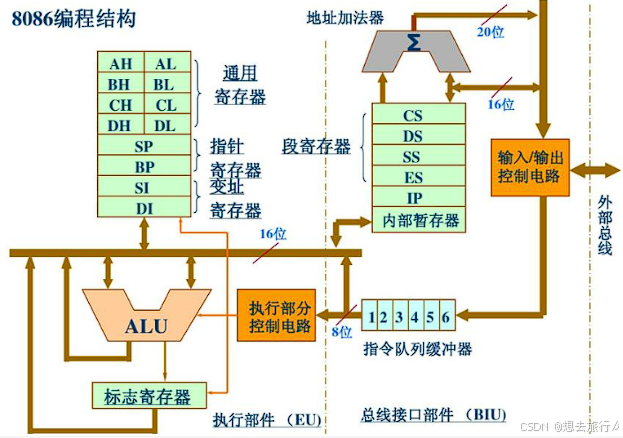

10.BIU与EU

指令流水线结构 -- 访问存储器(取指令)与执行指令分开 -- 对应为BIU(总线接口单元)&EU(执行单元)

BIU:CPU与I/O设备的接口,负责与存储器、IO接口进行数据传输(执行所有外部总线周期)

11.BIU取指令、预取指令(逻辑地址、物理地址)

取指令:逻辑地址CS:IP -- 20位物理地址(CS*16+IP)-- 对应存储单元取指令 -- 存储于指令队列

预取指令: 指令队列有2/1个空字节 -- BIU自动取指令

12.BIU配合EU执行指令、存取操作数和运算结果

EU --提供地址和数据-- BIU --进入外部总线周期-- 访问存储器、IO端口 -- 存取data

13.BIU空闲

指令队列满 and EU无总线访问请求 -- 空闲状态

14.BIU清除队列

EU执行转移 or 子程序调用 or 中断 -- 预取指令失去作用 -- BIU清除队列 -- 得新地址 -- 取与预取指令

15.BIU组成

如图段寄存器、地址指针寄存器、20位地址加法器、指令队列(8088 4Byte 8086 6Byte)、输入输出控制电路

EU:执行全部指令;为BIU提供数据和地址信息,管理部分寄存器(通用、标志),不与外部直接接触。

16.EU组成

ALU(算术逻辑单元)、

数据暂存寄存器(协助ALU,暂存参加运算的数据)、

标志寄存器(FR、FLAG)、

寄存器组(8个)、

执行控制部件(指令队列取指令并执行,向各部件发出控制指令,完成执行指令功能,中枢)

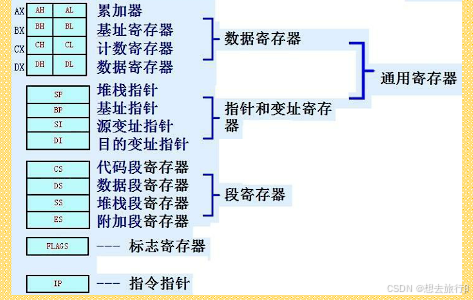

17.14个寄存器(4+4+4+1+1)

具体功能推荐到实验中探究

SI、DI:一般与DS联用,确定数据段中一存储单元地址

SP:栈顶偏移地址

BP:堆栈中基地址

SP、BP:均可与SS联用,……

在串操作指令中,原串操作数必须用SI提供偏移量,目的串操作数必须用DI提供偏移量。???

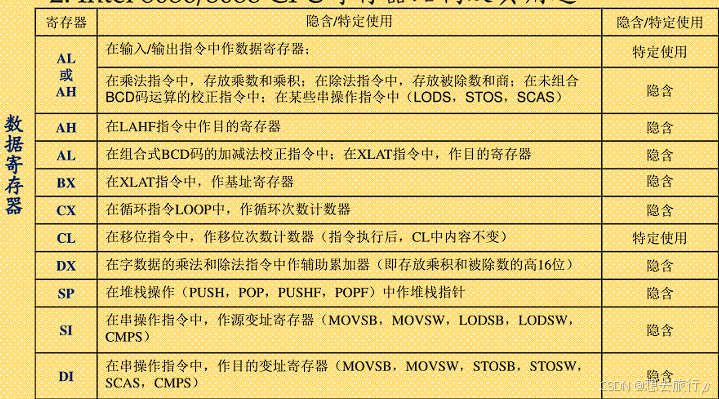

特殊用途

18.段寄存器(数据寄存器与指针和变址寄存器省略不讲)

8088 -- 存储器分段 -- 1MB分为 -- 若干逻辑段

段寄存器 -- 段基址 -- 偏移量(存储单元地址与段基址间距离)

代码段 CS : IP

数据段 DS:SI

堆栈段 SS:SP

附加段 ES:DI

19.源串???

当前源串所在段的基地址 -- DS,ES -- 目标串所在段的基地址

20.段寄存器使用约定

21.物理地址/逻辑地址(具体含义参考实际操作)

物理地址:段地址*16+偏移量(取指令时,CS*16 + IP)

逻辑地址:段地址:偏移量 (CS:IP)

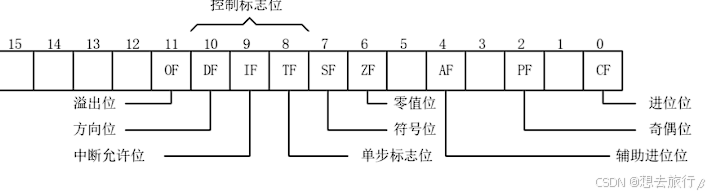

22.标志寄存器(FLAGS REGISTER)(P21)

又称程序状态字(PSW)寄存器

9个标志位 -- 状态标志(CF、PF、AF、ZF、SF、OF)-- 控制标志(TF、IF、DF)

具体标志位含义参考书上内容,标志位的1/0有其符号表达

OF需注意:产生溢出只可能在同号数+ or 异号数- 情况发生

且判断OF是否为1,最好用十进制进行计算(二进制补码计算复杂)

23.存储器组成

存储器容量:二级制信息容量 = 字数*字长

1存储单元 -- 1Byte -- 存储器字节编址

8086/8088 CPU 20根地址线 -- 1MB寻址能力 -- 00000H~0FFFFFH

字(Word) -- 低8位低地址(高8高地址) -- 低地址做字单元的地址

24.存储器分段结构

原因 -- 内部数据通路、ALU、Registers均为16位,不能直接寻址1M字节地址

逻辑段 -- 最大容量64KB(16位偏移量)

段 -- 物理存储器 -- 段基址 -- 16的整数倍

逻辑段间 -- 允许 -- 邻接、间隔、部分重叠、完全重叠 -- 自由

程序运行时,只允许4个当前段 -- 代码、数据、堆栈、附加段 -- 64KB代码、64KB堆栈和128KB数据

25.I/O

8086系统 -- I/O接口电路 -- 外设

I/O接口 -- 几个端口 -- 端口地址

端口 -- I/O接口电路内容的一个或一组寄存器???

8086CPU -- 地址总线低16位 -- 8位I/O端口寻址线(可访问64K个(65535个)8位I/O端口)

(寻址 -- 20根地址总线,且I/O端口可扩展到64KB个地址端口)

26.堆栈

定义 -- 端固定的数据存储区

先进后出 -- 栈底、栈顶、入栈、出栈 -- 栈顶元 -- 存取字数据

作用 -- 暂存数据、现场保护 -- 适用过程调用和中断处理场景

对应指令PUSH、POP

2.3 8086/8088 CPU引脚功能

引脚详细解释省略,自己查询,懒得查点下面

8086引脚图及功能 - 8086CPU引脚图及功能_8086CPU组成部分 - 电子发烧友网

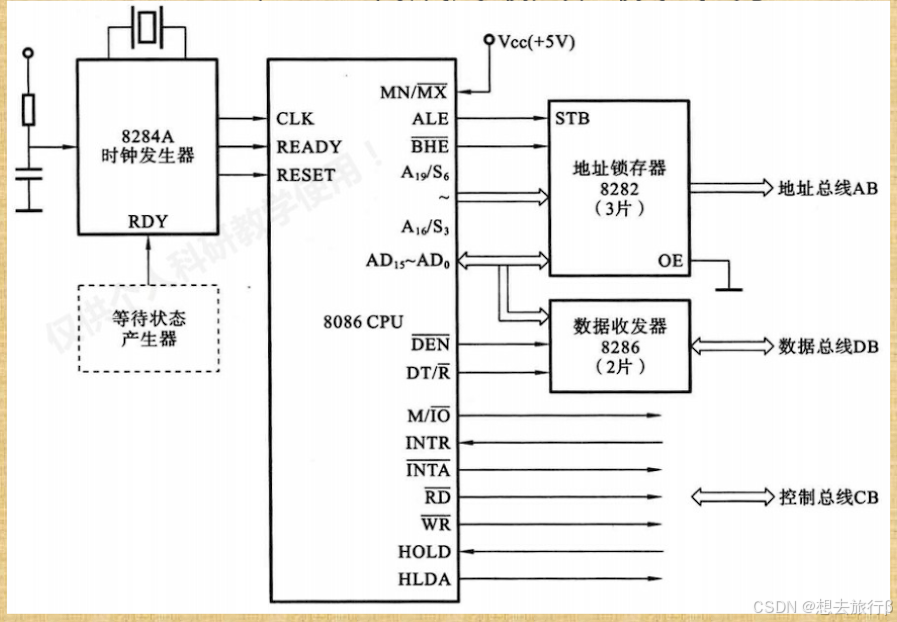

1.最小模式/最大模式

最小模式:系统中只有一个8086/8088 MCU,所有总线控制信号都直接由8086/8088产生

最大模式:两个或多个MCU,主处理器、协处理器

协处理器 -- 一般两个 -- 8087(数值运算协处理器) and 8089(输入/输出协处理器)

8087 -- 数值运算

8089 -- 带有一套专用于输入/输出操作的指令系统

2.总线周期

启动一个总线周期 -- 8086/8088 CPU 与 存储器或I/O端口交换数据

数据传送方向 -- “读”/“写”总线周期

基本总线周期 -由组成- 4个时钟周期 -- T1、T2、T3、T4

时钟周期 -- CPU的基本时间计量单位 -- 由CPU主频决定(8086 5MHz主频 -- 1个时钟周期200ns) -- 一个T状态

T1状态 -- CPU给出RW的存储单元地址 or I/O端口地址 -- 地址总线

“读”总线周期 -- T2 浮空(CPU输出地址的写方式 -转变- 输入数据的读方式 -- 缓冲) -- T3、T4CPU从总线接收数据

“写”总线周期 -- T2~T4 CPU把数据送到总线上 -- 写入存储单元 or I/O端口

3.空闲状态的总线周期(空闲周期)

一个总线周期后不立即执行下一个(CPU不需访问存储器 or I/O端口 ; 指令队列满,不需到内存中读指令)

此时的总线:

高4位CPU仍驱动前一个总线周期的状态信息;

低16位:若前一个周期为写周期,继续驱动数据信息;读周期,浮空

空闲状态,CPU对总线继续空操作,CPU内部仍进行有效操作

3.等待状态的总线周期

T3结束前,CPU测试READY信号线 -- 若READY = H,数据准备好,可以进入T4

--若READY = L,数据没准备好,T3后插入1个或多个等待周期Tw

检测到READY,(脱离Tw)进入T4

设计目的:延长总线周期,允许系统使用低速的存储器芯片

4.引脚信号与功能:

8086:20地址线 16数据线

8088:20 , 8

控制线、状态线、电源线和地线

4.1 电源线和地线

Vcc(pin 40):输入,接+-10% +5V电源

GND(pin 1 ,20):均应接地

4.2 地址/数据(状态)引脚

AD15~AD0(pin2~16,39):时分复用,传输地址单向输出,传输数据输入或输出;时序细节此处略

A19/S6 ~ A16/S3(Address/Status)(pin 35~38):书P35

4.3控制引脚:

NMI(pin 17)

INTR(pin 18)

CLK (pin19)

Reset(pin 21)

Ready(Pin22)

/TEST(Pin23)

/RD(pin32)

/BHE/S7(pin34)

MN//MX(pin33)

5.最小工作模式

MN//MX = +5V

外接15MHz晶振 -- 8284A时钟发生/驱动器三分频 -- CPU系统时钟

8284A也可产生 Ready与Reset

8282 -- 8位地址锁存器

8086 -- 20位总线 + /BHE信号??? -- 3片8282地址所存

8286三态输出的8位数据总线收发器 -- 增加驱动能力

8086 -- 2片;8088 -- 1片

5.1最小方式下,引脚功能

/INTA(pin24)

ALE(pin25)

/DEN(pin26)

DT//R(pin27)

M//IO(pin28)

/WR(Pin29)

HOLD(Pin31)

HLDA(Pin30)

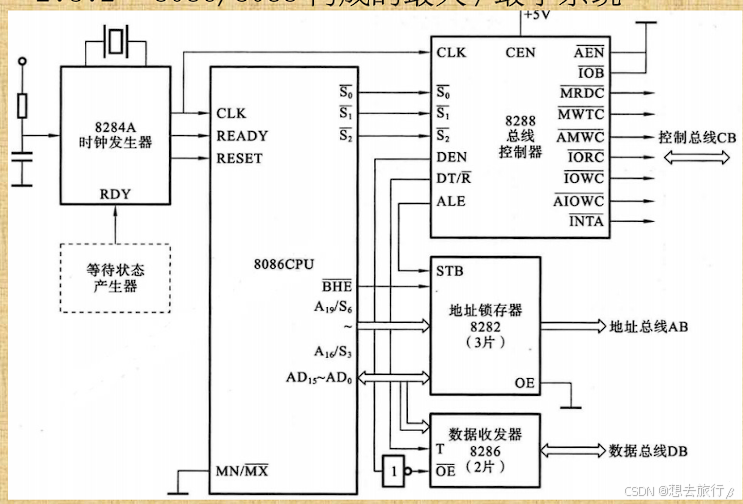

6.最大工作方式

MN//MX为低电平

8288总线控制器 -- 协调主处理器和协处理器的工作

6.1引脚

QS1,QS0(pin24,25)

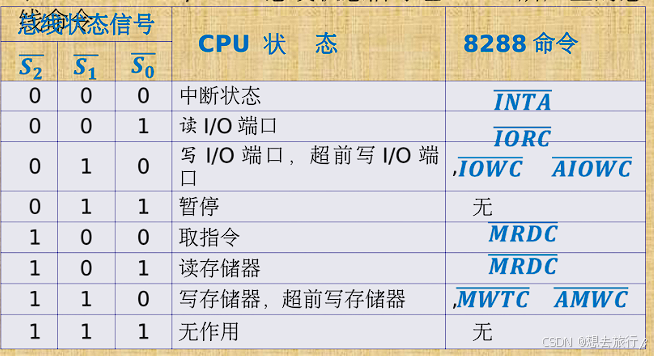

/S2、/S1、/S0(Pin26、27、28)

/LOCK(Pin29)

/RQ/GT1、/RQ/GT0(Pin30、31)

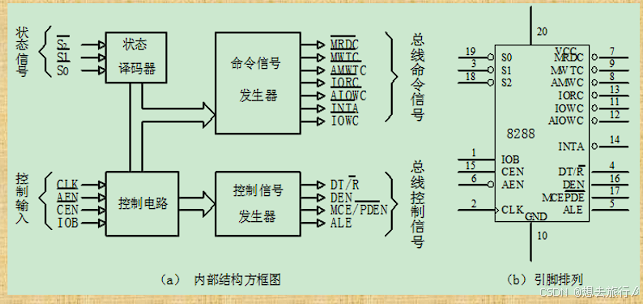

6.2 8288总线控制器

各命令信号与控制输入参考书P47

/AEN由总线仲裁器8289输入

MCE//PDEN?8259A?

6.3 总线仲裁器8289

8089,8087(略,此处没看PPT)

8089配合8288确定每一时刻总线使用权

7.时序

时序 -- 信号高低电平(有效或无效)变化及相互间的时间关系

8.指令周期、总线周期与时钟周期

指令周期 -- 执行一条指令所需要的时间 -- 包括:取指令、分析指令、对操作数寻址、执行指令、保存操作结果

1个指令周期 -- 若干个总线周期

不同指令周期 -- 不同长度

总线周期 (机器周期) -- BIU通过总线与存储器或I/O接口进行一次数据传输所需时间

1个总线周期 -- 4个时钟周期

时钟周期(T状态) -- CPU处理动作的最小单位 -- 时间长度 = 主频倒数

9.8086总线时序

CPU操作 -- 指令译码输出的电位 -- 外面输入的时钟信号联合作用 -- 产生各个命令控制 下进行

包括:系统复位和启动、存储器读/写操作、IO设备输入输出周期、中断响应操作、空转周期

10.系统复位和启动

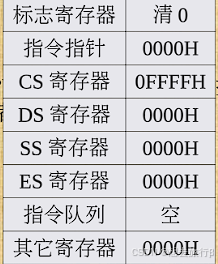

RESET引脚 -- 上升沿 -- 初始化状态 -- 直到RESET变低

内部引脚RESET -- 外部引脚RESET有效后的时钟上升沿有效

三态输出线(很多,记不下来),还有几条非三态线 -- 复位 -- 无效状态(不浮空)

8086/8088 -- RESET至少有4个时钟周期高电平(初次加电启动,至少50us高电平)

标志寄存器清0 -- 启动时需要指令设置有关标志

RESET高到低 --复位逻辑电路-- 7个时钟周期后 -- CPU启动,恢复正常工作 -- 0FFFF0H处执行程序

11.读总线周期(略)

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?