这里写目录标题

- cache基本原理

- 1. cache的功能

- 2. cache的基本原理

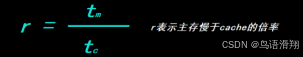

- cache的命中率h

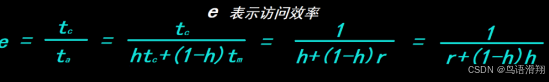

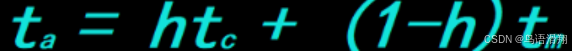

- cache/主存系统的平均访问时间ta

- cache的访问效率e

- 例题

cache基本原理

1. cache的功能

cache 是一种高速缓冲存储器,是为了解决CPU 和主存之间速度不匹配而采用的一项重要技术。其原理基于程序运行中具有的空间局部性和时间局部性特征。

cache是介于CPU和主存之间的小容量存储器,但存取速度比主存快,容量远小于主存。cache能高速地向CPU提供指令和数据,从而加快了程序的执行速度。从功能上看,它是主存的缓冲存储器,由高速的SRAM 组成。为追求高速,包括管理在内的全部功能出硬件实现,因而对程序员是透明的。

2. cache的基本原理

cache除包含SRAM外,还要有控制逻辑。若cache在CPU芯片外,它的控制逻辑一般与主存控制逻辑合成在一起,称为主存/chace控制器;若cache在CPU内,则由CPU提供它的控制逻辑。

CPU与cache之间的数据交换是以字为单位,而cache与主存之间的数据交换是以块为单位。一个块由若干字组成,是定长的。当CPU读取内存中一个字时,便发出此字的内存地址到cache和主存。此时cache控制逻辑依据地址判断此字当前是否在cache中,若是,则 cache 命中,此字立即传送给 CPU;若非,则 cache 缺失(未命中),用主存读周期把此字从主存读出送到CPU,与此同时,把含有这个字的整个数据块从主存读出送到 cache 中。

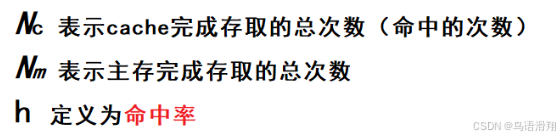

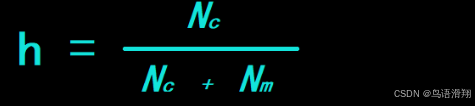

cache的命中率h

从 CPU来看,增加cache的目的,就是在性能上使主存的平均读出时间尽可能接近cache的读出时间。为了达到这个目的,在所有的存储器访问中由cache 满足 CPU 需要的部分应占很高的比例,即cache的命中率应接近于1。由于程序访问的局部性,实现这个目标是可能的。

cache命中率=cache 完成存取的总次数/(cache 完成存取的总次数+主存完成存取的总次数)

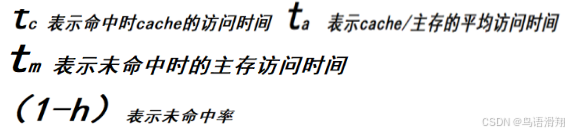

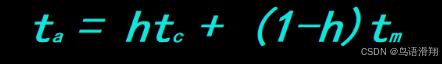

cache/主存系统的平均访问时间ta

cache的访问效率e

例题

1,CPU 执行一段程序时,cache 完成存取的次数为1900次,主存完成存取的次数为100次,已知cache存取周期为50ns,主存存取周期为250ns,求cache/主存系统的效率和平均访问时间。

解:

cache命中率=cache 完成存取的总次数/(cache 完成存取的总次数+主存完成存取的总次数)

有已知的命中率h为:

h=1900(1900+100)=0.95

r=250ns/50ns=5

e=1/(r+(1-r)h)=1/(5+(1-5)0.95)=83.3% (本人认为这似乎便麻烦了,没有直接算来的快)

ta=tc/e=50ns/0.833=60ns

直接算:

ta=htc+(1-h)tm=0.95x50ns+(1-0.95)x250ns=60ns

e=tc/ta=50ns/60ns=83.3%

这多简单,还省事。

2,已知cache 存储周期40ns,主存存储周期200ns,cache/主存系统平均访问时间为50ns,求 cache的命中率是多少?

提示:

利用此公式倒推即可得出命中率,剩下的就由自己算吧!~

感兴趣的宝子给点个👍支持一下吧😊😊😊

1862

1862

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?