第一章 计算机组成与结构

- 1.计算机硬件系统

- 1.1运算器

- 1.2控制器

- 2.数据表示

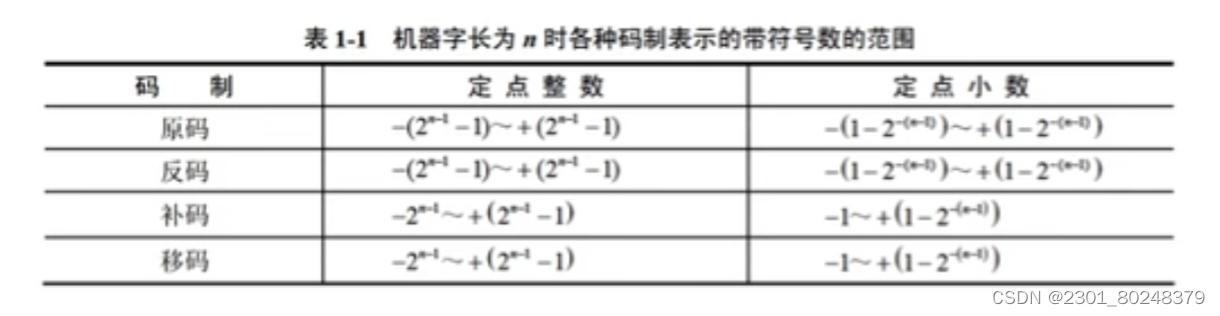

- 2.1原码,反码,补码,移码

- 2.2浮点数

- 3.寻址

- 4.校验码

- 5.RISC和CISC

- 6.指令流水线

- 7.存储器

- 8.高速缓存

- 9.中断

- 10.输入输出(I/O)控制方式

- 11.总线

- 12.加密技术与认证技术

- 12.1加密技术

- 12.2摘要(防止篡改)

- 12.3数字签名(防止假冒)

- 12.4数字证书

- 12.5加密算法

- 13.可靠性公式

1.计算机硬件系统

5部分:运算器,控制器(CPU),存储器,输入设备,输出设备

CPU负责获取程序指令,对指令进行译码并加以执行

CPU的功能:程序控制,操作控制,时间控制,数据处理

1.1运算器

算数逻辑单元(ALU),累加寄存器(AC),

数据缓冲寄存器(DR),状态条件寄存器(PSW)

1.2控制器

计算机指令包括:操作码,地址码

保证程序的正确执行,处理异常事件

指令寄存器(IR),程序计数器(PC),

地址寄存器(AR),指令译码器(ID)

程序计数器存指令地址

2.数据表示

数值在计算机中表示的形式称为机器数,采用二进制

0的原码:00000000或10000000

2.1原码,反码,补码,移码

正数的原码,反码,补码相同

负数:

1.原码:最高位为符号位:0正1负

2.反码:负数原码按位取反

3.补码:反码的末位+1

4.移码:补码符号位取反

5.补码的补码是原码

采用补码可以简化计算机运算部件的设计

2.2浮点数

N = 2ᴱ * F

N:二进制数 E:阶码 F:尾数

小阶对大阶,浮点数向右移

浮点数所能表示的数值范围是由阶码决定的,数值的精度由尾数决定

规格化:尾数的区间在[0.5,1]

浮点数的阶码用移码表示®,尾数用补码表示(M),都包括阶符

最大正数:+(1-2⁻ᴹ⁺¹) * 2⁽²^⁽ᴿ⁻¹⁾⁻¹⁾

最小负数:-1 * 2⁽²^⁽ᴿ⁻¹⁾⁻¹⁾

IEEE754阶码用移码,尾数用原码

小数点不需要占一个存储位

定点数的补码和移码表示2ⁿ个数,原码和反码表示2ⁿ-1个数

3.寻址

1.立即寻址:操作数就包含在指令中(最快)①

2.直接寻址:操作数存放在内存单元中,指令中直接给出操作数所在存储单元的地址③

3.寄存器寻址:操作数存放在某一寄存器中,指令中给出存放操作数的寄存器名②

4.寄存器间接寻址:操作数存放在内存单元中,操作数所在存储单元的地址在某个寄存器中④

5.间接寻址:指令中给出操作数地址的地址⑤

指令系统中采用不同的寻址方式目的:扩大寻址空间并提高编程灵活性

4.校验码

1.奇偶校验码:在编码中增加一位校验位,看编码中1的个数,为奇数是奇校验,为偶数是偶校验,从而使码距变为2。只能检测奇数个数据位出错(出错位共有奇数个),只能检错不能纠错

码距:一个编码系统中任意两个合法编码中至少有几位二进制数不同(开始有1个,经过校验有2个)

码距=2有检错能力

码距>=3有纠错能力

常用的有3种:水平奇偶校验码,垂直奇偶校验码,水平垂直校验码

2.海明码:利用奇偶性来检错和纠错的校验方法,插入k个校验位

数据位n位,校验位k位

2ᴷ-1 >= n+k

3.循环冗余校验码:可以检错不能纠错,k个数据位产生r个校验位,其编码长度为k+r

求CRC编码,采用模2用算

5.RISC和CISC

CISC支持流水线技术但不合适

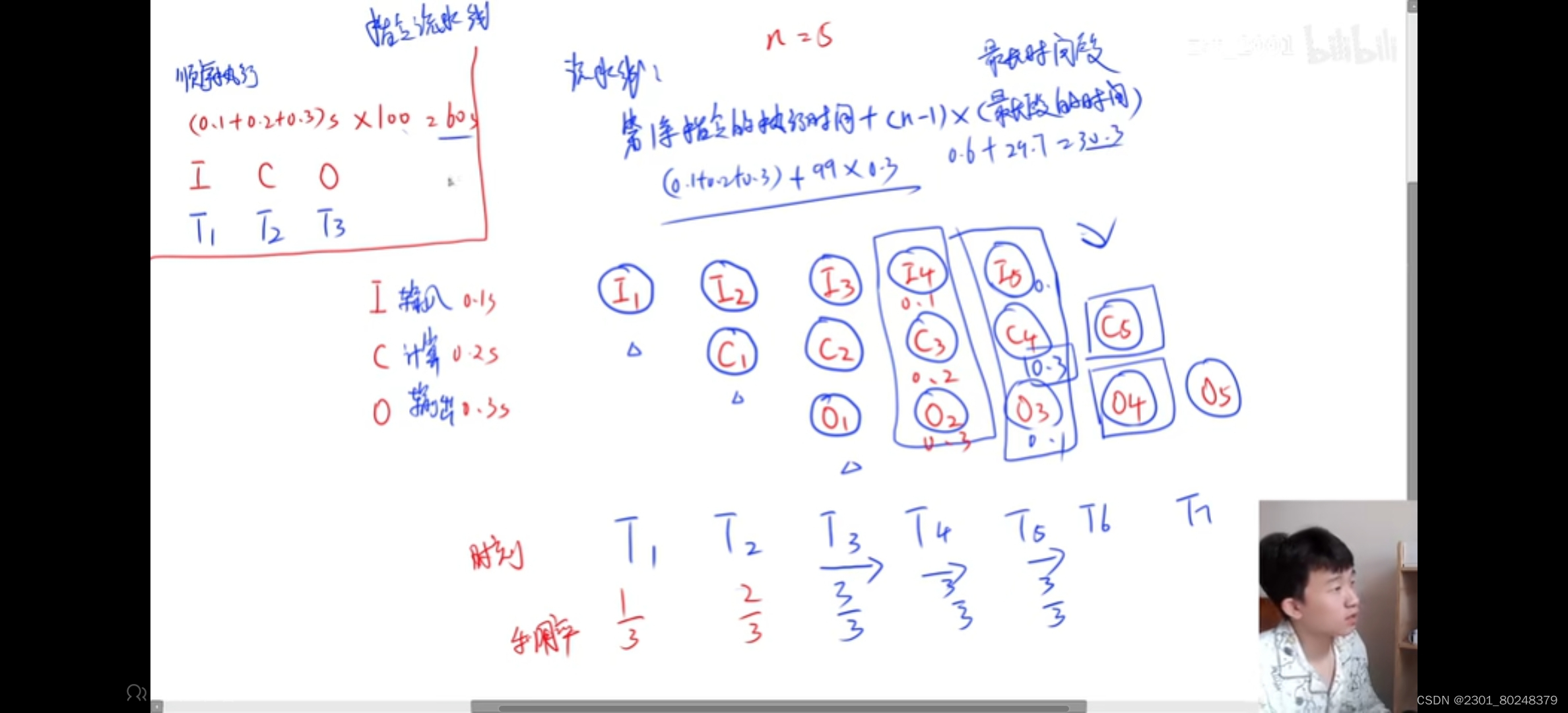

6.指令流水线

第一条指令的执行时间 + (n-1)*最长段时间

操作周期:最长时间段

吞吐率:最长时间的倒数

n条吞吐率=n/(第一条指令的执行时间 + (n-1)*最长段时间)

7.存储器

静态随机存储器(SRAM)(构成Cache)

动态随机存储器(DRAM)周期性刷新(构成主存)

Chache高速缓冲存储器

1.按存储器所在位置:内存(主存),外存(辅存)

2.按存储器工作方式:读/写存储器(RAM),只读存储器(ROM)

3.按访问方式:按地址访问,按内容访问

4.按寻址方式:随机存储器,顺序存储器,直接存储器

相联存储器(按内容访问)

虚拟存储器由主存和辅存构成

CPU空间局部性:访问完后可能会访问相邻的

CPU时间局部性:访问完后可能会再次访问

8.高速缓存

用来存放当前最活跃的程序和数据,速度一般比主存快5-10倍,对程序员来说是透明的

Cache,位于CPU和内存之间

Cache存储器存放主存的部分拷贝信息

控制部分的功能:判断CPU要访问的信息是否存在Cache存储器中,若存在就命中,若不存在就没有命中,未命中时,按照替换原则决定主存的一块信息放到Cache存储器的哪一块里

替换算法:使Cache获得尽可能高的命中率

随机替换算法,先进先出算法,近期最少使用算法,优化替换算法

Cache容量越大,命中率越高,随着容量的增加,命中率逐渐接近吧100%

高速缓存中的地址映像方法:

CPU工作时,送出的是主存单元的地址,而应从Cache存储器中读/写信息,将主存地址转换成Cache存储器地址,称为地址映像

Cache的地址映像:

1.直接映像:主存块与Cache块的对应关系固定(冲突大)

2.全相联映像:允许主存的任一块可以调入Cache存储器的任何一个块的空间中(冲突小)

3.组相联映像(冲突较小)

Cache与主存地址的映射是由硬件完成

9.中断

计算机在执行程序过程中,遇到急需处理的事件时,暂停当前正在运行的程序,转去执行有关程序服务,处理完后自动返回源程序

1.中断的量:提供中断服务程序的入口地址(汇集成中断向量表)

2.中断响应时间:发出中断请求开始,到进入中断服务程序

3.保护现场:返回来执行源程序

10.输入输出(I/O)控制方式

1.程序查询方式

CPU和I/O只能串行工作

CPU需要一直轮寻检查

一次只能读/写一个字(8bit)

2.中断驱动方式

I/O设备通过中断信号主动向CPU报告I/O操作已完成

CPU和I/O并行工作

3.直接存储器方式(DMA)

CPU和I/O并行工作

仅在数据块的开始和结束时才需要CPU干预

由外设直接将数据存入内存

读/写以块为单位

除数为0是异常

CPU在一个总线周期结束时响应DMA

采用DMA传送数据,每个数据占用一个存储周期

11.总线

总线分为数据总线,地址总线,控制总线

PCI:并行内总线

SCSI:并行外总线

12.加密技术与认证技术

窃听(加密),篡改(摘要),假冒和否认(数字证书,数字签名)

12.1加密技术

1.对称加密(私有密钥加密,共享密钥加密):只有一把密钥(加密和解密同一把)

密钥分发有缺陷

①加密解密速度很快

②适合加量大量明文数据

2.非对称加密(公开密钥加密):加密和解密不是同一把,一共有两把密钥,分别是公钥和私钥

公钥只能用私钥解密,私钥只能用公钥解密

不能通过一把推出另一把

用接收方的公钥加密明文,可以实现防止窃听的效果

密钥分发没有缺陷

①加密解密速度很慢

3.混合加密

用接受者的公钥加密(对称密钥加密和对称密钥)

12.2摘要(防止篡改)

将发送的明文经过hash算法后得到摘要,把摘要和明文一起传送,接收方解密明文后同样经过hash算法得到摘要,同之前的摘要相比,一样没有被篡改,反之被篡改

认证处理主动攻击(篡改),加密处理被动攻击(监听)

12.3数字签名(防止假冒)

用发送方的私钥签名,发送方的公钥解密

12.4数字证书

用户向CA机构申请数字证书

将个人信息和公钥发给CA机构

CA机构发给用户数字证书

数字证书用CA的私钥进行签名,公钥解密

得到用户的公钥

公钥加密认证,私钥解密签名

12.5加密算法

1.对称密钥:

DES,3DES,RC-5,IDEA,AES,RCA

AES分组加密

2.非对称密钥:

RSA,ECC,DSA

13.可靠性公式

1.串联系统:R=R₁R₂…Rₓ

2.并联系统:R=1-(1-R₁)(1-R₂)…(1-Rₓ)

被动攻击:流量分析,系统干涉

左乘又除

2137

2137

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?