1 3-8译码器

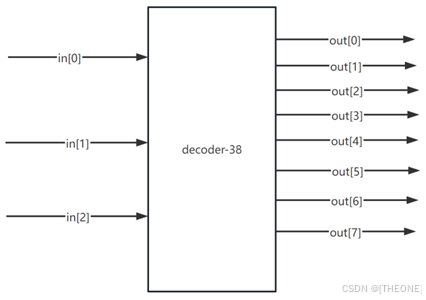

图 3.1 38译码器模块图

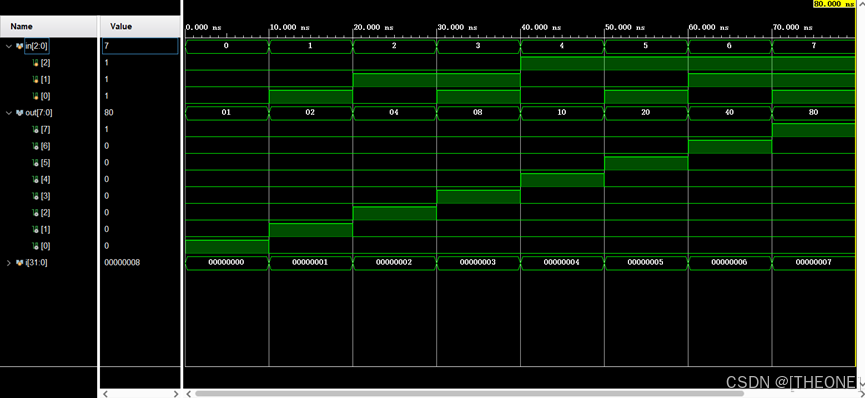

如图3.1所示,为38译码器的电路模块图。38译码器有3线输入,8线输出。3线输入会组成000到111共8个不同的数字,输出对应会有8种状态。表3.1是38译码器的真值表。

表 3.1 38译码器真值表

| 输入 |

输出 |

| in[2] in[1] in[0] |

out[7] out[6] out[5] out[4] out[3] out[2] out[1] out[0] |

| 000 |

0000 0001 |

| 001 |

0000 0010 |

| 010 |

0000 0100 |

| 011 |

0000 1000 |

| 100 |

0001 0000 |

| 101 |

0010 0000 |

| 110 |

0100 0000 |

| 111 |

1000 0000 |

设计代码

`timescale 1ns / 1ps

module decoder_38(

input [2:0] in,

output[7:0] out

);

assign out[0]=(in==3'd0);

assign out[1]=(in==3'd1);

assign out[2]=(in==3'd2);

assign out[3]=(in==3'd3);

assign out[4]=(in==3'd4);

assign out[5]=(in==3'd5);

assign out[6]=(in==3'd6);

assign out[7]=(in==3'd7);

endmodule仿真代码

`timescale 1ns / 1ps

module decoder_38_tb(

);

reg[2:0] in;

wire[7:0]out;

decoder_38 decoder_381(.in(in),.out(out));

integer i=0;

initial begin

#120

for(i=0;i<=7;i=i+1)begin

#10

in=i;

end

end

initial begin

#300

$finish;

end

endmodule

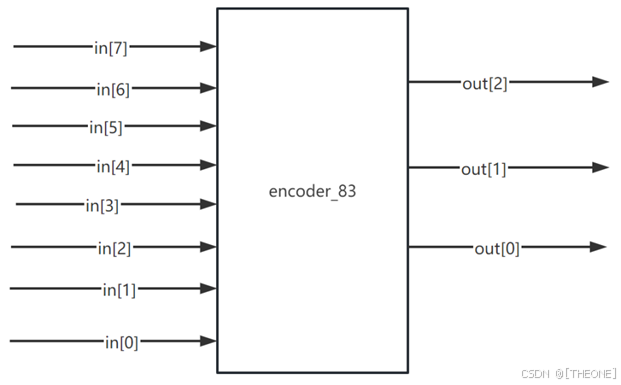

2 带有优先级的83编码器

如图3.2所示,为带优先级的83编码器模块图,83编码器有8线输入,3线输出。某一位为1,则输出对应的数字。应用场景是:根据指令译码后的结果生成ALU模块的操作码alu_op。

表3.2为83编码器的真值表。

图 3.2 83编码器模块图

表 3.2 83编码器真值表

| 输入 |

输出 |

|||||||||

| In[7] |

||||||||||

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?