initial 语句是个不可综合的语句,上电以后只执行一次。

仿真时,时钟信号使用阻塞赋值“=”,其余使用非阻塞赋值“<=”

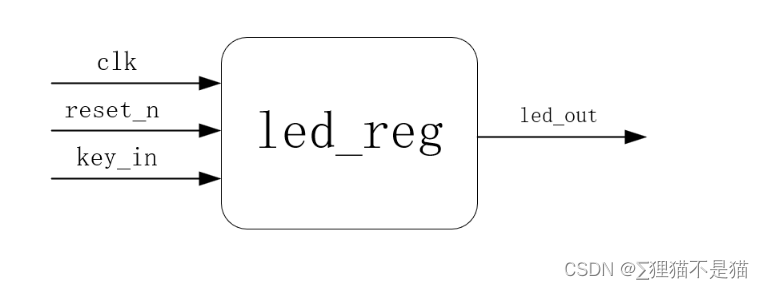

(1)Visio:

(2)同步复位 Verilog实现代码:

module led_reg(clk,reset_n,key_in,led_out);

input clk;

input reset_n;

input key_in;

output reg led_out;

//同步复位

always@(posedge clk)

if(!reset_n)

led_out <= 1'd0;

else

led_out <= ~key_in;

endmodule

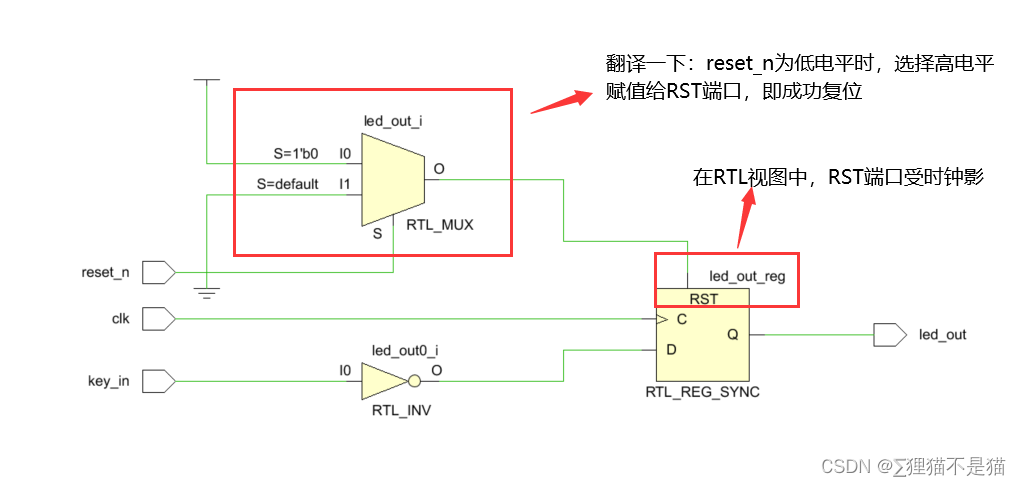

(3)同步复位RTL视图:

(4)更改代码为:

module led_reg(clk,reset_n,key_in,led_out);

input clk;

input reset_n;

input key_in;

output reg led_out;

//同步复位

always@(posedge clk)

if(!reset_n)

led_out <= 1'd1;

else

led_out <= ~key_in;

endmodule

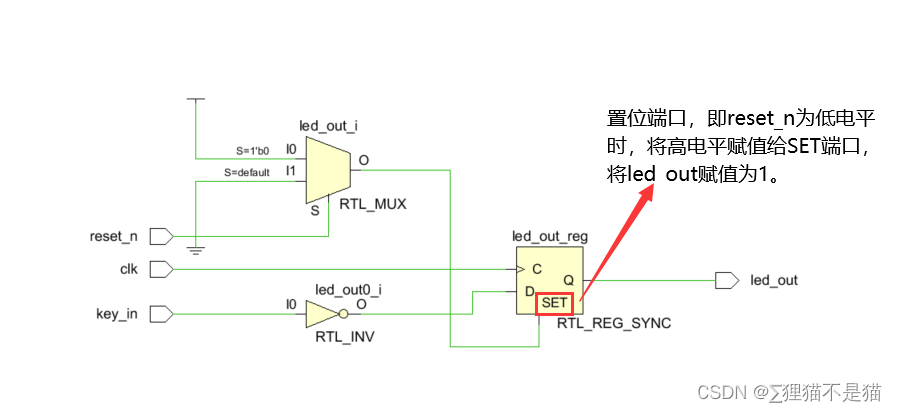

(5)此时RTL视图为:

(6)Verilog文件重新更改为原来代码后,同步复位仿真文件代码:

`timescale 1ns/1ns

module led_reg_tb;

reg clk;

reg reset_n;

reg key_in;

wire led_out;

led_reg led_reg_inst(

.clk(clk),

.reset_n(reset_n),

.key_in(key_in),

.led_out(led_out)

);

initial clk = 1'd0;

always #10 clk = ~clk;

initial begin

reset_n <= 1'd1;

key_in <= 1'd0;

#40;

reset_n <= 1'd0;

#43;

reset_n <= 1'd1;

#21

key_in <= 1'd1;

#13

key_in <= 1'd0;

#1

key_in <= 1'd1;

#1

key_in <= 1'd0;

#1

key_in <= 1'd1;

#1

key_in <= 1'd0;

#1

key_in <= 1'd1;

#1

key_in <= 1'd0;

#45

key_in <= 1'd1;

#1

key_in <= 1'd0;

#2

key_in <= 1'd1;

#1

key_in <= 1'd0;

#1

key_in <= 1'd1;

#1

key_in <= 1'd0;

@(posedge clk)

key_in <= 1'd1;

#30;

$stop;

end

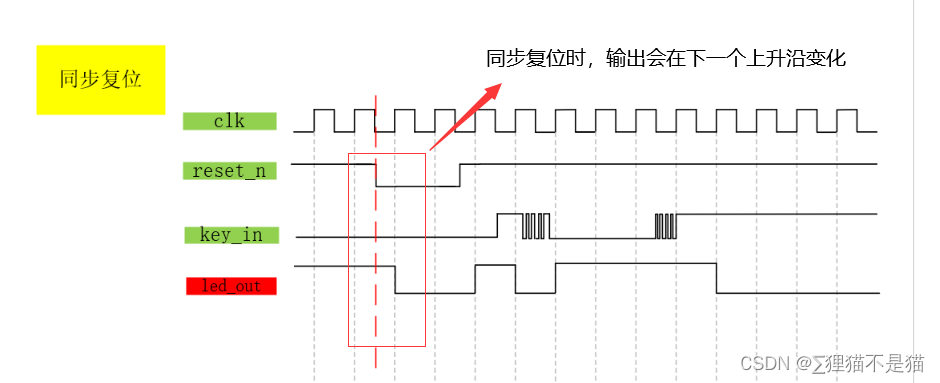

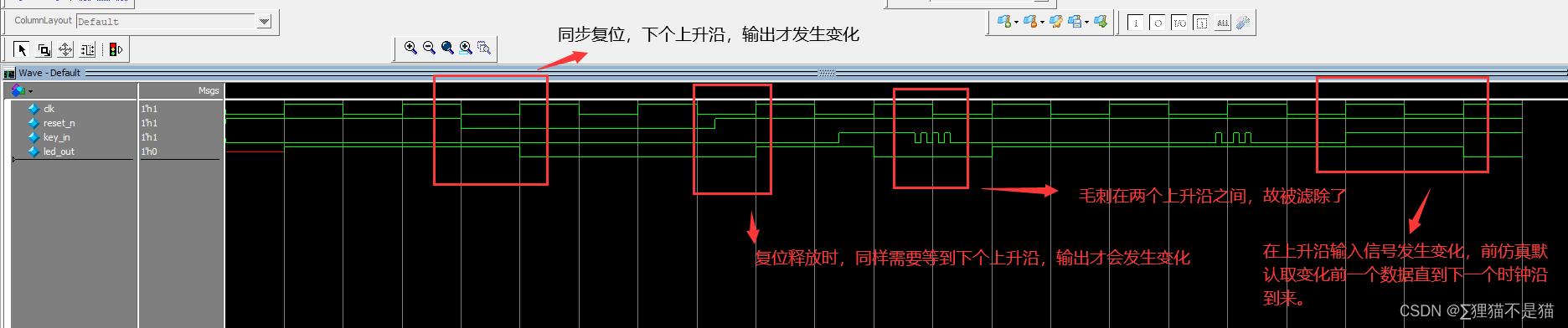

endmodule (7)同步复位仿真波形:

(8)异步复位Verilog代码:

module led_reg(clk,reset_n,key_in,led_out);

input clk;

input reset_n;

input key_in;

output reg led_out;

//异步复位

always@(posedge clk or negedge reset_n)

if(!reset_n)

led_out <= 1'd0;

else

led_out <= ~key_in;

endmodule

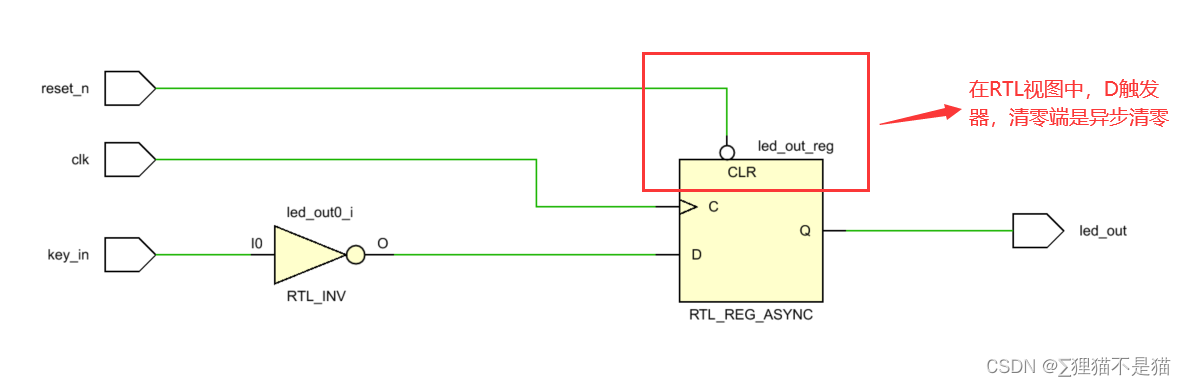

(9)异步复位RTL视图:

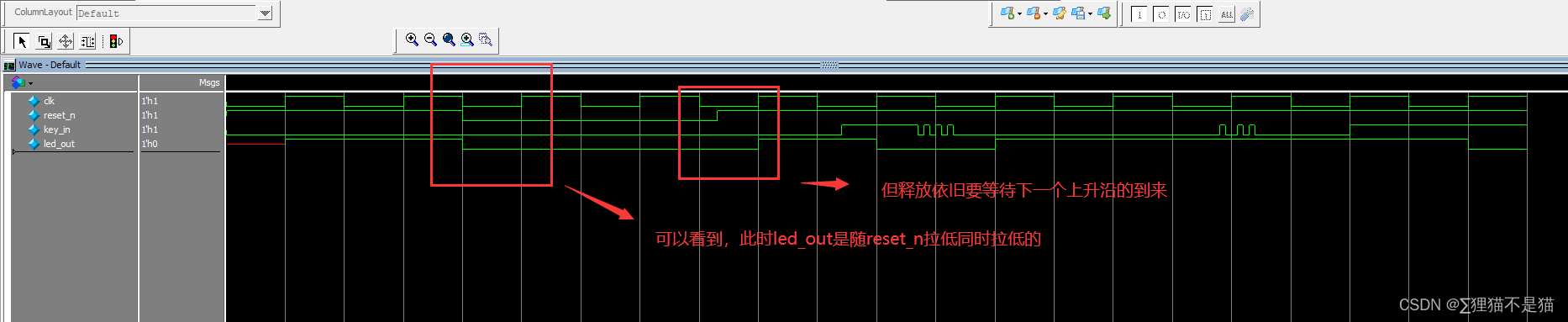

(10)异步复位仿真代码同同步复位一致,仿真波形如下:

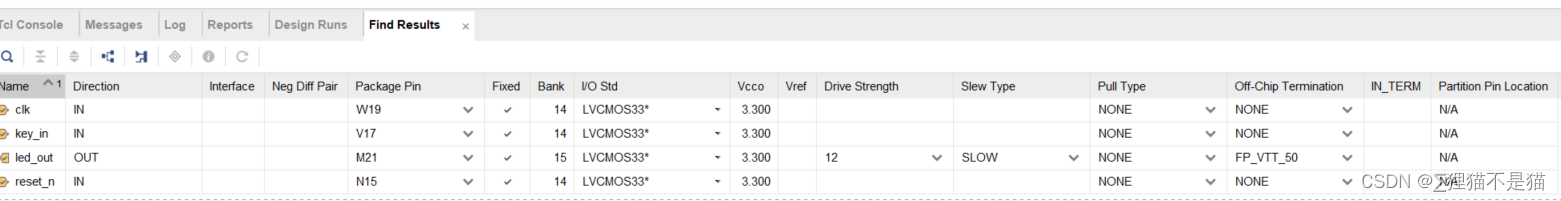

(11)引脚绑定:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?