计算机指令集体系结构之指令

指令由操作码和地址码字段组成。

操作码指明了指令要完成的操作。

长度可以固定:比如RISC(reduced instruction set computer)精简指令集计算机

与之对应的RISC(复杂指令集计算机),其操作码长度不固定。

一般采用拓展操作码技术。

图中指令字长共16位,操作码依次按4位,8位,12位,16位划分。

4位操作码(三地址)共有2^4=16种指令,其中使用了15条,剩下的2^4-14=1条用于8位拓展操作码,8位操作码(二地址)也使用了15条,留下一条区分12位操作码(一地址),直到16位操作码(零地址),此时使用全部的16条,因为本例最大只能操作码拓展全部到16位;。

即结论是拓展操作码中,指令操作码每减少a种,多构成a*2^(一地址的地址码位数)种拓展的下一位操作码。

例子:

1. 假设指令字长为16位,操作数的地址码为6位,指令有零地址,一地址,二地址三种格式。

(1)设操作码固定,而零地址指令由有P种,一地址指令有Q种,则二地址指令最多有多少种?

二地址指令操作码位数:

操作码固定:位数为16-6-6=4;

4位操作码有2^4=16种操作。

二地址指令有16-P-Q种。

(2)采用拓展操作码技术,若二地址指令由X种,零地址指令有Y种,则一地址指令最多有几种?

地址码拓展操作码长度可变,零地址,一地址,二地址操作码位数分别是16位,10位,4,位。

由上述图中的逻辑可知,操作码每减少一种,就可以多2^6种拓展的下个操作码。即二地址操作码每减少一种,多构成2^6种一地址操作码;

一地址操作码每减少一种,多构成2^6种零地址操作码。

二地址指令有X种,一地址指令最多有(2^4-X)*2^6种,(4位使用后剩下的用来区分下一地址操作码);

设一地址指令由M种,零地址指令有((2^4-X)*2^6-M))*2^6=Y种,解出M为(2^4-x)*2^6-Y*2^(-6);

指令操作数可直接寻址范围为2的幂次方,幂次方与地址码位数相同。

操作类型

1. 数据传送:对存储器store写,load读。

2。算术逻辑操作

3.移位:

算术移位:有符号数的移位。

逻辑移位:无符号数的移位。

循环移位:

4.转移:

(1)无条件转移:

JMP X:无条件跳转到X

(2)条件转移:

一些条件码:Z(零标志位),N(负标志位),V(溢出标志位),C(进位标志位),P(奇偶标志位):为偶数时候,P为1;

比如:BRO X(结果溢出,跳转到X)

BRC Y( 结果进位,跳转到Y)

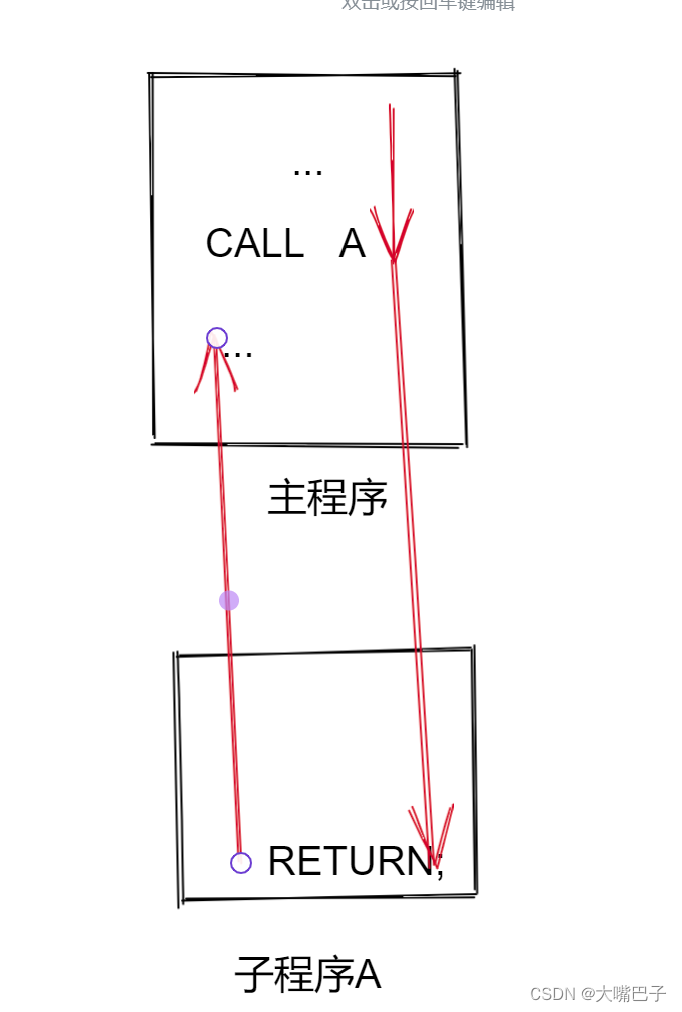

(3)调用与返回

调用

CALL:

转到子程序入口。

RETURN:返回调用程序断点处,

(4)TRAP陷阱与陷阱指令

计算机运行2时候,可能出现意外情况,比如电源断开,除数为0,运算结果溢出等,此时计算机发出陷阱信号,暂停当前程序的执行,转入故障处理程序进行相应的处理。

5.

输入输出

6.其他;

等待,停机等指令。

指令格式

(1)RISC计算机,比如ARM,MIPS,指令长度受到了严格的限制,指令长度必须规整为一个字。

(2)CISC计算机,比如68K,采用允许指令长度拓展解决了固定指令长度问题

设计者

操作码与指令

三地址计算机

operation destination,source1,source2

source1和source2都是源地址,destination是目标地址,即用来存放结果。

双地址计算机

计算

比如a=a+b;

一个地址出现了两次,第一次作为源地址,第二次作为目的地址。

一个地址(即操作数)因为覆写而被破坏。

大多数计算机不能直接访问两个存储单元,而是两个寄存器,或者一个寄存器加一个存储单元。

68K处理器的ADD指令

ADD D0,D1 [ D1]+[D0] ←[D1]

ADD P,D1 [P]+[D1] ← [D1]

ADD D7,P [D7]+[P] ← [P]

单地址计算机

只在指令中有一个操作数,第二个操作数是叫做累加器的寄存器

比如c=a+b

LDA a;将P加载到累加器中。

ADD b;将Q与累加器的内容相加。

STA c; 将累加器的内容加载到c;

零地址计算机

根本没有地址指令

叫做栈计算机,对位于栈顶的数据进行处理

从栈顶取出元素,进行计算,结果入栈。

取元素叫出栈,放元素叫入栈。需要load指令和store指令从存储器读取数据或保存数据到存储器。

计算a+b

PUSH a;a入栈

PUSH b;b入栈。

ADD 栈顶两个元素出栈,然后相加入栈。

POPZ :栈顶数据出栈(结果)

运算的操作命令将栈顶元素出栈(可能不止一个)在运算完成后将其入栈;

一个半地址计算机

INTEL IA32系列和FREESCALE系列

计算(a+b)*c

MOVE a,D0;将a从存储器放入寄存器D0

ADD b,D0;将b从存储器放入寄存器D0

MOVE c,D1;将c从存储器放入寄存器D1

MULU D0,D1;将寄存器D0乘以寄存器D1

接下来讨论ARM的指令,

ARM是一个32的位的计算机,采用寄存器存储器结构,采用store/load指令在存储器和寄存器之间移动数据。

32位为一个字,16位为一个半字,16位为一个字

ARM有的16个寄存器,r0-r13为通用计算机,r14为链接寄存器,用于存放子程序返回地址。r15为程序计数器,r13为栈指针,但只要当需要使用时才会变为栈指针,

ARM指令

加法 ADD r0,r1,r2 [r0] ← [r1] +[r2]

减法 SUB r0,r1,r2 [r0] ←[r1]- [r2]

与 AND r0,r1,r2 [r0] ←[r1]·[r2]

或 ORR r0,r1,r2 [r0] ←[r1] ⊕[r2]

乘 MUL r0,r1,r2 [r0] ←[r1]*[r2]

寄存器-寄存器移动 mov r0,r1 [r0] ←[r1]

比较 cmp r1,r2 [r1] ←[r2]

相等跳转 beq label [pc]-label(跳转到label处)

ARM在算术或逻辑运算后不会自动更新状态标志,

更新ARM条件码,只有需要在指令助记符后面加后缀S,实现自动更新

SUBS r1,r1,#1;

在r1-1后,将结果放入r1并更新状态标志

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?