前言

回顾第五章前两节的内容;在前面,首先是了解了CPU的构成,主要由CU和ALU构成,给出了CU的功能:控制指令的取出、分析指令、执行执行,ALU的功能:进行数据的加工;了解了CPU要实现的五大功能:指令控制、操作控制、时间控制、数据加工、中断处理;ALU的内部所需的寄存器:通用寄存器、ACC、移位寄存器、暂存寄存器、PSW。CU内部所需要的寄存器:IR、PC、MAR、MDR。 接着在第二节我们了解了一个指令是如何被执行的;要清楚指令周期,机器周期,CPU周期,时钟周期,CPU时钟周期的区别,一条指令可以被分为取指令阶段,间址阶段,执行阶段、中断周期,了解了每个周期内其数据的流向。

接下去我们将进一步研究CPU内部的数据流向

一、数据通路和基本结构

什么是数据通路?数据通路是CPU内部两个部件之间进行交换数据所需要经过的部件路径称为数据通路。

对于数据通路来说,其CPU内部需要数据通路的无非就是CPU内部的寄存器和寄存器之间需要通路,内部寄存器和CPU中ALU之间的数据传送,寄存器和主存之间的数据传送。 所以接下去我们探讨的也就是这三种传送方式。

1.2 CPU内部的数据通路基本结构

CPU内部的数据通路基本结构有很多种,单总线型结构,内部数据的交换都通过总线传输;专用数据通路结构,内部部件只要存在数据交换,就设置一个专门的数据线;多总线型结构,CPU内部有多条总线,内部数据的交换可以使用不同的总线进行传输。

①单总线结构

单总线型结构如下,CPU内部的所有部件,都连接在同一个公共的数据总线上。

寄存器到寄存器

以将PC中的内容送至MAR,这就是取指令中的一个步骤,在前面了解取址周期的数据流向的时候,我们仅仅只是宏观的从机器周期去分析的,现在我们将从时钟周期出发,研究一个机器周期内完成的一个取址操作,由多少个微指令完成。

将PC中的内容送至MAR

(pc)-->Bus-->MAR

将PC的内容送至MAR,要让PCout有效,这样PC中的内容就可以输出送至总线Bus上,同时MARin也要有效,数据才能进入MAR;PCout有效和MARin有效信号都是由CU发出的控制信号。(CU的的功能:取址:由PC自动加1完成,分析指令:操作码送入指令译码器,译码得到的操作信号送入微指令发生器,同时PSW的信号以及时序控制信号一同送入微指令发生器,由微指令发生器产生的控制信号,控制数据的流向。PCout和MARin就是产生的控制信号)

从主存读数据到寄存器

就以从主存中读指令为例,此次要执行的指令,首先要进行取指令,指令的地址所在的位置就是即将要执行指令的存储地址。

(pc)-->Bus-->MAR

M(MAR)-->MDR, (pc)+1-->pc

(MDR)-->Bus-->IR

(pc)-->Bus-->MAR时,要让PCout有效,同时让MARin有效,这样才能把pc中的内容送至MAR中;M(MAR)-->MDR,让MARout有效,同时MDRin也要有效,同时CU发出的读信号也要有效,这样才能根据MAR中的地址,找到存储在主存中的数据并送至MDR中,与此同时,pc的内容会自动的加“1”;(MDR)-->Bus-->IR,要让MDRout有效和IRin有效,这样取出的指令就可以通过总线传输到寄存器IR中。

ALU和寄存器

以执行一条加法指令ADD ACC R1为例,ACC为目的操作数,R1为源操作数,将ACC中的内容和R1中的内容相加然后写回ACC中。

(R1)-->Bus-->Y

(ACC)+(Y)-->Z

(Z)-->ACC

(R1)-->Bus-->Y 将R1的内容取到Y寄存器,需要Yin和R1out信号有效,(ACC)+(Y)-->Z,将ACC中的内容取出,通过总线传输到ALU中,与Y中的进行加操作,将结果输出到Z寄存器,需要ACCout和ALUin信号有效; (Z) - ->ACC是将保存在Z中的计算结果保存至ACC 中,需要Zout和ACCin信号有效。

2⃣️多总线型结构

多总线型结构和单总线型结构唯一的区别就是,由于CPU内部有多个总线,所有在进行数学流通的时候,不需要等待,只要有总线空闲,就利用空闲总线进行传输数据,但是多总线型结构其控制较为复杂,硬件成本高。

3⃣️专用数据通路结构

专用数据通路结构,就是只有CPU内部的两个部件存在数据交换,就为他们两个部件设置专门的数据传输线路,这样的结构控制简单,但是这样会导致数据线非常多,混乱。

1.3以 ADD (R1), R2指令执行全过程为例,看数据流通的整体过程

先分析一下该条指令实现的功能,这是一个加法指令,将R2中的数据和R1中的间接寻址找到的数据相加,然后将加法运算后的结果写回主存。

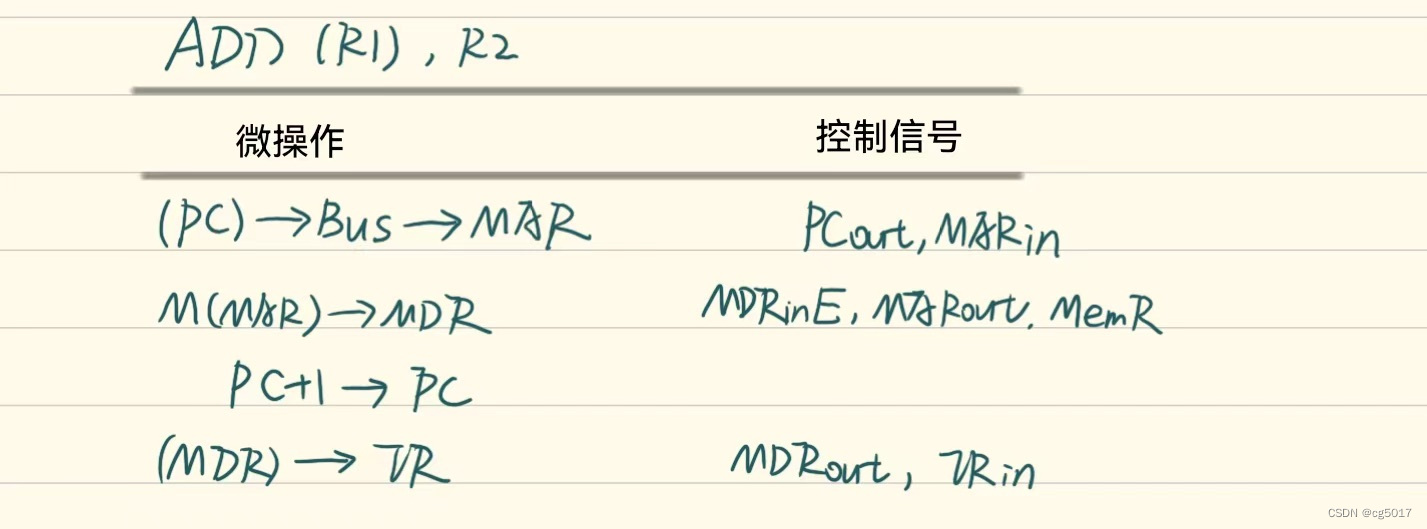

取指令阶段

在取指令结束后,即将指令放进了IR,就会自动的对指令进行译码,即产生一系列的操作信号供微操作发生器产生一系列微操作指令。

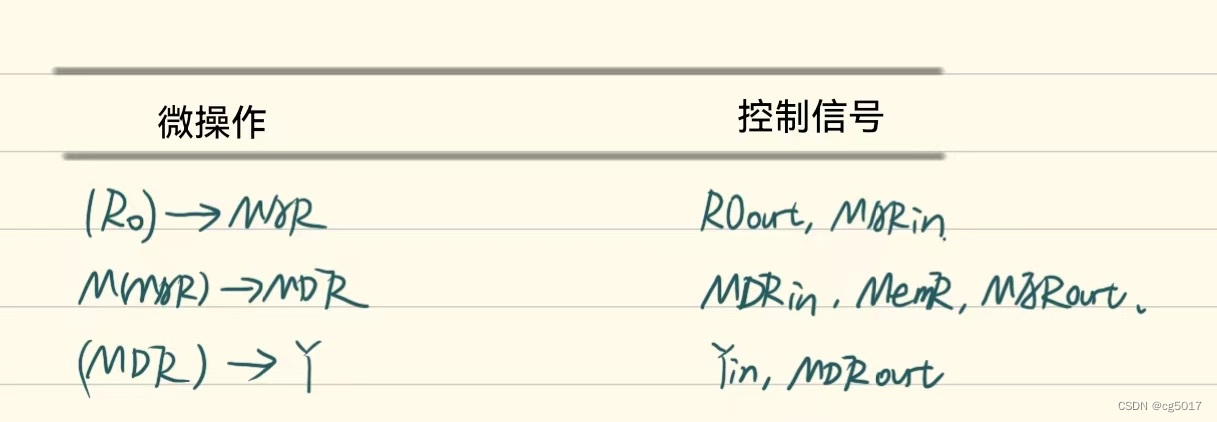

间址阶段

将R0的真实数据从主存取到Y寄存器。

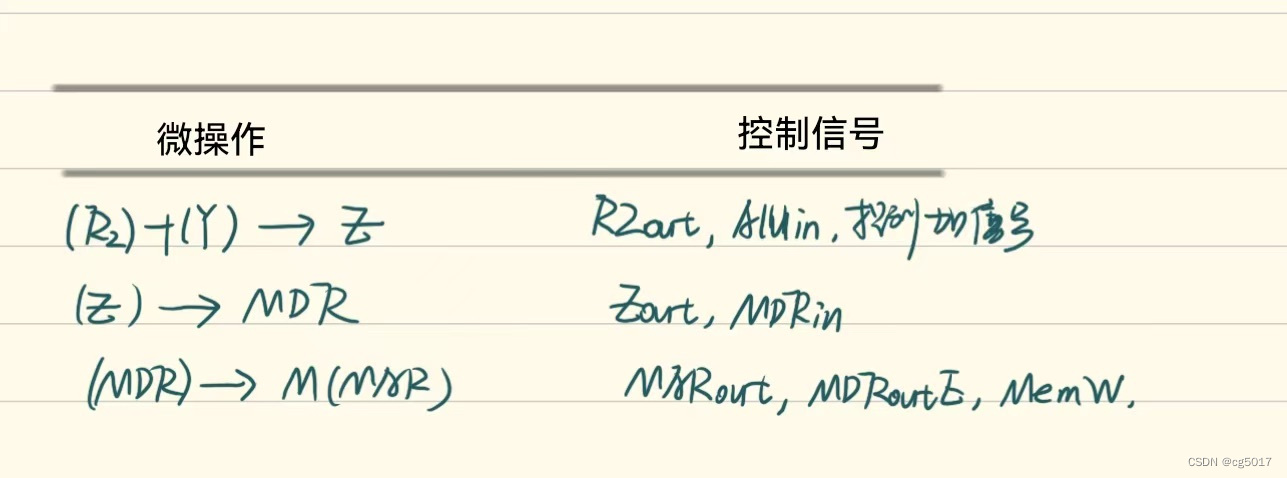

指令执行

执行加法指令,最后将结果写回主存,由于在间址的时候MAR已经存放了该内存单元地址,所以在将结果写回时,直接根据MAR中的地址写回主存就行。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?