学习《基于STM32F的嵌入式系统原理与应用》一书摘要

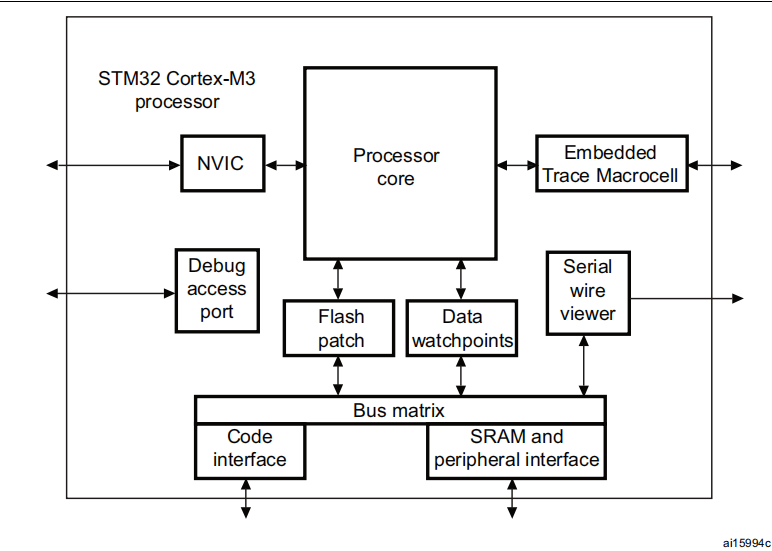

Cortex-M3内核

Cortex-M3的内核是32位的。基于该内核的处理器采用了Tail-Chaining中断技术,完全基于硬件进行中断处理,还采用了新型的单线调试技术,设计了一个专门用于调试的引脚。同时,该内核处理器集成了大部分存储控制器,开发者可直接在CPU处理器外连接Flash存储器。

Contex-M3内核采用了哈弗体系结构,拥有独立的指令总线和数据总线,可以同时访问指令和数据。两总线共享一个4GB存储器空间。

Contex-M3内核数据存储支持小端和大端模式。在小端模式下,数据的低位存储在低地址,高位存储在高地址。在大端模式下,数据的高位存储在低地址,低位存储在高地址。其工作模式分为处理模式和线程模式。

-

线程模式用于执行普通应用程序代码,可以在特权级或用户级下运行。

-

处理模式用于处理异常和中断,始终在特权级下运行。

在特权级下,可通过设置控制寄存器的CONTROL[0]位进入用户级,而用户级不可通过此方式进入特权级。从用户级进入特权级的唯一途径是异常。

该内核指令执行设计为三级流水线形式。一条流水线的每个分步骤称为流水线级。任何处理器在执行一条指令的时候,主要有三个步骤:取指、译码、执行。并行运行指令的方式称为流水线操作。

该内核指令执行过程中支持Thumb状态和调试状态,以及支持ARMv6架构的BE8/LE和非对齐访问特点。Thumb状态,又称16位指令集状态,是ARM处理器为了节省代码空间和提高代码密度而引入的另一种工作模式。

Cortex-M3总线

总线是一种内部结构,是处理器、内存、输入/输出设备之间传递信息的公用通道。几乎所有部件都通过总线连接,从而形成了计算机硬件系统。

I-Code 总线是一条基于 AHB-Lite 总线协议的 32 位总线,负责在 0x0000_0000 – 0x1FFF_FFFF 之间的取指操作。取指以字的长度执行,即使是对于 16 位指令也如此。因此 CPU 内核可以一次取出两条 16 位 Thumb 指令。

D-Code 总线是一条基于 AHB-Lite 总线协议的 32 位总线,负责在 0x0000_0000 0x1FFF_FFFF之间的数据访问操作。尽管 CM3 支持非对齐访问,但你绝不会在该总线上看到任何非对齐的地址,这是因为处理器的总线接口会把非对齐的数据传送都转换成对齐的数据传送。因此,连接到 D-Code总线上的任何设备都只需支持 AHB-Lite 的对齐访问,不需要支持非对齐问。

系统总线也是一条基于 AHB-Lite 总线协议的 32 位总线,负责在 0x2000_0000 – 0xDFFF_FFFF 和0xE010_0000 – 0xFFFF_FFFF 之间的所有数据传送,取指和数据访问都算上。和 D-Code 总线一样,所有的数据传送都是对齐的。

外部私有外设总线是一条基于 APB 总线协议的 32 位总线。此总线来负责 0xE004_0000 – 0xE00F_FFFF 之间的私有外设访问。但是,由于此 APB 存储空间的一部分已经被 TPIU、 ETM 以及 ROM 表用掉了,就只留下 0xE004_2000-E00F_F000 这个区间用于配接附加的私有外设。

调试访问端口总线接口是一条基于“增强型 APB 规格”的 32 位总线,它专用于挂接调试接口,例如 SWJ-DP 和 SW-DP。不要挪用此总线。

2986

2986

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?