目录

设计想法

通过利用简单电子元件及multisim仿真软件设计一个数电电子时钟电路,可以实现以下功能:

- 正确显示时,分,秒

- 可以实现对时,分,秒的分别校时

- 可以实现时钟的全部清零,设置初始时间

设计思路

时间显示:

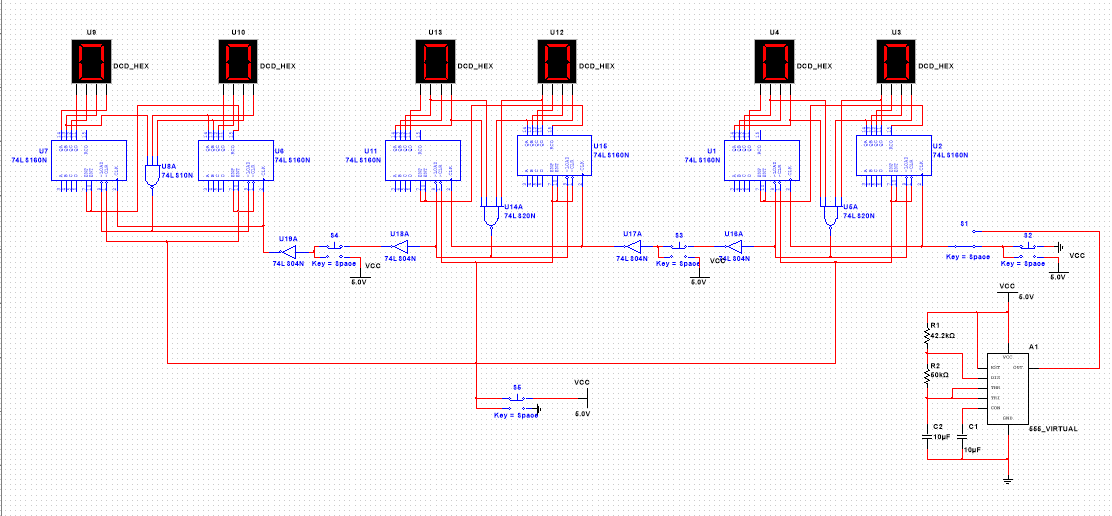

电子时钟需要显示时,分,秒分别对应的两位十进制数,考虑使用8个数码管显示。时部分的数字为24进制,分和秒部分的数字为60进制,考虑使用两块74LS160实现电子时钟的不同进制

计数及校时:

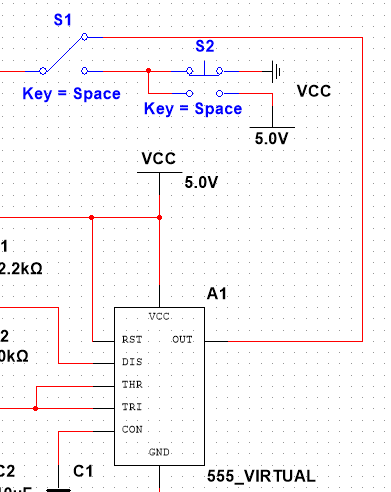

通过555定时器输出一个频率为1Hz的方波脉冲信号作为74LS160的时钟信号,当74LS160的EP端和ET端同时为1(高电平)时实现计数功能。校时过程需要设计开关电路断开555定时器脉冲信号的输入,并实现按动开关则输入一个有效信号,使计数器加一,可以设定时钟的初始值

时间复位:

当74LS160的~CLR为低电平时,通过异步清零功能可以实现时钟的全部清零。考虑通过开关电路控制,当不需要复位时,~CLR接Vcc(高电平);需要复位时,将~CLR接地(低电平)

仿真绘制

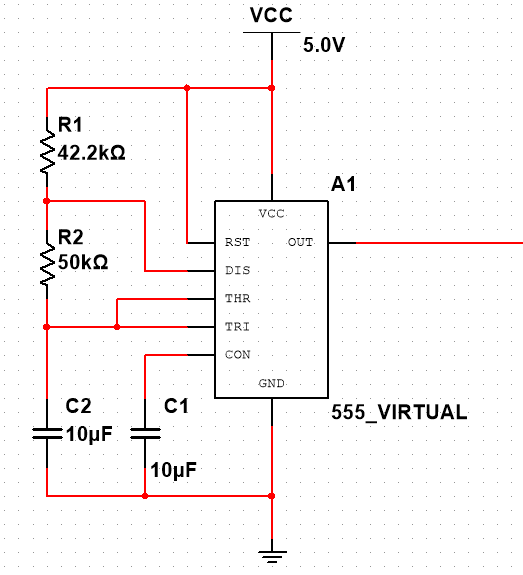

时钟信号输入端采用555定时器通过连接合适的电阻和电容,实现1Hz脉冲信号的输出

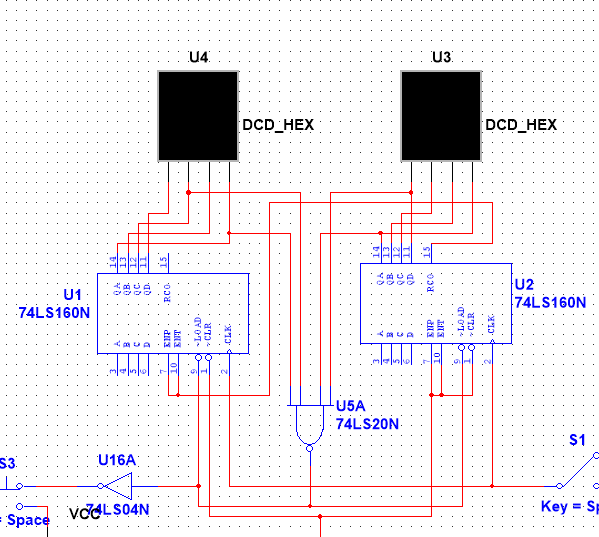

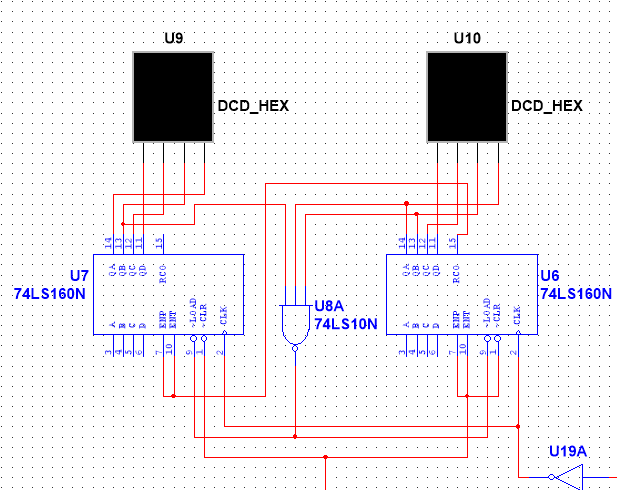

60进制分显示电路和秒显示电路相同,设计电路如下图所示。QA,QB,QC,QD为四个输出端与数码管相连;A,B,C,D为输入端这里不进行连接,相当于接低电平,预置数为0;RCO为进位信号输出端,将个位RCO与十位EP,ET相连。当有进位信号时,RCO输出高电平,此时十位EP,ET端同时为1,则十位开始计时;CLK端接555定时器脉冲信号输出端,用于接收时钟信号;~CLR及个位的EP,ET端通过开关电路控制,不使用复位功能时默认接高电平;~LOAD端为同步并行置入控制端,将十位和个位的~LOAD端接到一起,用于接收与非门传递的信号。当十位为5,个位为9时,与非门输出一个低电平给十位和个位的~LOAD端,~LOAD端实现同步并行置入功能

24进制的时显示电路,引脚连接思路和60进制分,秒显示电路的连接思路基本相同。这里直接上图,不过多赘述

通过下图所示连接实现是否进行校时功能的实现,开关S1可断开和555定时器的连接,按动开关S2按动一次即输出一个有效信号实现校时功能。对于时校时和分校时原理类似,在按动开关两端加入非门防止信号之间的相互干扰

总原理图:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?