本文是笔者参与2024年全国大学生电子设计竞赛的阶段性总结,记录了团队在“无线传输信号模拟系统(C题)”中的设计思路与实现过程。由于知识水平和时间限制,系统中仍存在诸多不足,希望借此分享与广大电子爱好者交流探讨,共同进步。

一、项目背景与任务目标

1.1 竞赛题目要求

根据C题要求,需设计一套能够模拟无线传输信号(含直达信号、多径信号及合路信号)的系统,具体要求包括:

-

信号类型:支持CW连续波和AM调幅信号(调制信号为2MHz正弦波)。

-

参数调节:载波频率(30-40MHz)、幅度(100mV-1V)、调制度(30%-90%)、多径时延(50-200ns)、衰减(0-20dB)、初相(0°-180°)等参数需步进可调。

-

精度要求:载波频率误差≤2%,调制度误差≤5%,时延误差≤10ns,衰减误差≤1dB。

1.2 设计目标

团队以ZYNQ7020为核心平台,尝试构建一套硬件与算法协同工作的系统,实现信号生成、参数动态调节及实时合路输出。设计过程中重点解决以下问题:

-

如何通过FPGA实现高精度信号调制与时延控制?

-

如何优化硬件电路以降低噪声干扰?

-

如何验证系统参数调节的准确性?

二、系统架构与实现

2.1 整体设计框架

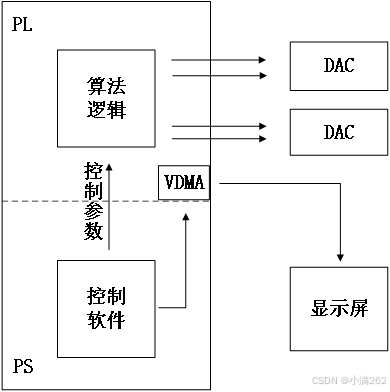

系统由ZYNQ7020主控平台、高速双通道DA模块、显示屏交互模块三部分组成,架构如图1所示:

-

PS端:运行Linux系统,负责参数输入与界面交互。

-

PL端:基于Verilog实现信号生成算法,包括载波调制、时延控制、衰减计算等。

-

DA模块:采用3PD5651E芯片(125MSPS)完成数模转换,输出模拟信号。

-

数学模型:

SD(t)=A⋅[1+mAcos(2πfmt)]⋅cos(2πfct)

-

SM(t)=α⋅A⋅[1+mAcos(2πfm(t−τ))]⋅cos(2πfc(t−τ)+ϕ)

其中,αα为衰减系数,ττ为时延,ϕϕ为初相。

-

FPGA实现:

-

基于120MHz系统时钟,通过DDS(直接数字频率合成)生成载波与调制信号。

-

时延控制采用采样点偏移法,将延时量转换为时钟周期数,误差控制在±8.33ns。

-

2.2.2 参数调节与合路输出

3.2 显示屏交互

五、总结与展望

本项目通过ZYNQ7020平台实现了无线传输信号模拟系统的基本功能,初步验证了设计方案的可行性。然而,在信号精度、实时性等方面仍有较大提升空间。未来计划从以下方向改进:

源码与资料:关注后私信获取完整工程文件(含Verilog代码、PCB设计图)。

-

衰减计算:将dB衰减转换为线性增益,通过查表法快速实现乘法运算。

-

合路逻

三、硬件设计与优化

3.1 关键电路模块

-

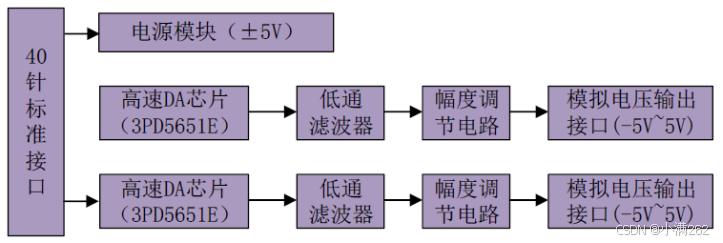

DA输出电路(图2):

-

采用低通滤波器(截止频率45MHz)滤除高频噪声。

-

通过运放电路实现差分转单端输出,提升信号稳定性。

-

-

电源设计:

-

使用LT3042低噪声LDO为DA芯片供电,降低电源纹波。

-

-

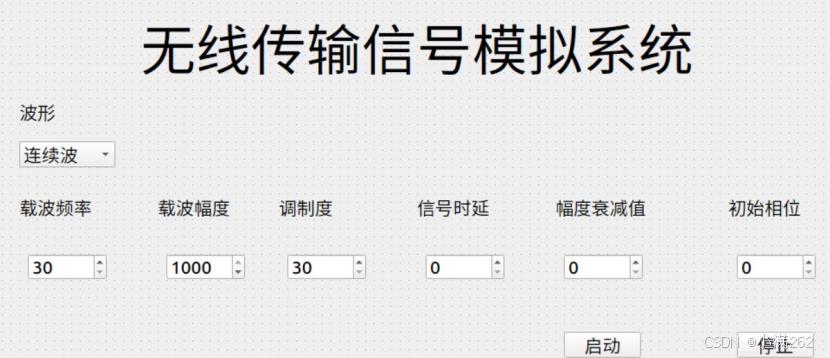

方案选择:7寸TFT LCD(1024×600分辨率),通过VDMA框架实现图形界面动态刷新。

-

界面功能:支持载波频率、幅度、调制度等参数实时设置(图3)。

-

辑:在FPGA内直接对SDSD与SMSM进行加法运算,输出SOutSOut。

四、测试结果与不足

4.1 测试数据

参数 理论值 实测值 误差 载波频率 35MHz 34.987MHz 0.037% 调制度 50% 50.52% +0.52% 多径时延 100ns 106.5ns +6.5ns 多径衰减 10dB 10.9dB +0.9dB 4.2 不足与改进方向

-

时延精度:受限于120MHz时钟,最小步进为8.33ns,后续可尝试提升系统时钟频率。

-

界面响应速度:PS端与PL端通信存在微小延迟,需优化AXI总线协议。

-

噪声抑制:高频信号仍存在轻微谐波干扰,需进一步优化滤波器设计。

-

引入更高精度的时钟源(如PLL倍频)。

-

探索基于CORDIC算法的动态相位补偿方法。

-

扩展功能支持更多调制方式(如FM、QAM)。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?