信号分离装置(H题)总结报告

- 总体设计思路和框图

首先通过NE5532集成运算放大器将信号A和信号B相加,得到信号C。由于单片机的输入幅值要求为0~3.3V,先设计可调电压生成器,将生成的电压用于抬升电路,将信号C的电压抬升到所需幅值。接着将信号C输入到STM32G431RBT6,进行FFT快速傅里叶变换,读取并分析信号频谱,通过频谱判断波形。再将所得频率与波形信息传给AD9833模块进行波形的输出。

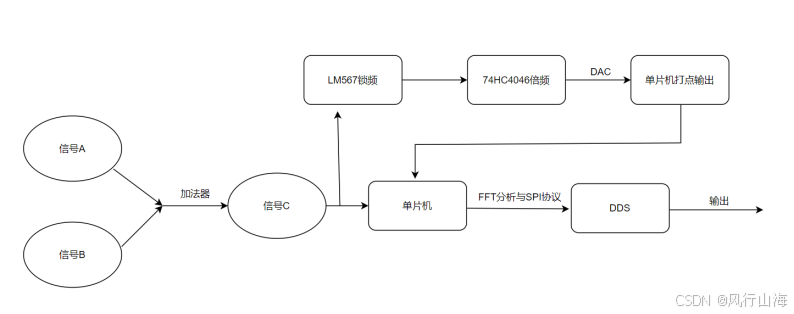

为实现稳定同频显示,我们尝试了多种方案。首先是使用LM567芯片将信号C中的A和B频率选出,并将所选频率输入到74HC4046芯片,加上分频器以得到32倍频的信号,再将信号作为DAC给到单片机进行打点输出,后因为单片机的精度不够遂放弃该方案。

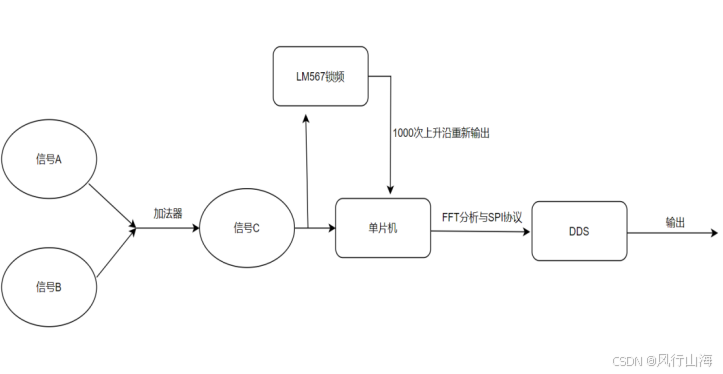

其次是将LM567所选频率作为AD9833的重新输出信号,经过分析选择当方波上升沿1000次时,AD9833重新从0开始输出信号,从而实现同频显示。

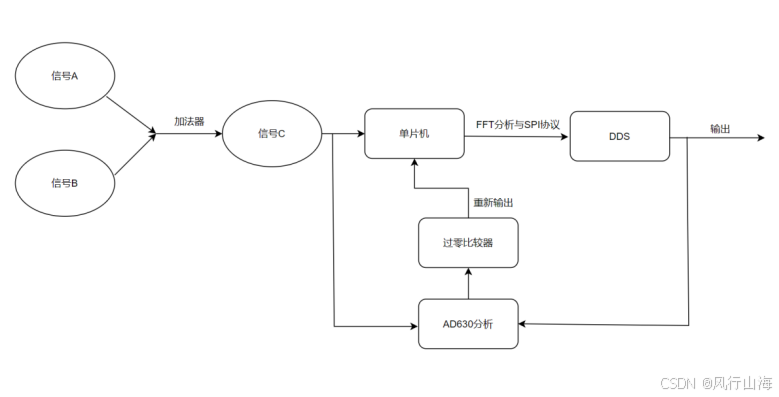

然后是通过AD630模块读取输入与分离后的频率差,并输出相应相位的电压值,通过过零比较器生成方波并输入到单片机中,当检测到上升沿时,AD9833重新输出信号,实现同频显示。

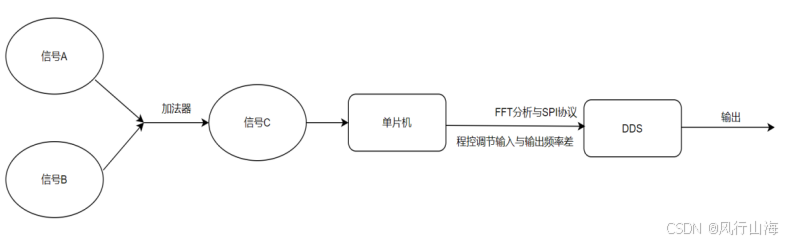

最后是通过分析输入与输出的频率差,手动调节输出频率,使得输入与输出频率差值尽可能小,产生的相移减小,从而实现同频显示。最终选择的时该方案。

一框图

二框图

三框图

四框图

- 硬件设计

(一)NE5532集成运算放大器

该运放的性能较LM324有了较大的提升,共模抑制比较高,性能更好,能够更加稳定地输出信号,误差更小,LM324无法达到的预期幅值,NE5532能够轻松达到,产生的信号更加准确与稳定。

(二)DDS模块

我们所选的AD9833为双通道输出型DDS模块。该型号DDS是低功耗、可编程波形发生器,能够产生正弦波、方波、三角波。无需外接元件,输出频率和相位可通过编程实现。通过SPI协议即可将单片机识别到的频率与波形给到DDS并输出相应波形。

(三)锁相器

我们所选锁相器有三种,分别是LM567、CD4046、74HC4046。

LM567内部包含鉴相器、压控振荡器等,通过与外部电路的低通滤波器等构成锁相环,并通过外部的电容和电阻调节中心频率,环路滤波器调节捕捉带宽度,当外部输入信号频率在捕捉带内时,方波信号的频率会与输入信号频率相等,从而实现选频锁相。

CD4046内部结构与74HC4046相似,内部比LM567多了更多相位比较器,从而可以实现更多功能,在此题中我们使用的是比较器2,与LM567相似。两者不同在于工作频率和能够输出的最大频率,若想达到32倍频的输出信号,只能选取74HC4046。

(四)锁相放大器

我们所选的锁相放大器型号为AD630。该模块能够实现平衡调制、平衡解调以及锁相放大功能,本题只要使用其锁相放大功能即可。锁相放大是通过比较待测信号与参考信号的相位,当两者相位相同时,OUT2口输出高电平信号;相位相差90°时,OUT2口输出为零;相位相差180°时,OUT2口输出低电平信号。相位差与电压的关系为

。

- 软件设计

软件设计方面,我们采用的主控板是STM32G431RBT6。首先先通过ADC采样对A+B的合成信号进行采样读取,然后为了提高采样精度,在代码中添加了汉宁窗,然后用ARM里自带的函数进行FFT变换,得到频谱数组。在得到频谱数组之后,为了得到每一个频谱数组对应的频率大小,我们是通过比较实际输入频率以及读入的频谱数组位置的关系来进行确认。FFT变换之后,采用的DDS是AD9833,通过SPI协议来控制双路AD9833输出正弦波或者三角波。

判断正弦波和三角波的方法,通过对正弦波和三角波实际频谱的分析来确认。主要是通过比较正弦波和三级波实际频谱的三倍频和五倍频的关系来确认。

最后则是稳定同频显示的方法,在和其他小组讨论以后,有一个通过软件实现的方法就是,先通过LM567将输出的合成C信号内部的信号进行锁相成方波,然后单片机读取锁住的方波的上升沿,每到一个上升沿便重置一次DDS的输出,以此来将输出信号能够实现稳定同频显示。

具体代码会在后续上传,包含对代码内容的解释

四、总结

我们先用NE5532将信号相加得C,再经电压抬升、FFT分析频谱后,由AD9833输出。为同频显示,尝试多种方案,最终选择程控调节输出频率使差值小以减小相移实现。涉及模块包括性能优的NE5532、可编程的AD9833、能选频锁相的LM567等锁相器及锁相放大用的AD630。

通过完成这次赛题,我们深刻体会到工程实践中解决问题的复杂性和多样性。设计信号分离装置过程中,团队不断尝试多种方案,从最初的锁相环方案到最终的程控调节频率方案,体现了在面对技术难题时的灵活应变和创新思维。这让我们明白,在实际工程中,理论知识固然重要,但更重要的是将理论与实践相结合,勇于尝试和调整。同时,对各个模块的深入了解和精准应用,如NE5532的高性能优势、AD9833的编程灵活性等,是成功实现项目的关键。这个过程也让我们认识到团队协作的力量,不同成员对方案的讨论和改进推动了项目向前发展。在今后的学习和工作中,我们将更加注重实践能力的培养,积极面对挑战,不断探索和创新。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?