作者的话

补充一些常用的算法,想到哪里写到哪里,很多文字和程序框架都是摘抄的ADI原厂给的资料。

有兄弟可能会说OP你怎么总是摘抄,我想说这里的摘抄,有的是ADI的AE写的,有的是我去参加ADI的培训现场记录的,是公开资料找不到的!

作者的话

ADAU1701EVB开发板在未升级成ADAU1701EVB-A2B前,我看了一下写的例程,虽然超过了100个,但我发现还是有很多常用的算法并没有写进来,那就借着这次产品大升级,我把例程也升级一下,加一些常用的,但是没有写的例程。

文章中的开发板和仿真器哪里找

产品链接: https://item.taobao.com/item.htm?spm=a21dvs.23580594.0.0.621e2c1b6F3EMW&ft=t&id=811967886964

产品链接: https://item.taobao.com/item.htm?spm=a1z10.5-c.w4002-5192690539.11.ad392dbdrCme9n&id=38242936768

软件准备

SigmaStudio4.7

用到的例程

BasicDSP的几个例程

SigmaStudio 软件里有一个 BasicDSP 的类,所有的 SigmaDSP 都有可能会用到,下面从ADI的文档里,摘了几个例程来简单说一说,逻辑算法类,共同学习。

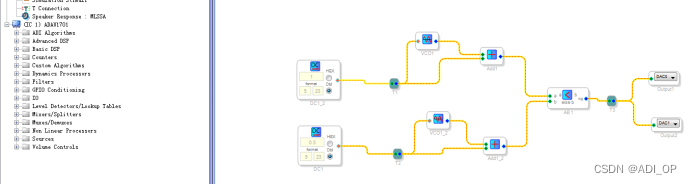

- DC Input、Adder 和 AB in/Out Condition 的组合使用(例程 17)

例程采用“直流输入”(DC Input)模块、“加法器”(Adder)和一个“ AB 输入/输出条件”(AB in/Out Condition)模块,用于比较两个输入 VCO 源的电平,其中,这两个源均加上了一个直流值。“条件”模块的输出通过一个“ T 形连接” T Connection)分路并传送至“输出”(Output)端。

在当前配置中,条件为假,信号 B 将传送至输出模块。如果单击“ AB 输入/输出条件”模块中 的“条件” (Condition)图标,使其显示大于符号(>),然后重新编译,则条件为真,结果输出信号 A。

- Delay 延迟和 Feedback 反馈的组合使用(例程 18)

这个例程中,来自“延迟” (Delay)模块的输出在一个“ T 形连接”处分路,然后传送至“输出”端,同时馈入“反馈” (Feedback)模块,然后传回“多控制混频器” (Multiple Control Mixer) 的第二输入端。

- Linear Gain 线性增益和 Divide 除法和 DSP Readback 模块的组合使用(例程 19)

该例程显示的是如何通过“线性增益”(Linear Gain)模块来实现纯增强,如何通过“除法”(Divide) 模块来用一个值除以另一个值,以及“ DSP 回读” (DSP Readback)模块是如何从 DSP 中读回值的。

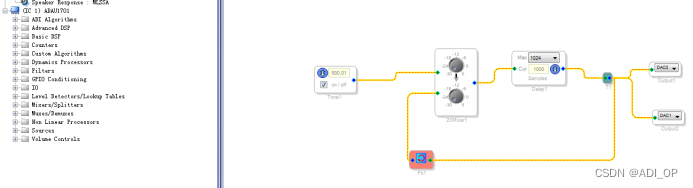

- DC Input 直流输入和信号变换 Signal Invert 模块的组合使用(例程 20)

该例程采用“直流输入” (DC Input Entry)模块、“信号音(查找/正弦)” (Tone (lookup/sine)) 模块、“信号变换” (Signal Invert)模块、“值保持” (Value Hold)模块和“输出” (Output)模块。 其中,“值保持”模块保持绿色引脚的输入信号,而“直流输入”模块红色引脚处的“控制”Control) 输入则经反相处理。

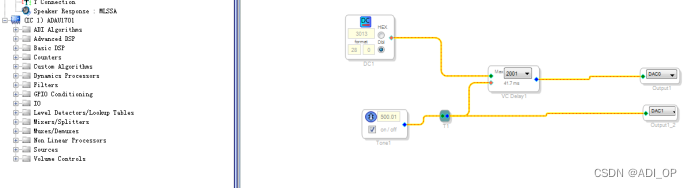

- DC Input 和 Tone (lookup/sine)和 Voltage-Controlled Delay 模块的组合使用(例程 21)

该原理图采用“直流输入” (DC Input)模块、“信号音(查找/正弦)” (Tone (lookup/sine))模块、 “ T 形连接” (T Connection)、“电压控制延迟” (Voltage-Controlled Delay)模块和“输出” (Output)模块,展示了电压控制延迟算法在其中的工作方式。当延迟处于最大允许范围之内时, 直流输入将延迟采样发送至输入信号;如果超过最大允许值或设为 0,则输出未定义。其中,电压控制延迟的最大延迟设为 2001 个采样。直流输入的最大值设为 3013。

RMS 详解

RMS限幅器也是一个比较重要的算法,这里浅摘了几个原厂给的程序框架。

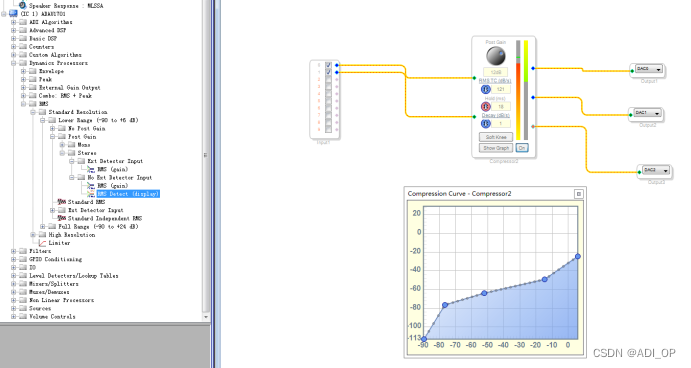

- RMS 检测 (RMS Detect)的用法(例程 22)

这个例程为一种音频流应用,采用了“ RMS 检测” (RMS Detect)(显示)模块及输入/输出模块。在以下所示示例中,需要注意的是“压缩曲线” (Compression Curve)窗口、显示栏上的相对输入/输出电平和“后增益” (Post Gain)旋钮。

水平输入电平轴上的阈值(即电平匹配点,此处无动态处理)设为约 35 dB,垂直输出轴上的阈值也作相同设置。超过阈值的压缩比约为 2.7:1。

对于低于 35 dB 的所有输入信号,其输出电平将不受影响。然而,当输入超过该阈值时,输入每增加 2.7 dB,输出将只减少 1 dB。

两个显示栏分别显示输入电平和压缩比(越绿表示压缩比越高)。绿色输入水平栏显示的是当前电平之前的上一个值的电平。

这种情况下,压缩大幅降低了输出电平,为了进行补偿,有必要将输出调高。

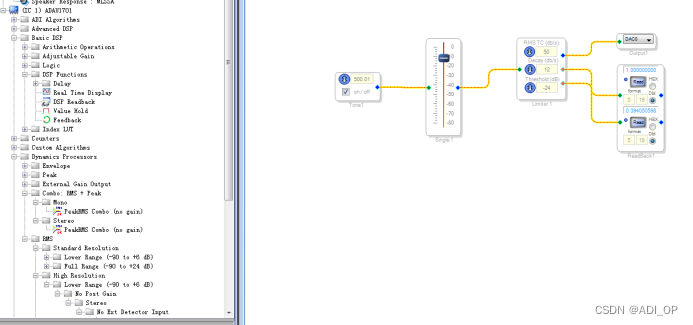

- 限幅器 (Limiter)的用法(例程 23)

该设计采用 “信号音 (查找/正弦)”(Tone (lookup/sine))模块、“单音量 (共享)”(Single Vol (shared))模块、“限幅器” (Limiter)、“ DSP 回读” (DSP Readback)模块、“端子” (Terminal) 和输出模块。其中,输入信号的阈值点设为-24 dB,当输入的均方根值超过该值时,则依据“限幅器”帮助页面上给出的比例降低增益。

请看“限幅器”模块,蓝色引脚输出经动态限幅处理的信号。第一红色引脚(三个引脚中间的那个)输出 1,此值可从“回读” (Readback)模块中的数字框中读取,表示限幅器正根据即时限幅比(Gn)对输入进行钳位处理。

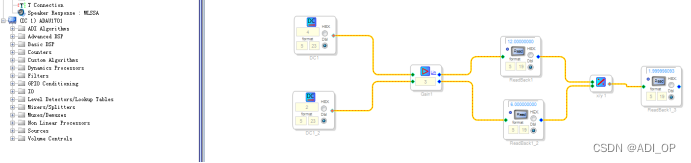

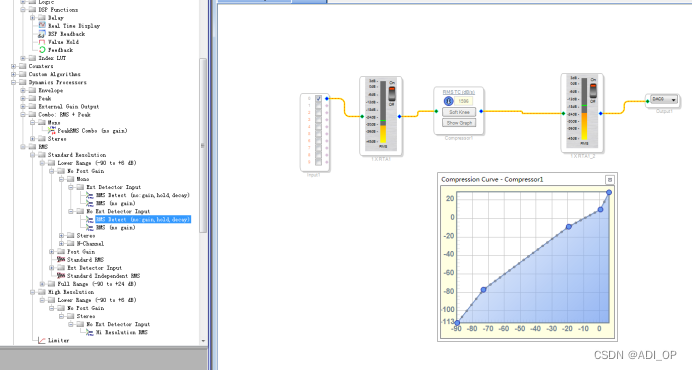

- (RMS Detect) (no:gain, hold, decay)的用法(例程 24)

以下设计采用“ RMS 检测(无:增益、保持、衰减)” (RMS Detect) (no:gain, hold, decay) 模块、“单电平检测器” (Single Level Detector)模块和输入/输出模块。原理图显示的是输出信号电平在处理后的递增情况。输入轴上的阈值设为-30 dB。对于低于-30 dB 的输入,其输出电平不受影响。但是,当输入信号超过阈值时,输出将根据所示曲线的扩展比(超过阈值时约为2.5:1,即强扩展)急剧增加。

下一章预告

前面的文章写的都是零散的功能,下一章OP老师带着大家做一个狠简单的产品框架,把产品级音频算法框架的开发过一遍。

943

943

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?