作者的话

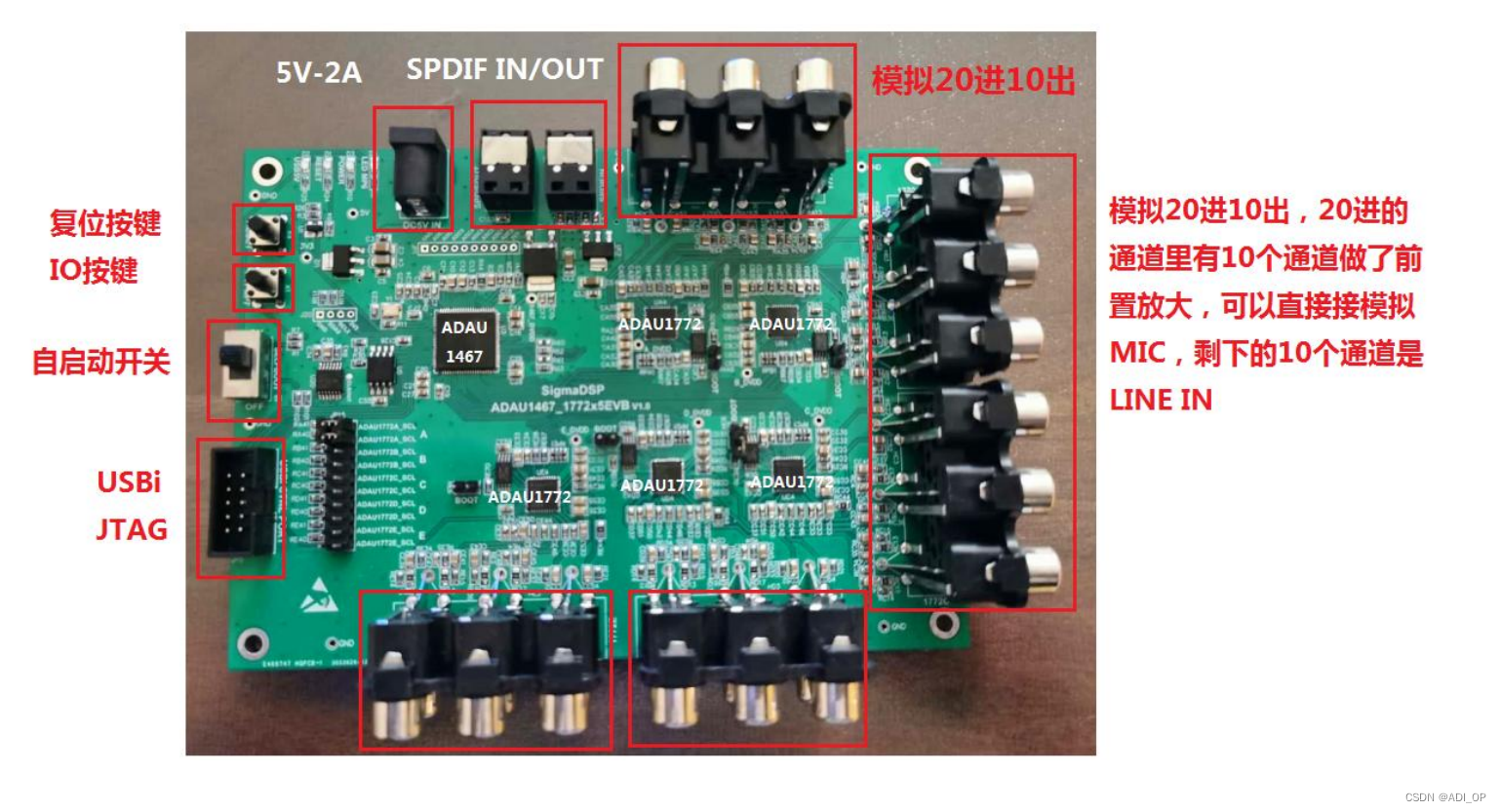

ADAU1467是现阶段ADI支持最多通道的ADAU音频DSP,他配合外部的AD/DA,可以实现最多32路音频通道,接了一个小项目,我拿它做了一块20进10出的板,10个MIC/LINE输入,10个LINE IN输入,10个HPOUT,算是把他的接口几乎都用全,芯片性能开发到了极致。(其实可以做20个MIC IN,但是因为客户的具体需求是10个LINE IN,10个MIC IN)

芯片选型

项目背景的话,做这块板的目的是给ADAU1467搞功能验证,还有极限性能评估,所以并没有考虑更细节的芯片成本,怎么方便怎么来。

主芯片当然就是ADAU1467了,CODEC考虑到要LINE IN的同时能够模拟MIC IN,这就要求Codec的AD需要具备前置放大,需要有偏置电压,我选了ADAU1772做Codec,这其实也是一颗DSP,但他片内有一个adda,能做到4进2出,而且4进全部可以支持MIC IN,搞起来非常方便快捷,于是我就直接用它了。这颗codec也因为有自带的运放,我在模拟输出的设计时就不需要额外加运放了。

4进2出去配ADAU1467显然是不够的,那我就拼5个,就有20进10出了,这是我的选型思路。

这个系列文章将对这个电路板的软硬件开发设计做详细讲解,上一章我们讲了硬件设计,这一章我们开始讲软件开发。

硬件准备

开发板的产品链接:https://item.taobao.com/item.htm?id=625095214294&spm=a1z10.5-c.w4002-5192690539.15.713a1c74E0XfRv

调试器的产品链接:https://item.taobao.com/item.htm?id=38242936768&spm=a1z10.5-c.w4002-5192690539.11.663b2dbdDNXVZF

ADAU1467 的开发 10:总音量增益

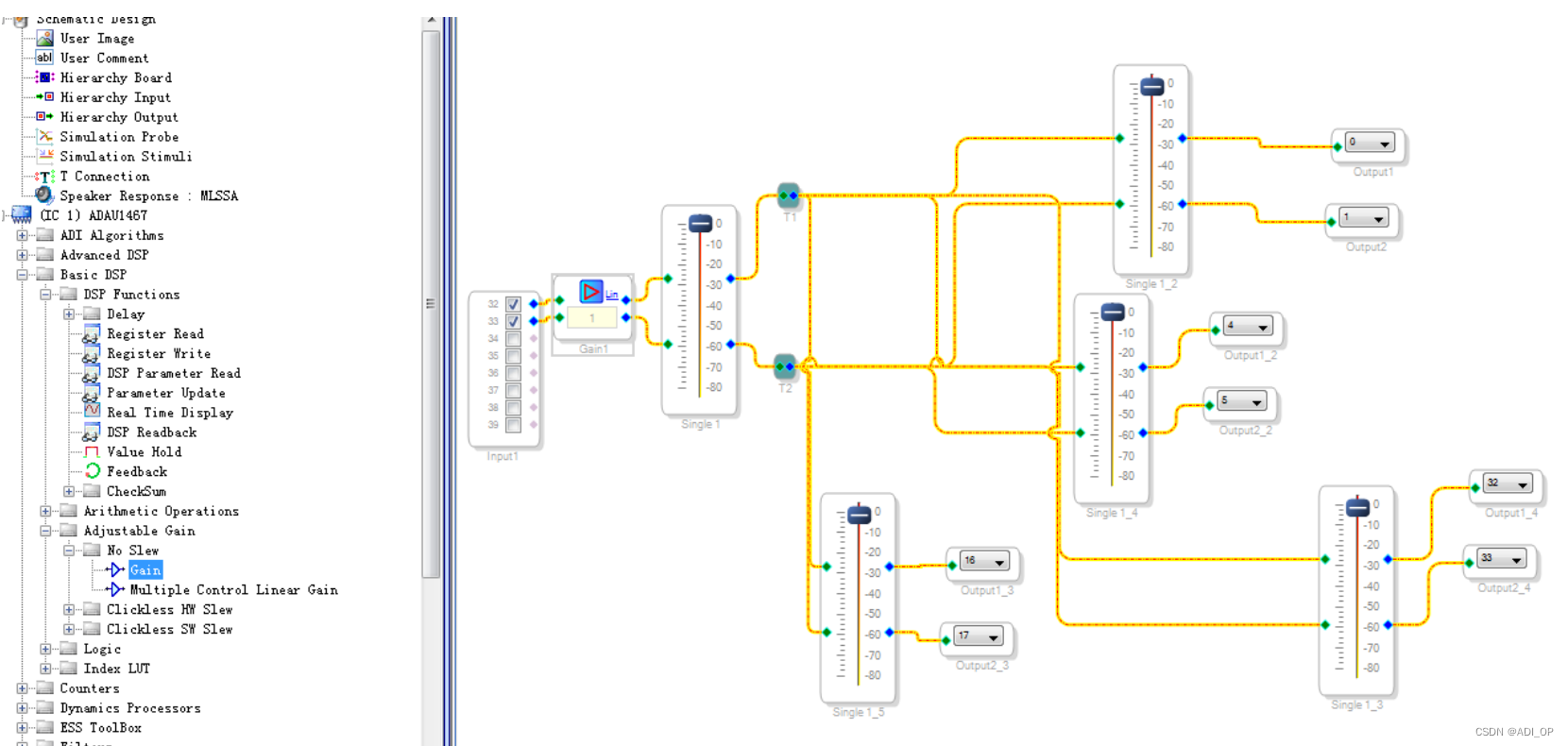

通过上面的几个调音量的例程,用户可以发现,原始音量进来,我们的调音量模块只能对他进行音量减小的操作,想要增大音量,需要外部设备的输入的音量增加。那么原始音源进来,可否通过软件进行增益呢?答案一定是可以的,这个很简单,DSP 是怎么做的,加一个线性增益模块就好啦,看下面这个例程:

一个线性增益模块加到音源输入之后,数字自己填,数字越大,增益越多,直接把音量拉起来,大家可以改改数试试看,效果很明显。

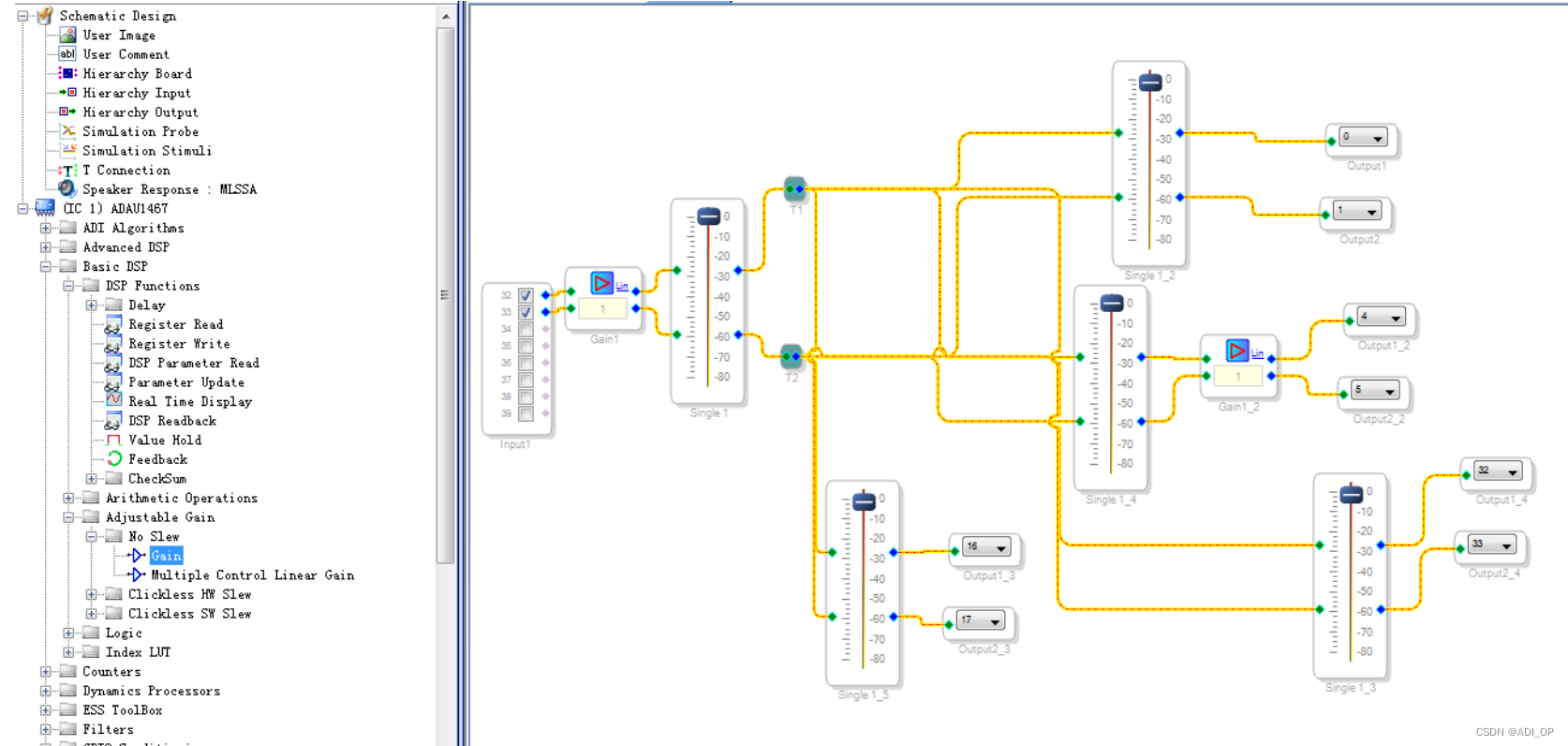

ADAU1467 的开发 11:选择通道增益

这种设计很常见,比如在音源进来后进行音效处理,某个通道需要增益加强,就加一个模块。

这个程序里,我就单独在 4/5 输出通道这里再加了一个增益,让这个立体声输出音量更大。

705

705

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?