作者的话

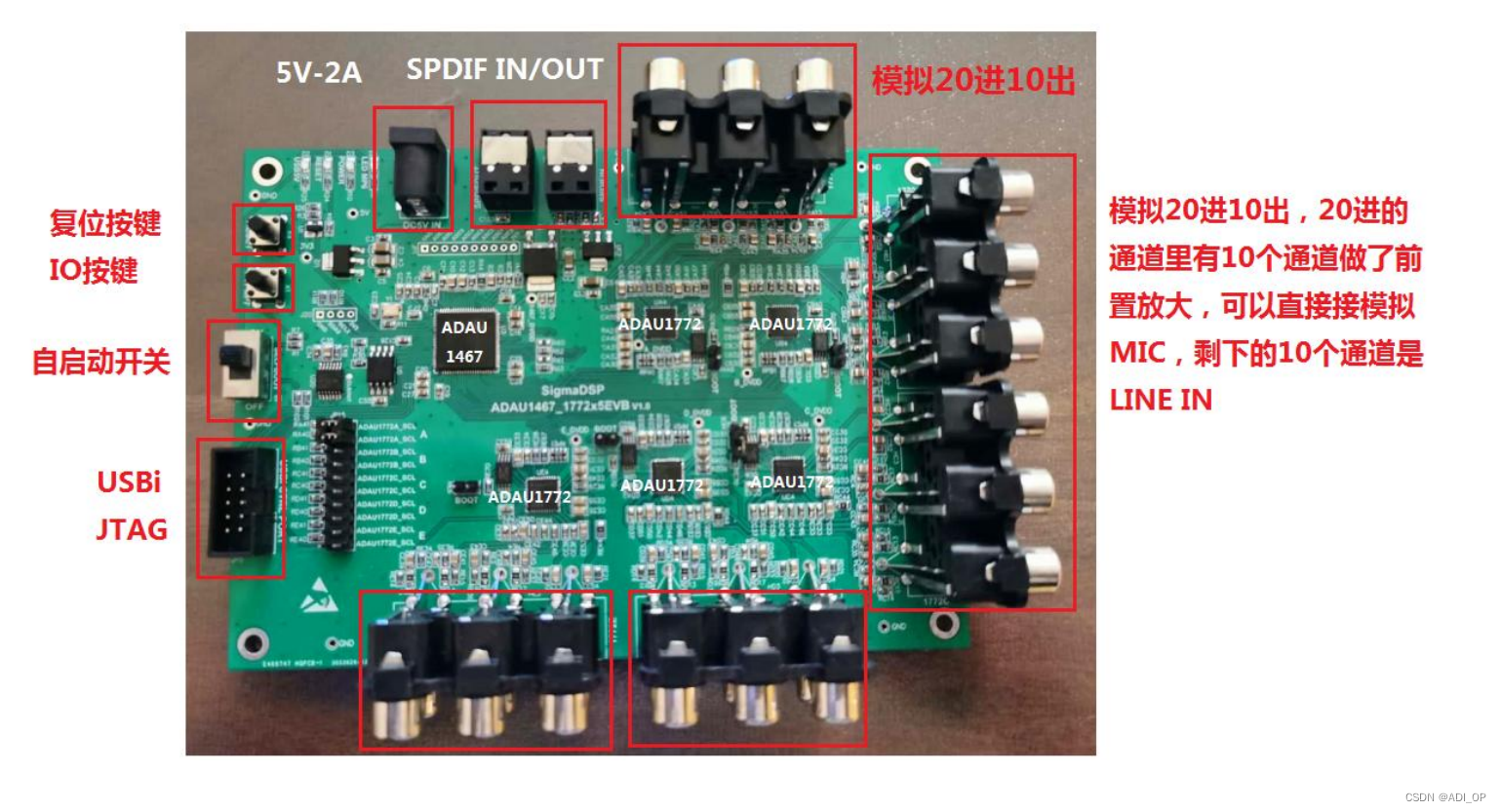

ADAU1467是现阶段ADI支持最多通道的ADAU音频DSP,他配合外部的AD/DA,可以实现最多32路音频通道,接了一个小项目,我拿它做了一块20进10出的板,10个MIC/LINE输入,10个LINE IN输入,10个HPOUT,算是把他的接口几乎都用全,芯片性能开发到了极致。(其实可以做20个MIC IN,但是因为客户的具体需求是10个LINE IN,10个MIC IN)

芯片选型

项目背景的话,做这块板的目的是给ADAU1467搞功能验证,还有极限性能评估,所以并没有考虑更细节的芯片成本,怎么方便怎么来。

主芯片当然就是ADAU1467了,CODEC考虑到要LINE IN的同时能够模拟MIC IN,这就要求Codec的AD需要具备前置放大,需要有偏置电压,我选了ADAU1772做Codec,这其实也是一颗DSP,但他片内有一个adda,能做到4进2出,而且4进全部可以支持MIC IN,搞起来非常方便快捷,于是我就直接用它了。这颗codec也因为有自带的运放,我在模拟输出的设计时就不需要额外加运放了。

4进2出去配ADAU1467显然是不够的,那我就拼5个,就有20进10出了,这是我的选型思路。

这个系列文章将对这个电路板的软硬件开发设计做详细讲解,上一章我们讲了硬件设计,这一章我们开始讲软件开发。

硬件准备

开发板的产品链接:https://item.taobao.com/item.htm?id=625095214294&spm=a1z10.5-c.w4002-5192690539.15.713a1c74E0XfRv

调试器的产品链接:https://item.taobao.com/item.htm?id=38242936768&spm=a1z10.5-c.w4002-5192690539.11.663b2dbdDNXVZF

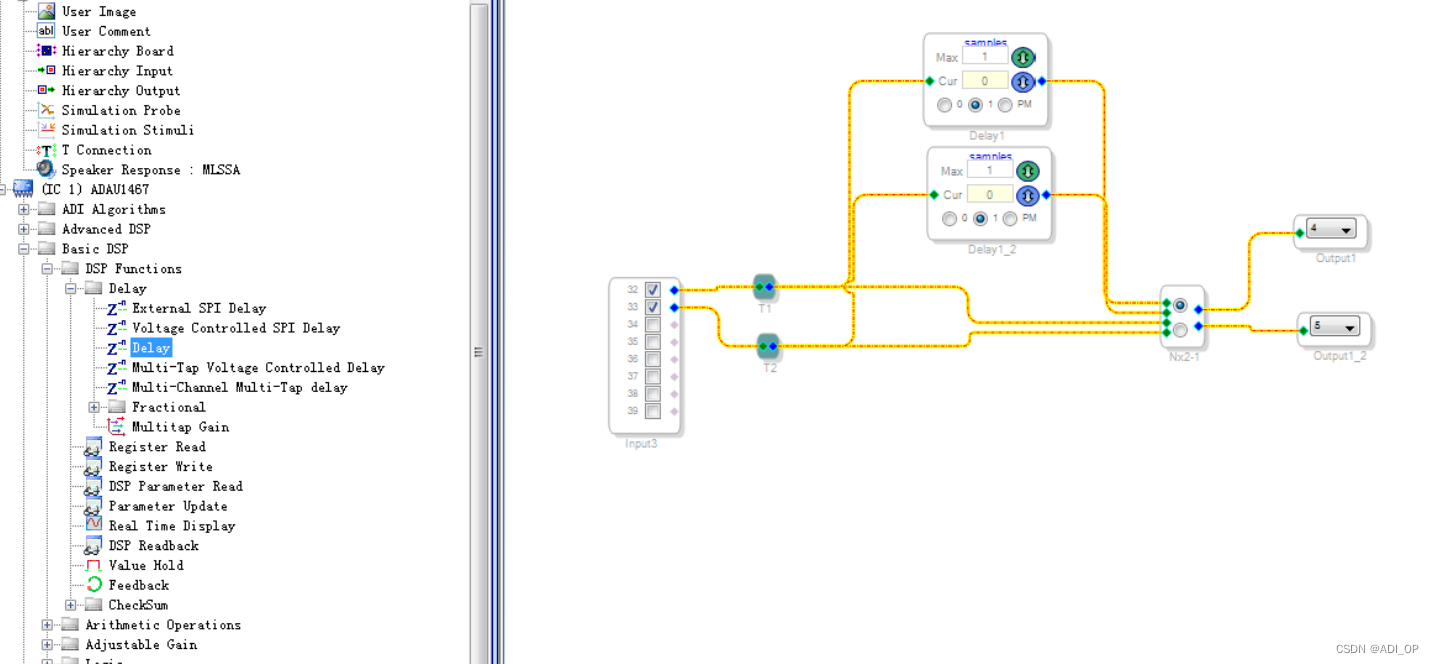

“延迟”(Delay)模块(采用 Z-a 算法)向信号流中添加一个可变延迟,其范围在 1 与 DSP 的最大可用内存之间。 特定延迟模块的最大可用延迟取决于系统可用总数据 RAM,该值由 DSP 处理器数据手册规定。设置“最大”(Max)控制值,分配 DSP 中的内存并保留这些内存,专供这一特定模块使用,降低设计中所有其他延迟模块的可用内存。这是一种编译器指令,可修改汇编代码,因此,每当更改“最大”设置时,您必须重新编译并下载程序。

注意:此规则适用于可分配内存的任何模块(如压缩器模块)。最大延迟值范围局限于 RAM。

我做一个例程:

在这个例程呢,我把延迟加了进来,并且做了一个开关,上面的音频流是加了延时的,下面的音频流是直通,通过开关来选择,大家可以听一下有没有区别吧。

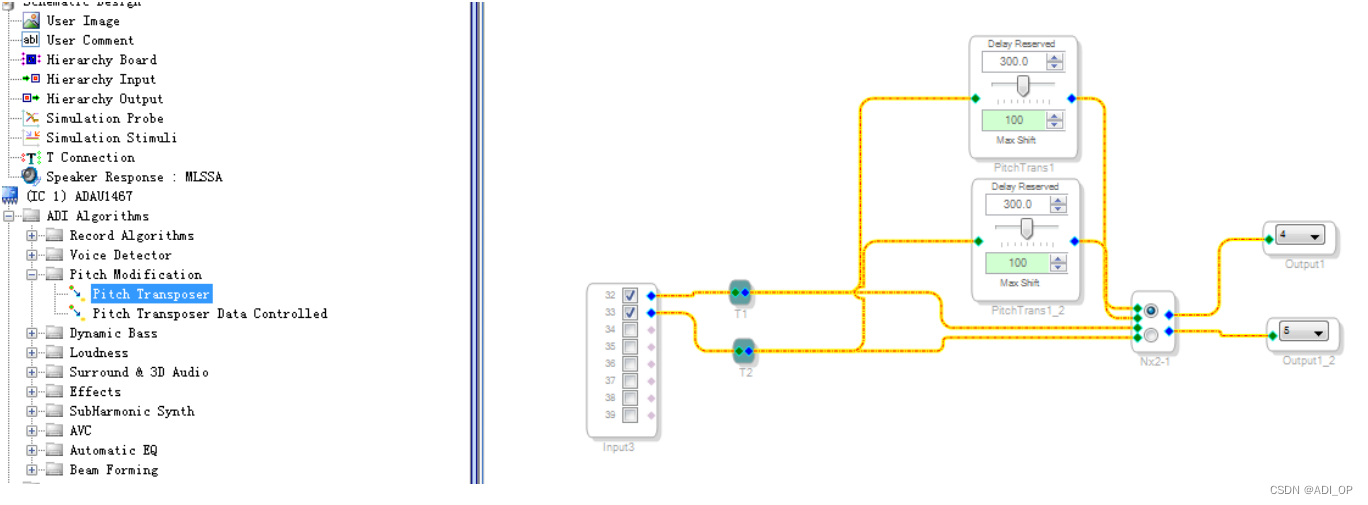

ADAU1467 的开发 31:移频

ADAU1467 有专门的移频算法,这个模块多用于防啸叫,我只给一个最简单的例程告诉你在哪里,至于防啸叫就需要用户自己在自己的声乐环境下细调了。

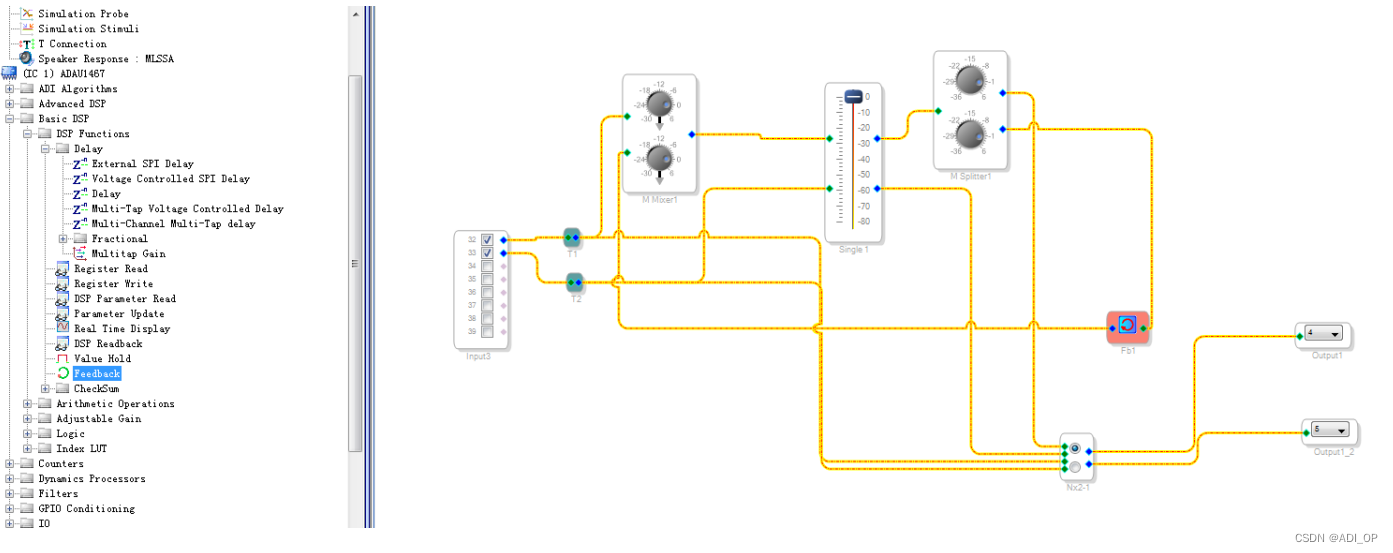

ADAU1467 的开发 32:反馈

“反馈”(Feedback)算法在信号通道中生成一个延迟,并将信号重新引导至该通道中较早发生的输入。(图中所示即为这种反向信号流,这是唯一一个绿色输入位于右侧、蓝色输出位于左侧的模块。)注意,如果设计中要求反馈,则必须使用该模块。

我做一个例子,主要是要讲一下这个反馈的信号流是反的:

通过开关的选择,上面是经过反馈后的音效,下面的是直通的音效,对比音效还是比较明显的。

ADAU1467 的开发 33:电平实时显示

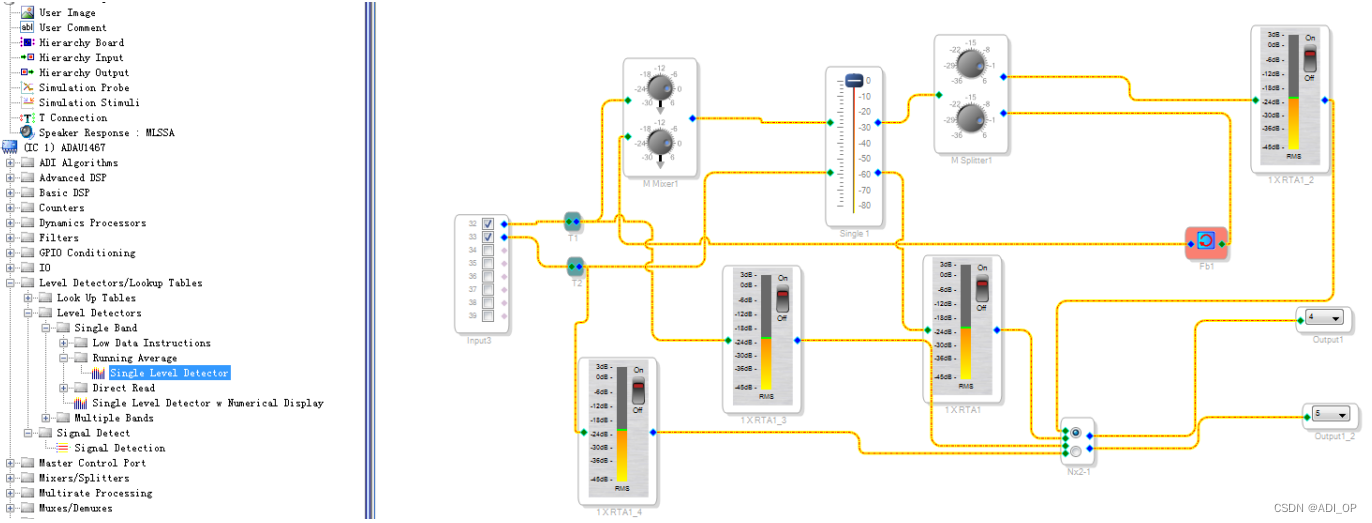

基于上一个个例程,我们来加几个电平显示的模块,直观的看看声音的情况:

打开这 4 个显示的开关,你会发现 3 个直通的电平,和经过反馈后的电平显示是完全不同的。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?