目录

前言

这个系列的文章是我备考软件设计师考试期间,通过学习B站上zst_2001老师的视频所整理的笔记。现在我已经顺利通过了考试,希望能将这些笔记分享给大家,希望能够帮助更多的人备考,一次通过考试。

上午题①计算机系统

一、CPU

-

计算机的基本硬更件系统由:运算器控制器,存储器,输入设备,输出设备

-

CPU分为运算器和控制器。CPU是硬件系统的核心。CPU(中央处理单元)

-

CPU功能: 程序控制,操作控制,时间控制(前三个是控制器), 数据处理(运算器)

-

运算器(4)个:算术逻辑单元,累加寄存器,数据缓冲寄存器,状态条件寄存器

- 算术逻辑单元(ALU):是运算器的重要组成部件,负责处理数据,对数据的算术运算(加减,乘除等)和逻辑运算(与,式,非,零值测试/两个值比较)

- 累加寄存器(AC):在ALU工作时,为ALU提供一个作区,暂存操作数和处理结果

- 数缓冲寄存器(DR):内存和外部设备数据传送的中转站

- 状态条件寄存器(PSW):标志

- 控制器:它不仅要保证程序的正确执行,而且能够处理异常事件

- 指令寄存器(IR):指令,操作码+地址码,指令暂存IR中,不可问,位数取决指长

- 程序计数器(PC): 自动计算指地址的个数(保存下一条),每次+1(顺序执行)。程序开始执行

- 地让寄存器(AR):保存当前CPU所访问的内存单元地

- 指令译码器(ID):对指中的操作码字段进行分析解释

- 不可访问指令寄存器

二、进制

- 计算机基本单位

| 位(比特) | bit (b) | 1B=8bit |

|---|---|---|

| 字节 | byte | |

| 千字节 | KB | 1KB=1024B |

| 兆字节 | MB | 1MB=124KB |

| 吉字节 | GB | 1GB=1024MB |

| 太字节 | TB | 1TB=1024GB |

最小的数据单位:b,最小的储存单位:byte

- 进制

①进制

二进制(B),0~1

十进制(D) ,0~9

八进制(O),0~7

十六进制(H),0~15

②n进制 —>十进制,按权展开求和

十进制 —>n进制,除n取余法

③进制加减法

加法逢n进1,减法借1当n

三、原码,反码,补码,移码

1.原码,反码,补码,移码

原码:最高位符号位,0为正,1为负

[+0]原=00000000,[-0]原=10000000

反码:

正数的反码与原码相同,负数的反码则是其绝对值按位求反(除符号位)

[+0]反=00000000,[-0]反=11111111

补码:

正数的补码与原码相同,负数的补码等于其反码的末尾加1

[+0]补=00000000,[-0]补=00000000(0有唯一的补码)

移码:

把补码的符号位取反

[+1]移=10000001,[-1]移=01111111

2.一个数的补码的补码是原码

3.浮点数

①小数点不固定,可移动,科学记数法

②二进制数N -->N=2ᴱ×F(E为阶码,F为尾码)

用E,F表示的数为浮点数,阶码为带符号的纯整数,尾码为带符号的纯小数

两个数比较,先对阶后加减小,小阶对大阶,尾码右移n位数

③浮点数所能表示的数值范围主要由阶码决定,数值的精度主要由尾数决定

④规格化:尾码的绝对值限定区间[0.5, 1]

如果浮点数的阶码(包括1位阶符)用R位的移码表示,尾数(包括1位数符)用M位补码表示

四、寻址

1.立即寻址:操作数包含在指令中

2.直接寻址:操作数存放在内存单元中班,指令直接给出操作数在内存的地址中

3.寄存器寻址:操作数存放在某一寄存器中,指令直接给出寄存器地址(指令->寄存器)

4.寄有器间接寻址:指令→寄存器名→操作数

5.间接寻址:指令→操作数地址→地址

6.扩大寻址控空间并提编程寻活性

7.寻址速度(快→慢)

立即寻址,寄存器寻址,直接寻址,寄存器间接寻址,间接寻址

五、校验码

1.奇偶校验码

码距至少为2,为只能检错,不能纠错,

看1的个数为奇数/偶数

只能检测奇数位出错,有奇数个数据位出错

2.海明码.

码距至少为3, 码距≥3可纠错

设数据位是n位,校验位是k位,则n和满足(2^k)-1≥n+k

3、循环冗余校验码

可检错但不能纠错,码距=2

在求CRC编码时,是模2运算,编码长度k十r(K位数据位,r位校验位)

六、精简指令集,复杂指令集

| 指令种类 | RISC | CISC |

|---|---|---|

| 指令复杂度 | 低(简单) | 高(复杂) |

| 指令长度 | 固定 | 变化 |

| 寻址方式 | 少 | 复杂多样 |

| 实现译码方式 | 硬布线控制逻辑(组合逻辑控制器) | 微程序控制技术 |

| 通用寄存器数量 | 多,大量 | 一般 |

| 流水线技术 | 支持 | 支持 |

七、流水线

①第一条指令的执行时间+(n-1)×最长段时间

②操作周期:最长时间段

③吞吐率:最长时间段的倒数

执行n条指令的吞吐率:n/①

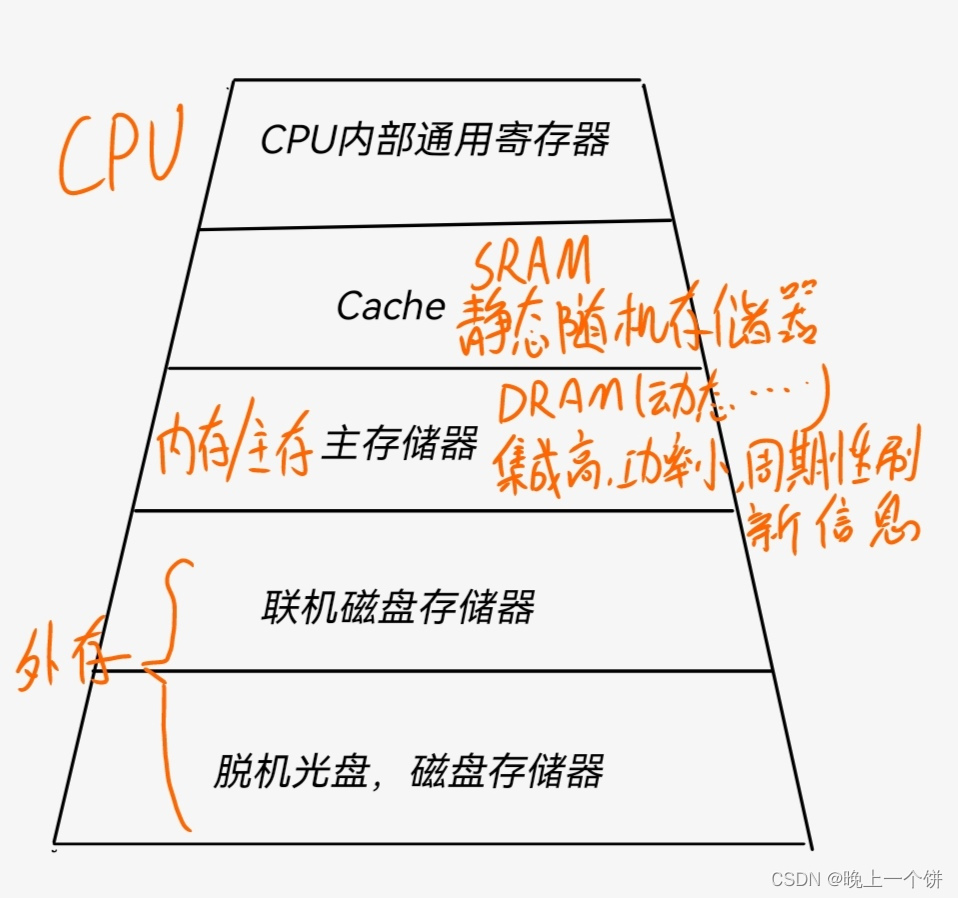

八、存储器

1.内存/主存:为CPU提供信息

2.分类:①读写存储器(RAM) ,读取/存入数据

②只读存储器(固定只读存储器ROM,可编程的只读存储器PROM,可擦除可编程的只读储存器EPROM,电可擦除可编程的只读储存器EEPROM,闪速存储器flash(以块为单位删除,信息不回丢失,代替ROM,不能代替主存/内存))

3.按访问方式

按内容访问的存储器–相联存储器

按寻址方式访问–随机存储器,顺序存储器,直接存储器

九、Cache

1.Cache告诉缓存:存放最活跃的程序数据,容量:几千字节~几兆字节,比内存快5~10倍,程序员看不见(透明的)

2.Cache部分拷贝内存副本信息

CPU先在cache中找,如果命中对cache寻址,如果没有命中按照替换原则决定主存的信息在Cache的哪一块

3.替换算法–尽可能提高Cache的命中

①随机替换算法

②先进先出算法

③近期最少使用算法

④优化替换算法

4.Cache命中率与Cache容量有关

容量越大,命中率越高(不是线性变化)

5.Cache中地址映像法

①直接映像:主存的块与Cache块的关系固定(冲突大)

②全相联映像:允许主存的任一块可调用Cache的任何一块空间中(冲突小)

③组相联映像:取下分组,组合组之间对接(冲突较小)

6.Cache与主存地址映像由硬件自动完成

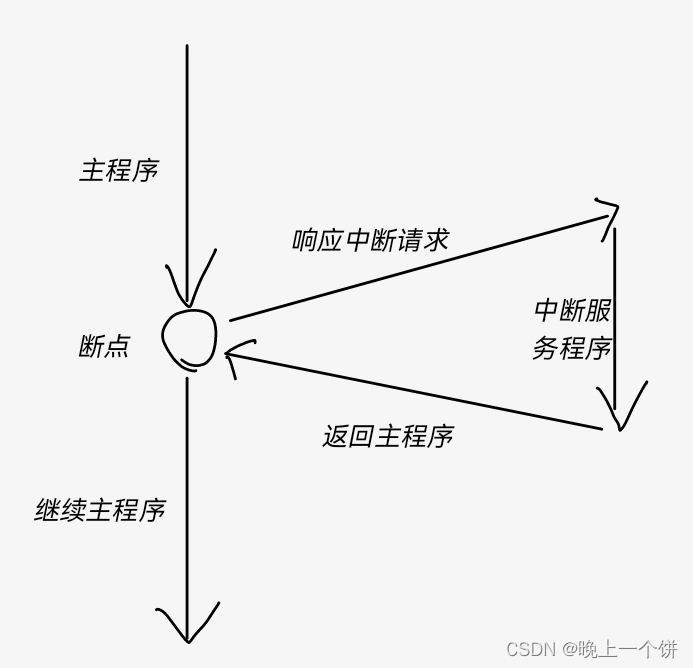

十、中断

1.中断:紧急暂停,处理完成之后继续执行

2.中断向量:提供中断服务程序的入口地址

3.中断响应时间:发出中断请求到进入中断服务程序

4.保护现场:返回来执行程序

十一、输入输出(I/O)控制方式

1.程序查询方式: (CPU与IO同步,IO与打印机设备异步)

特点:

- CPU和I/O(外设)只能串行工作,CPU需要一直轮询检查,长期处于忙等状态,CPU利用率低

- 一次只能读/写一个字

- CPU将数据存入内存

2.中断驱动方式

特点: - I/O设备通过中段信号主动报告IO操作已完成

- CPU和I/O(外设)可并行工作

- CPU利用率得到提升

- CPU将数据存入内存

- 一次只能读/写一个字

3.直接存储器存取方式(DMA)

特点: - CPU和IO(外设)可并行工作

- 仅在传送数据块的开始和结束时才需要CPU干预

- 由外设直接将数据放入内存(主存)

- 一次读写的单位为块,而不是字

系统总线周期,CPU是在一个总线周期响应DMA请求

4.总线

①系统总线:CPU主存及外设部件

②分类:数据总线,地址总线,控制总线

③常见总线 - PCI总线,微型机广泛采用内总线,采用并行传输方式(并行总线)

- SCSI总线(并行外总线)

④减少信息传输线的数量

十二、加密技术与认证技术

1.加密技术(被动)

①对称加密(私有密钥加密,共享密钥加密,私有,私有):加密和解密是同一把密钥,只有一把密钥

优点,加密解密速度很快,适合大量明文数据

缺点,密钥分发有缺陷

②非对称加密(公开密钥加密):加密和解密不是同一把密钥,一共有两把密钥(公钥,机密认证;私钥,解密签名)不能通过一把推出另一把

可防止窃听效果,密钥分发没有缺陷,加密速度很慢

③混和加密

2.认证技术(主动)

①摘要:明文通过Hash算法生成摘要,A将明文+摘要给B,B将明文+摘要经过Hash算法得到摘要,B将自己计算出的新摘要与A发送过来的摘要进行比较。

如果两个摘要完全一致,那么B可以认为接收到的明文没有被篡改。

如果两个摘要不匹配,则可能意味着明文在传输过程中被篡改或损坏。

②数字签名(防否认):A用自己的私钥进行签名,将A的公钥和签名发给B,B用A的公钥对签名进行认证,成功则正确

③数字证书

十三、加密算法

1.对称加密

DES,3DES,RC-5,IDEA,AES,RC4

2.非对称加密

RSA,ECC,DSA

3.Hash函数

MD5摘要算法----长度为128位

SHA-1安全散列算法

十四、可靠性公式

1.串联系统,n个串联 R=R₁R₂…Rₙ

2.并联系统,n个并联R=1-(1-R₁)(1-R₂)…(1-Rₙ)

658

658

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?