存储器(二)

文章目录

三、高速缓冲存储器

3.1 概述

3.1.1 为什么用Cache

👉问题的提出

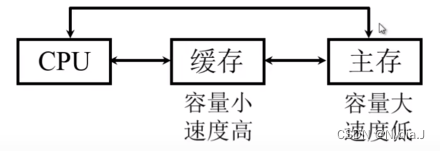

CPU执行速度远大于一般主存(DRAM)存取速度

为了避免CPU出现“空等”现象,在CPU和主存之间加入容量小,速度高的存储设备——Cache

主存可将CPU要取的信息提前送至缓存,一旦主存在与I/O设备交换时,CPU 可直接从缓存中读取所需信息

程序访问的局部性原理

- 时间的局部性:当前正在使用的指令和数据在不久的将来还会被使用到,那么当前正在使用的指令和数据需要放到Cache中,将来再用的时候直接从Cache中取出来

- 空间的局部性:当前正在使用的指令和数据在不久的将来相邻的指令或数据会被用到,那么当前正在使用的指令和数据需要放到Cache中,同时将相邻的指令和数据也放到Cache中

3.1.2 工作原理

👉工作原理

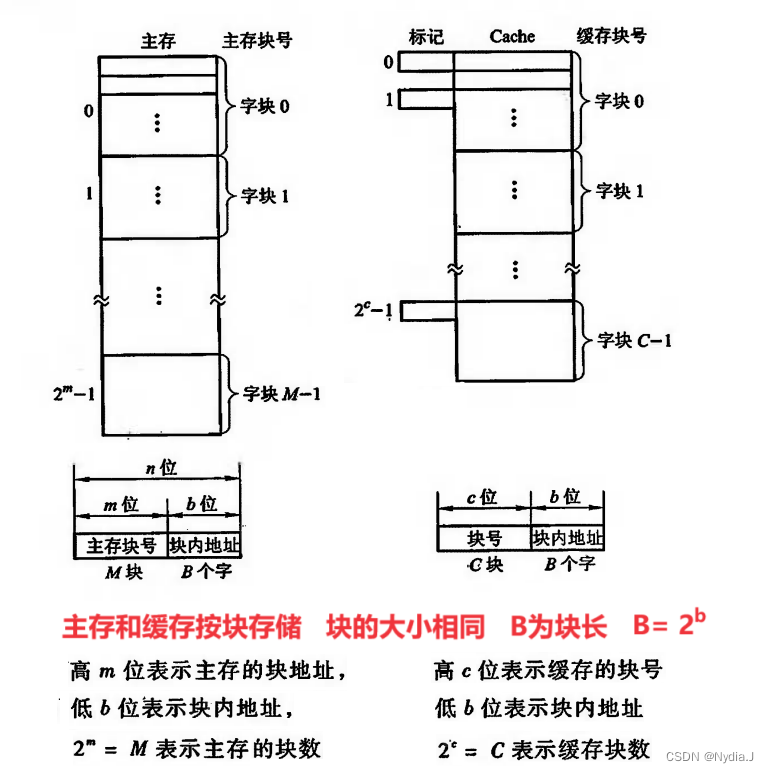

缓存块数C远小于主存块数M

一个块在内存和Cache中进行传送的时候是整体进行传送块内字节的顺序不会发生任何变化,所以主存和Cache的块内偏移地址的值是完全相同的,

Cache上的标记,标记了主存块和Cache块之间的对应关系如果一个主存块把它调用到Cache中,就可把主存块号写入到标记中。当CPU给出一个内存地址,希望能在Cache中访问这个地址,首先就会确定这个块是否已经被送到了Cache当中即比较给出的的地址的主存块号与Cache中的标记,如果和某一个Cache的标记相等,且该Cache块有效,则可直接从此Cache中获得想要访问的主存数据。

👉命中和不命中

- 命中:要访问的主存块已经调入缓存,CPU在缓存中能够取到相应得数据或指令,就称为命中。如果命中,则主存块与缓存块就建立了对应关系。

- 未命中:要访问的主存块没有调入缓存,CPU必须到主存中获得相应得数据或指令,就称为未命中。如果未命中,则主存块与缓存块未建立了对应关系

👉Cache的命中率

命中率与Cache的容量与块长有关。

CPU取若干次数据,从cache中读取了N1次,从主存中读取了N2次:命中率 = N1 / (N1 + N2)

一般每块可取 4 ~ 8 个字,块长取一个存取周期内从主存调出的信息长度

采用16体交叉,每个存储体保存一个字,块长就是16个存储字,在一个存储周期中,可以把16个存储字取出放到cache中

CRAY_1 16体交叉 块长取 16 个存储字 IBM 370/168 4体交叉 块长取 4 个存储字 👉 Cache-主存的效率

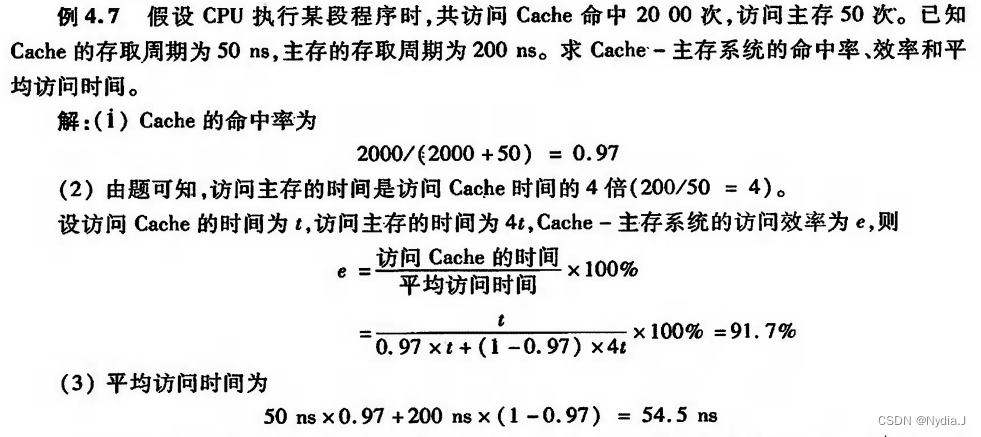

效率e与命中率有关,命中率h越接近1越好

e = 访问 C a c h e 的时间 平均访问时间 × 100 % e=\frac{访问Cache的时间}{平均访问时间}×100\% e=平均访问时间访问Cache的时间×100%

设Cache命中率为h,访问Cache的时间为tc,访问主存的时间为tm ,则

e = t c h × t c + ( 1 − h ) × t m × 100 % e=\frac{t~c~}{h\times t~c~ + (1-h)\times t~m~}×100\% e=h×t c +(1−h)×t m t c ×100% 可得

t c t m ≤ e ≤ 1 \frac{t~c~}{t~m~} \leq e \leq 1 t m t c ≤e≤1

3.1.3 Cache的基本结构

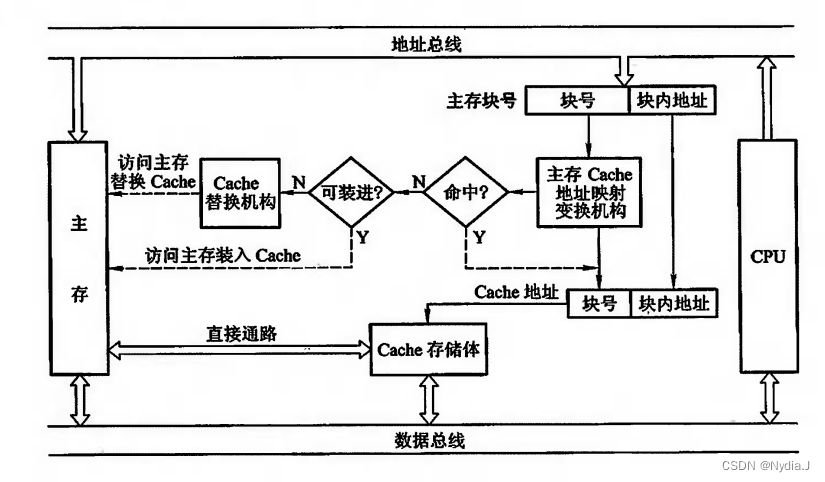

- CPU发出一个地址,包括块号和块内地址,发给主存Cache地址映射变换机构

- 如果命中,就将主存地址转化为Cache地址(由于偏移地址(低位地址)一致,所以基本上是主存块号(高位地址)到Cache块号的转换),从Cache存储体中找到对应的字,然后通过数据总线送到CPU,完成一次读写过程;

- 如果没有命中,需要查一下Cache中是否有空间可以装入

- 如果有:访问主存,把主存块装入到Cache中

- 如果没有:启用Cache替换机构,根据替换算法决定Cache中哪一个块写回到主存或者作废,并将主存要用的块写入到Cache这个块中

将主存地址映射到缓存中定位称为地址映射,将主存地址转换成缓存地址称为地址变换

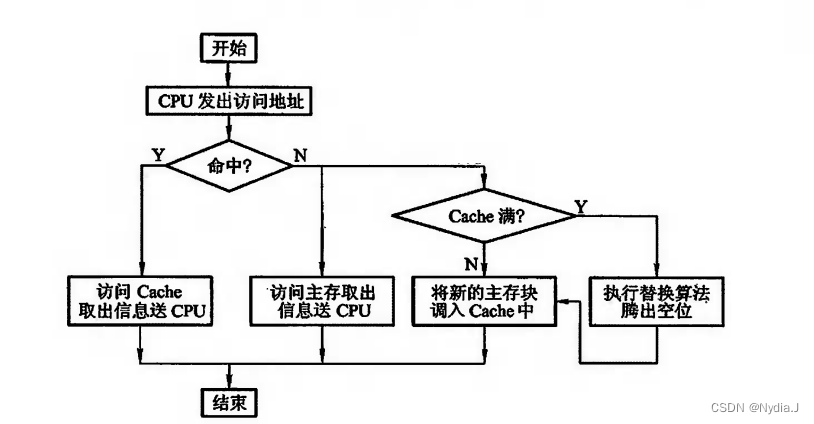

3.1.4 Cache的读写操作

读操作

写操作

-

写/存直达法(Write-through):

写操作时数据既写入Cache又写入主存,时刻保存Cache内容和主存内容一致,并且Cache块内容从Cache中退出的的时候,不需要对主存执行写操作。写操作的的时间就是访问主存的时间

优点:Cache和主存一直保持一致

缺点:可能造成CPU对同一个内存单元反复写

-

写/拷回法(Write-back):

写操作时只把数据写入Cache而不写入主存,当Cache数据被替换出去时才写回主存,允许一段时间中,主存与Cache内容不一致优点:修改数据只在Cache中修改速度快,减少了主存的写入操作

缺点:在多处理器的情况下,各个处理器有各自的Cache,内存的一个块在各个处理器的Cache中都有副本,会导致各个副本之间的一致性问题。

为了识别 Cache 中的数据是否与主存一致,Cache 中的每一块要增设一个标志位,该位有两个状态:“清”(表示未修改过,与主存一致)和“浊”(表示修改过,与主存不一致)。在Cache 替换时,“清”的Cache块不必写回主存,因为此时主存中相应块的内容与Cache 块是一致的。在写 Cache 时,要将该标志位设置为“浊”,替换时此Cache块要写回主存,同时要使标志位为“清”。

3.1.5 Cache改进

-

增加Cache的级数

片载Cache(单一缓存)- 是指在CPU和主存之间只设一个缓存且把这个缓存直接与CPU制作在同一个芯片内。

片外Cache(二级缓存)- 在主存与片内缓存之间再加一级缓存,由静态RAM组成。而且不使用系统总线作为片外缓存与CPU之间的传送路径,使用一个独立的数据路径,以减轻系统总线的负担。 -

统一缓存和分立缓存

统一缓存:数据与指令统一放入Cache----冯氏结构

分立缓存:Cache分为指令Cache和数据Cache与机器对指令执行的控制方式有关。当采用超前控制或流水线控制方式时,一般都采用分立缓存。

所谓超前控制,是指在当前指令执行过程尚未结束时就提前将下一条准备执行的指令取出’称为超前取指或指今预取。所谓流水线控制实质上是多条指令同时执行

3.2 Cache-主存的地址映射

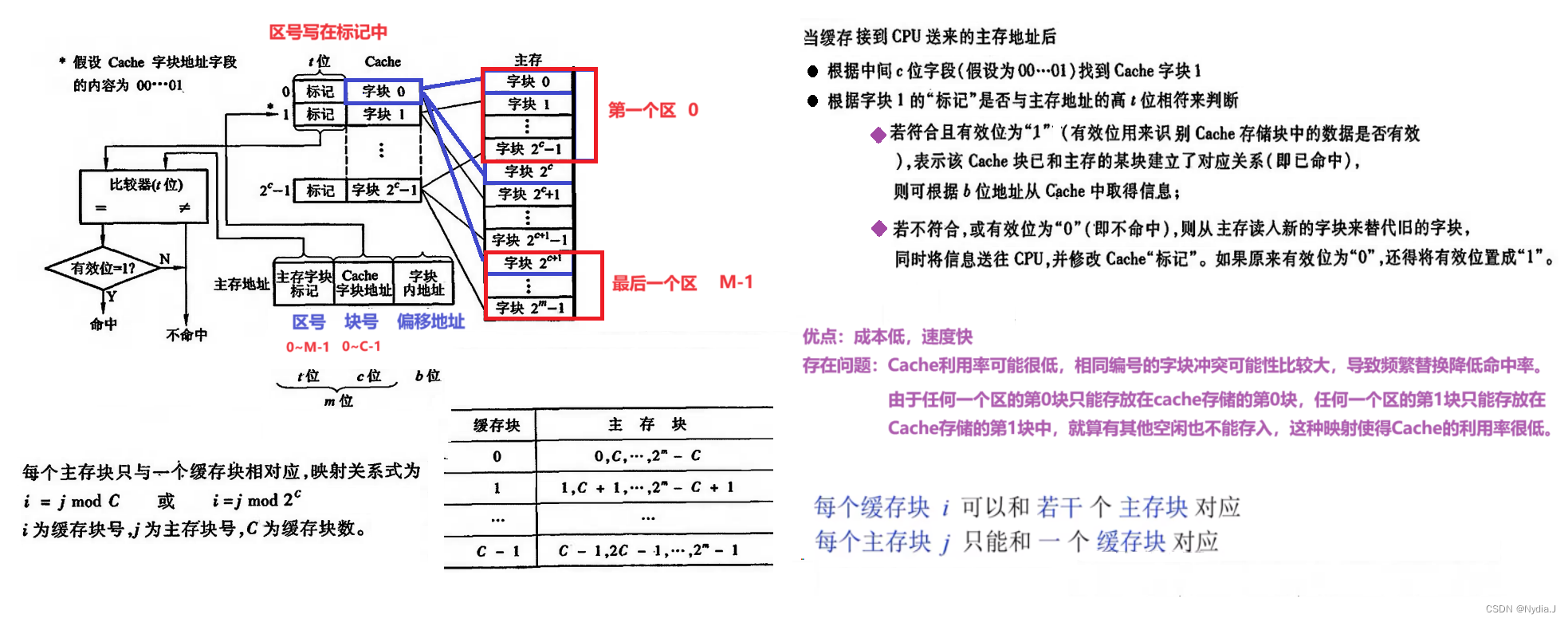

3.2.1 直接映射

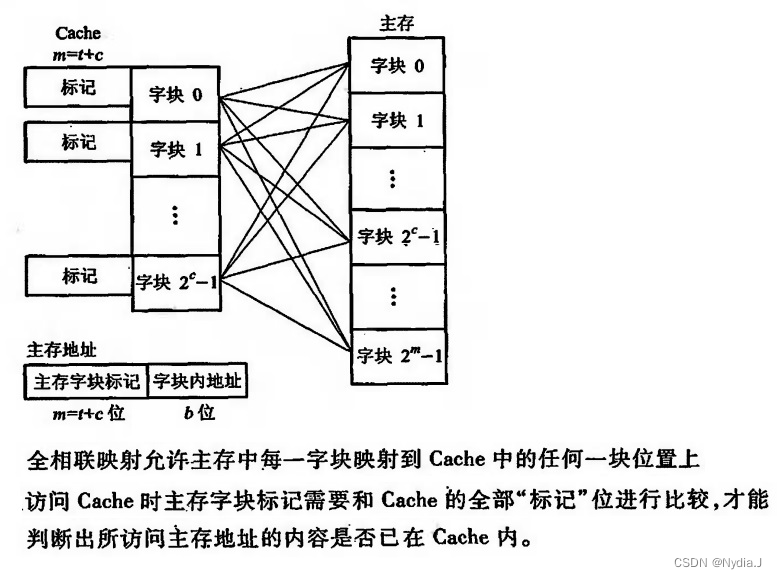

3.2.2 全相联映射

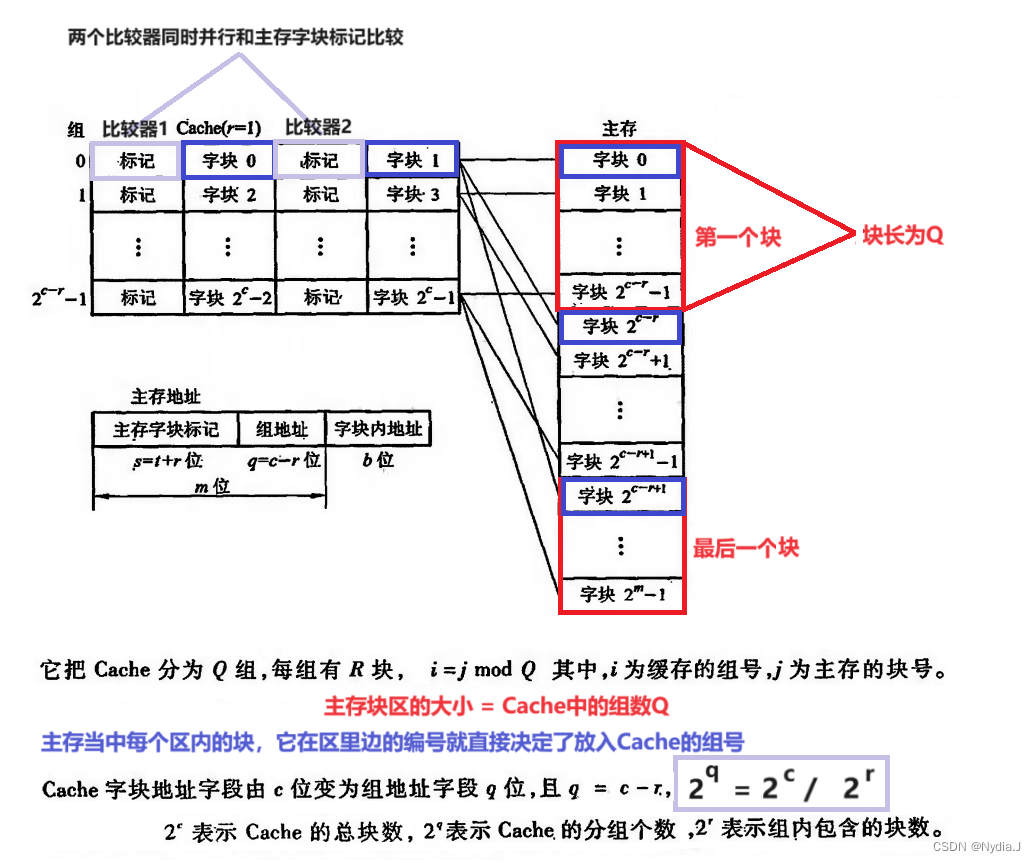

3.2.3 组相联映射

Cache中所有的块分成一组即为全相联,Cache中每一组只有唯一一块即为直接相联

距离CPU近的Cache层次 —— 需要高速度 —— 直接相联 或 路数比较少的组相联

距离CPU远的Cache层次 —— 需要Cache利用率高—— 全相联

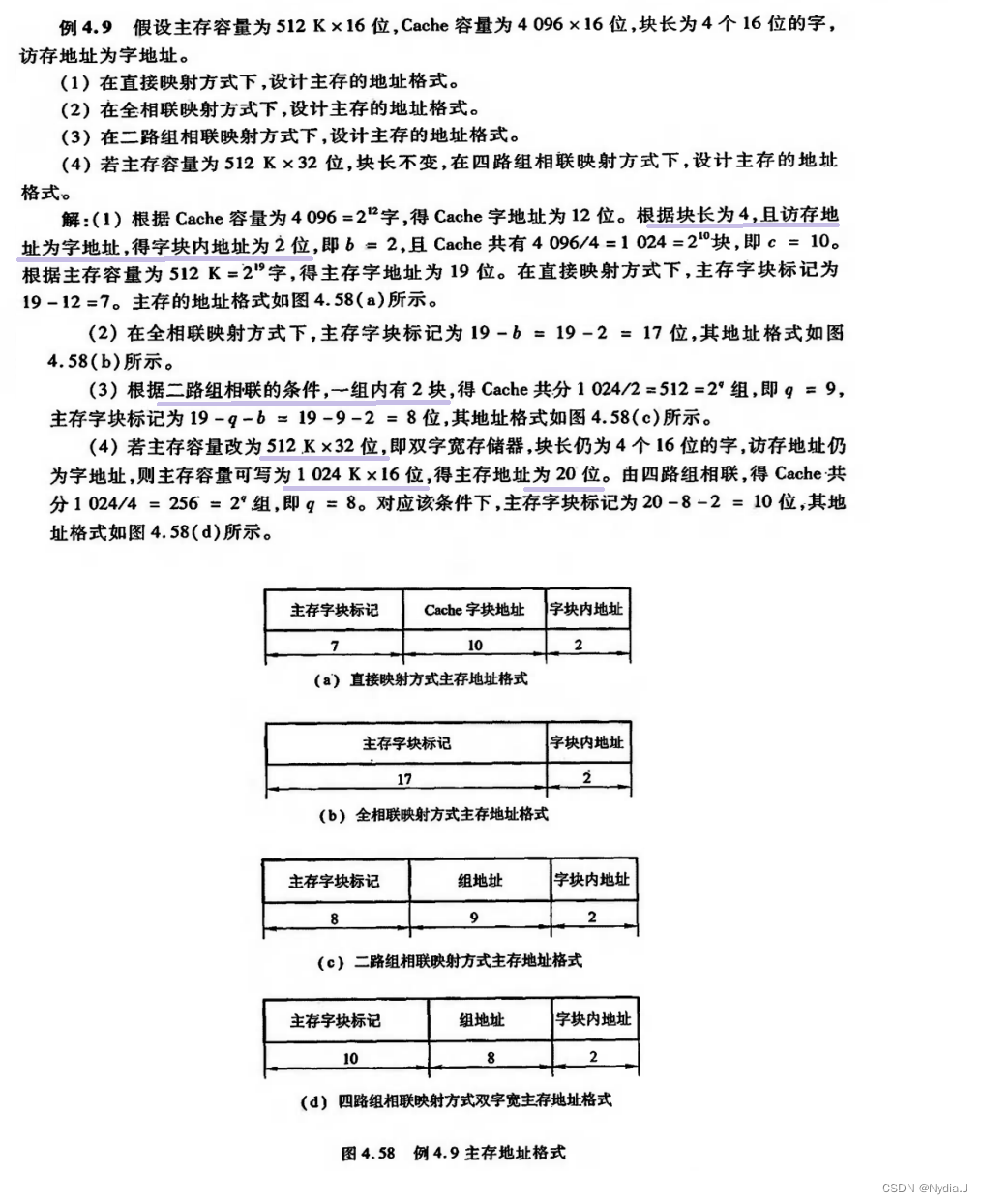

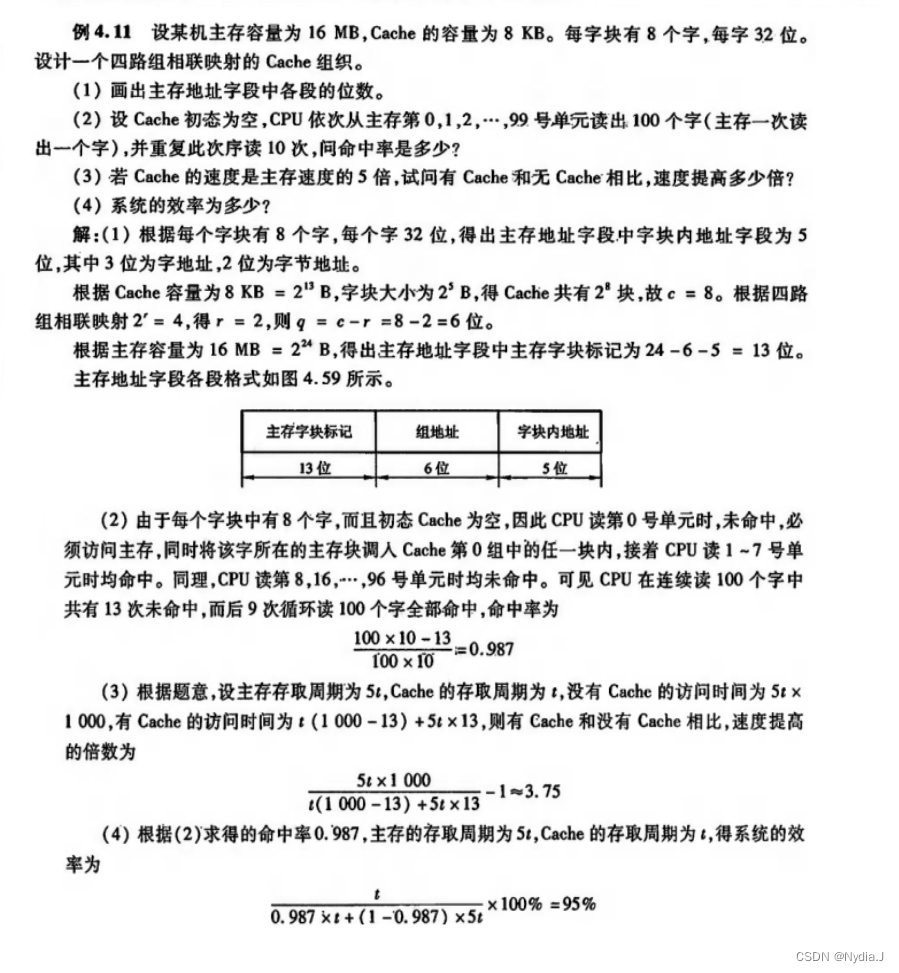

3.2.4 例题

3.3 替换算法

-

先进先出(First-In-First-Out,FIFO)算法

FIFO算法选择最早调入Cache的字块进行替换,它不需要记录各字块的使用情况,比较容易实现,开销小,但没有根据访存的局部性原理,故不能提高 Cache 的命中率。

-

近期最少使用(Least Recently Used,LRU)算法

LRU算法比较好地利用访存局部性原理,替换出近期用得最少的字块。它需要随时记录Cache 中各字块的使用情况,以便确定哪个字块是近期最少使用的字块。它实际是一种推测的方法,比较复杂,一般采用简化的方法,只记录每个块最近一次使用的时间。

LRU算法的平均命中率比FIFO的高。

四、辅助存储器

4.1 概述

⭐️辅助存储器作为主存的后援设备又称为外部存储器,简称外存

⭐️辅助存储器具有容量大、速度慢、价格低、可脱机保存信息等特点,属“非易失性”存储器。

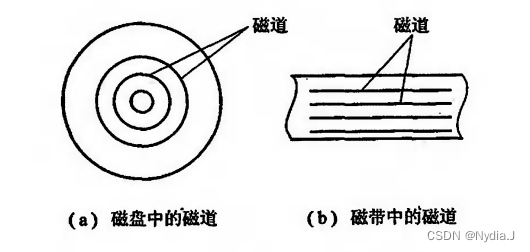

⭐️磁表面存储器是在不同形状(如盘状、带状等)的载体上涂有磁性材料层, 工作时, 靠载磁体高速运动, 由磁头在磁层上进行读/写操作, 信息被记录在磁层上, 这些信息的轨迹就是磁道。磁盘的磁道是一个个同心圆, 磁带的磁道是沿磁带长度方向的直线。

⭐️磁表面存储器的主要技术指标

记录密度:通常是指单位长度内所存储的二进制信息量。

磁盘存储器用道密度和位密度表示;磁带存储器则用位密度表示。

磁盘沿半径方向单位长度的磁道数为 道密度,单位是tpi(Track Per Inch,道每英寸)或tpm(道每毫米)。

相邻两条磁道中心线之间的距离称为道距道密度 Dt = 道距P的倒数 Dt = 1 P \frac{1}{P} P1

单位长度磁道能记录二进制信息的位数,称为 位密度或线密度,单位是bpi(Bits Per Inch,位每英寸)或bpm(位每毫米)。

磁盘的位密度 Db = f t π d m i n =\frac{f~t~}{π d~min~} =πd min f t 越往外位密度越低

ft - 每道总位数 dmin - 同心圆中最小直径

存储容量:外存所能存储的二进制信息总数量,一般以位或字节为单位。

C = n × k × s C为存储总容量, n为存放信息的盘面数, k为每个盘面的磁道数, s为每条磁道上记录的二进制代码数。

磁盘有格式化容量和非格式化容量两个指标。非格式化容量是磁表面可以利用的磁化单元总数。格式化容量是指按某种特定的记录格式所能存储信息的总量,即用户可以使用的容量,它一般为非格式化容量的60%~70%。

平均寻址时间

磁盘采取直接存取方式,寻址时间分为两个部分,

其一是磁头寻找目标磁道的找道时间 寻道时间 ts

其二是找到磁道后,磁头等待欲读/写的磁道区段(给定的扇区)旋转到磁头下方所需要的 等待时间 tw

由于从最外圈磁道找到最里圈磁道和寻找相邻磁道所需时间是不等的,而且磁头等待不同区段所花的时间也不等,因此,取其平均值,称为 平均寻址时间 Ta,它是平均找道时间 tsa 和平均等待时间 twa 之和:

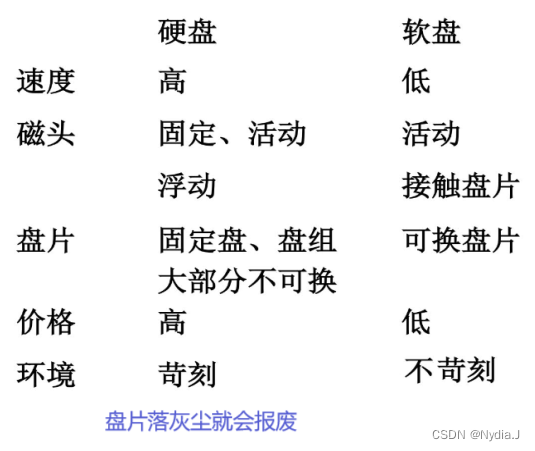

T a = t sa + t wa = t s m i n + t s m a x 2 \frac{t~smin~ + t~smax~}{2} 2t smin +t smax t w m i n + t w m a x 2 \frac{t~wmin~ + t~wmax~}{2} 2t wmin +t wmax 硬磁盘的平均寻址时间比软磁盘的平均寻址时间短,所以硬磁盘存储器比软磁盘存储器速度快。

数据传输率

Dr是指单位时间内磁表面存储器向主机传送数据的位数或字节数,它与位密度Db,和记录介质的运动速度V有关:

Dr = Db × V

误码率

从辅存读出时,出错信息位数和读出信息的总位数之比。

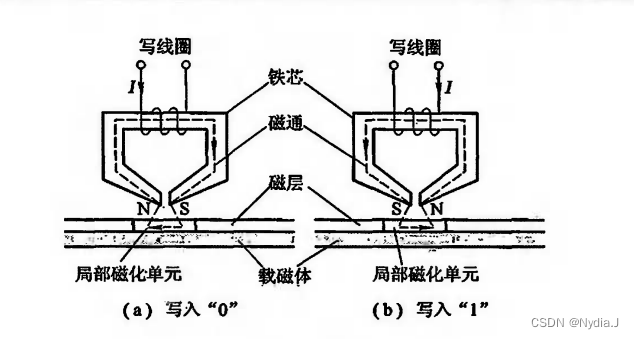

4.2 磁记录原理和记录方式

对写入线圈输入一定方向和大小的电流,使磁头导磁体磁化,产生一定方向和强度的磁场。由于磁头与磁层表面间距非常小,磁力线直接穿透磁层表面,将对应磁头下方的微小区域磁化(称为磁化单元)。可以根据写人驱动电流的不同方向,使磁层表面被磁化的极性方向不同,以区别记录“0”或“1”。

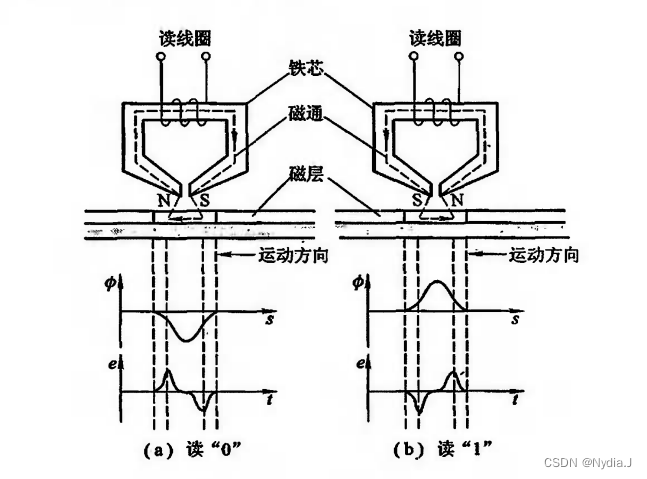

读出时,记录介质在磁头下方匀速通过,磁头相对于一个个被读出的磁化单元作切割磁力线的运动,从而在磁头读线圈中产生感应电势e,其方向正好和磁通的变化方向相反。由于原来磁化单元的剩磁通φ的方向不同,感应电势方向也不同,便可读出“1”或“0”两种不同信息。

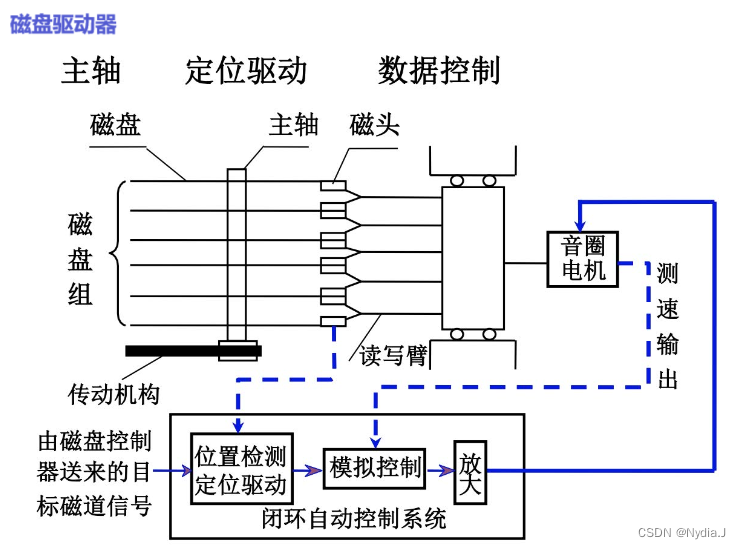

4.3 硬磁盘存储器

-

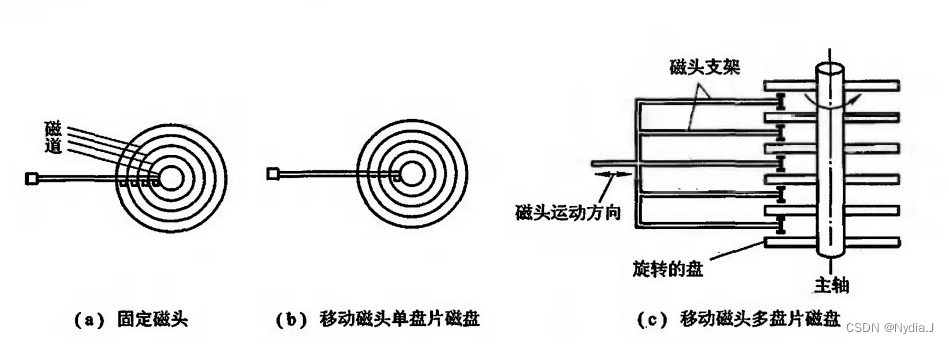

按磁头的工作方式可分为固定磁头磁盘存储器和移动磁头磁盘存储器

-

固定磁头的磁盘存储器,其磁头位置固定不动,磁盘上的每一个磁道都对应一个磁头,盘片也不可更换。

其特点是省去了磁头沿盘片径向运动所需寻找磁道的时间,存取速度快,只要磁头进人工作状态即可进行读写操作。

-

移动磁头的磁盘存储器在存取数据时,磁头在盘面上作径向运动,这类存储器可以由一个盘片组成,也可由多个盘片装在一个同心主轴上,每个记录面各有一个磁头。

-

-

按磁盘是否具有可换性又可分为可换盘磁盘存储器和固定盘磁盘存储器

- 可换盘磁盘存储器是指盘片可以脱机保存。

- 固定盘磁盘存储器是指磁盘不能从驱动器中取下,更换时要把整个头盘组合体一起更换(常用)

-

硬磁盘存储器的结构

4.4 软磁盘存储器(弃用)

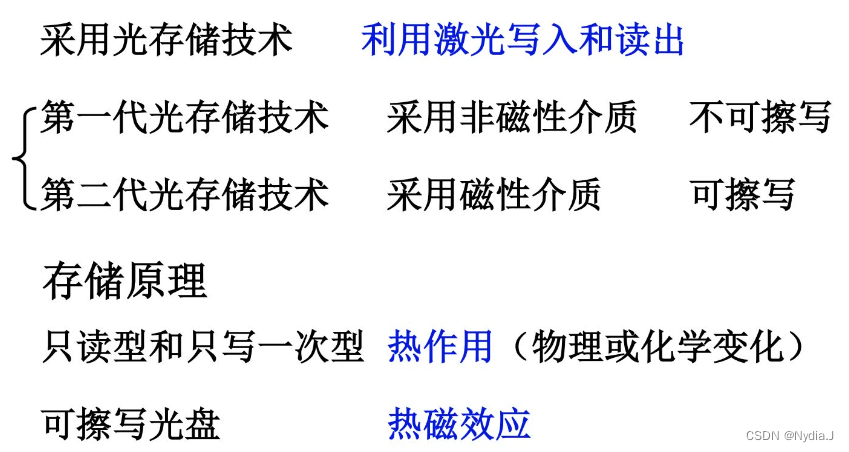

4.5 光盘存储器

五、虚拟存储器

5.1 虚拟存储器

是主存-辅存层次的,虚拟存储器主要是由操作系统实现

- 实地址(物理地址):计算机物理内存的访问地址。

- 虚地址(逻辑地址):用户编程时使用的地址。

- 再定位:程序进行虚地址到实地址转换的过程。

| 主存 - 辅存 | 主存-Cache | |

|---|---|---|

| 信息块 | 页、段、段页 | 块 |

| 侧重点 | 主存容量 | 主存与CPU速度差异 |

| 数据通路 | CPU与辅存、虚存无直接通路 | CPU与Cache、主存有直接通路 |

| 透明性 | 对程序员不透明 | 对程序员透明 |

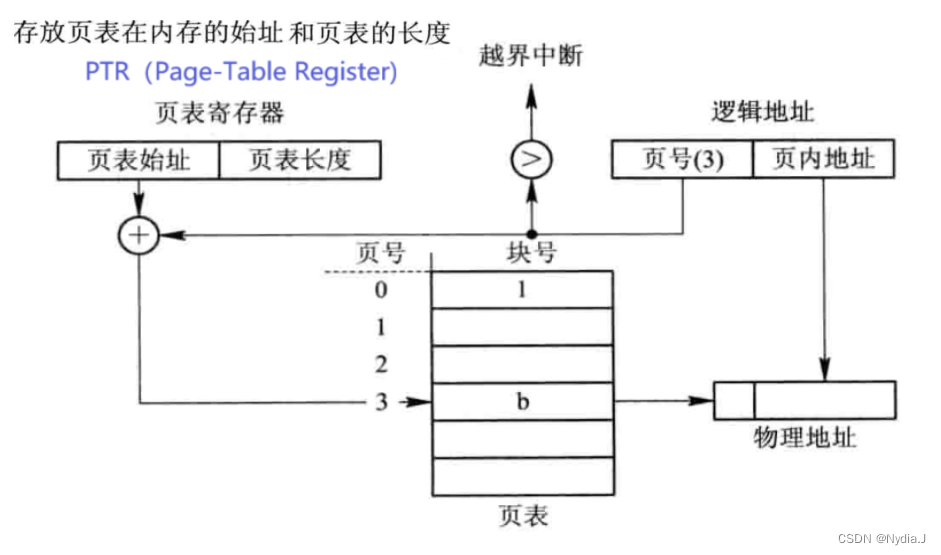

5.2 页式虚拟存储器

将地址空间分为若干个固定大小的区域,称为“页”或“页面”。

-

虚页/逻辑页:虚地址空间被分成的页

-

实页/物理页:实地址空间被分成同样大小的页

-

页表:虚拟地址与物理地址映射关系的索引表

-

逻辑地址到物理地址的变换:

- 当进程要访问某个逻辑地址中的数据时,分页地址变换机构会自动地将有效地址(相对地址)分为页号和页内地址两部分,

- 再以页号为索引去检索页表。查找操作由硬件执行。

- 在执行检索之前,先将页号与页表长度进行比较,如果页号大于或等于页表长度,则表示本次所访问的地址已超越进程的地址空间。于是,这一错误将被系统发现,并产生一地址越界中断。

- 若未出现越界错误,则将页表始址与页号和页表项长度的乘积相加,便得到该表项在页表中的位置,于是可从中得到该页的物理块号,将之装入物理地址寄存器中。

- 与此同时,再将有效地址寄存器中的页内地址送入物理地址寄存器的块内地址字段中。

-

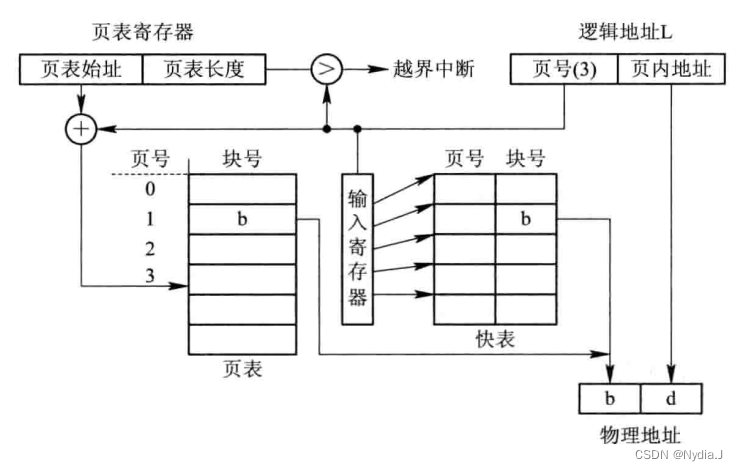

联想寄存器(Associative Memory)/快表/TLB(Translation Look aside Buffer)

出现背景:由于页表是存放在内存中的,这使CPU在每存取一个数据时,都要两次访问内存。第一次是访问内存中的页表,从中找到指定页的物理块号,再将块号与页内偏移量W拼接,以形成物理地址。第二次访问内存时,才是从第一次所得地址中获得所需数据(或向此地址中写入数据)。因此,采用这种方式将使计算机的处理速度降低近1/2。

地址变换过程是:

- 在CPU给出有效地址后,由地址变换机构自动地将页号P送入高速缓冲寄存器,

- 并将此页号与高速缓存中的所有页号进行比较,若其中有与此相匹配的页号,便表示所要访问的页表项在快表中。可直接从快表中读出该页所对应的物理块号,并送到物理地址寄存器中。

- 如在快表中未找到对应的页表项,则还须再访问内存中的页表,找到后,把从页表项中读出的物理块号送往地址寄存器; 同时,再将此页表项存入快表的一个寄存器单元中,亦即,重新修改快表。但如果联想寄存器已满,则OS 必须找到一个老的且已被认为是不再需要的页表项,将它换出。

5.3 段式虚拟存储器

将地址空间分为若干个大小不同的段,每段可定义一组相对完整的信息

-

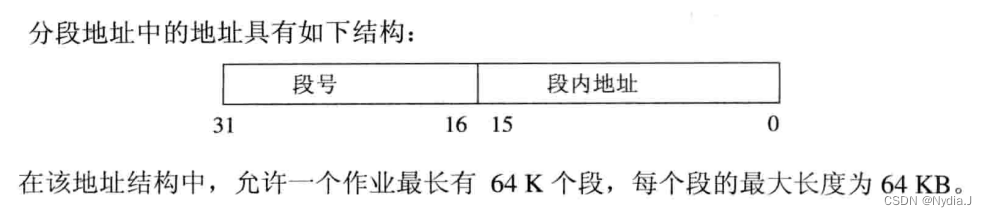

分段地址结构

-

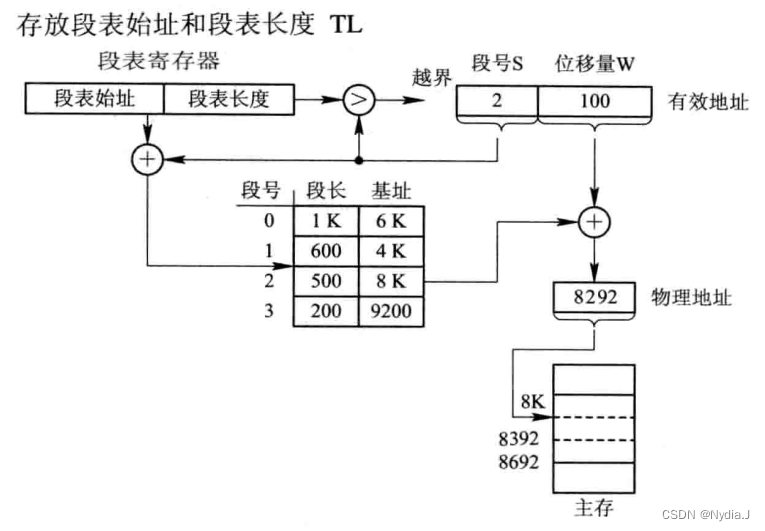

段表:记录了该段在内存中的起始地址(又称为“基址”)和段的长度

-

地址变换过程:

- 在进行地址变换时,系统将逻辑地址中的段号与段表长度TL,进行比较。

- 若S>TL,表示段号太大,是访问越界,于是产生越界中断信号。

- 若未越界则根据段表的始址和该段的段号,计算出该段对应段表项的位置,从中读出该段在内存的起始地址。

- 然后,再检查段内地址d是否超过该段的段长SL。

- 若超过,即d>SL,同样发出越界中断信号。

- 若未越界,则将该段的基址d与段内地址相加,即可得到要访问的内存物理地址。

5.4 段页式虚拟存储器

-

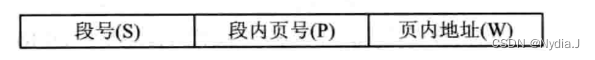

段页式系统的基本原理是分段和分页原理的结合,即先将用户程序分成若干个段,再把每个段分成若干个页,并为每一个段赋予一个段名。

-

地址结构由段号、段内页号及页内地址三部分所组成

-

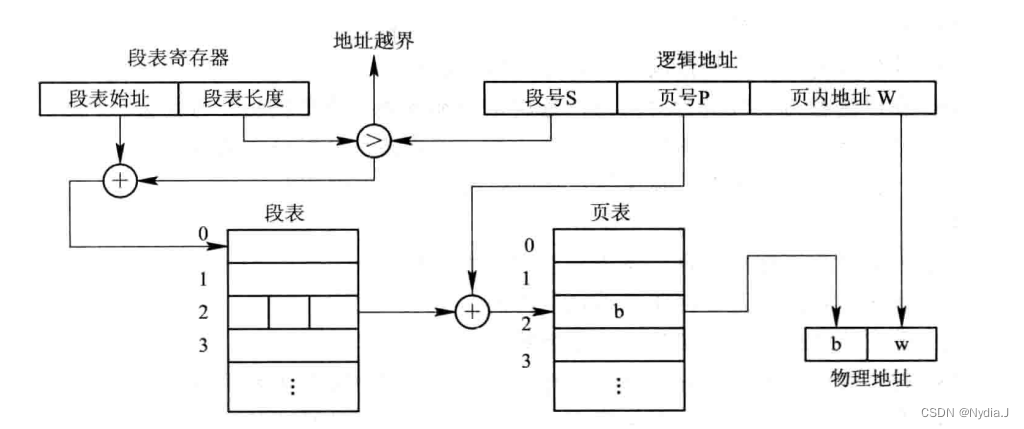

地址变换过程:

- 段表寄存器,其中存放段表始址和段长 TL。

- 进行地址变换时,首先利用段号S,将它与段长TL进行比较。

- 若S<TL,表示未越界,于是利用段表始址和段号来求出该段所对应的段表项在段表中的位置,

- 从中得到该段的页表始址,并利用逻辑地址中的段内页号P来获得对应页的页表项位置,从中读出该页所在的物理块号b,

- 再利用块号b和页内地址来构成物理地址。

参考:

教材:计算机组成原理 (唐朔飞).pdf

计算机操作系统(第四版) (汤小丹) .pdf

视频:https://www.bilibili.com/video/BV1t4411e7LH?p=1&vd_source=a89593e8d33b31a56b894ca9cad33d33

31万+

31万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?