教材:数字设计基础与应用 第二版 邓元庆 关宇 贾鹏 石会 编著 清华大学出版社

源文档高清截图在后

第2章 组合逻辑电路分析与设计

2.1 集成逻辑门

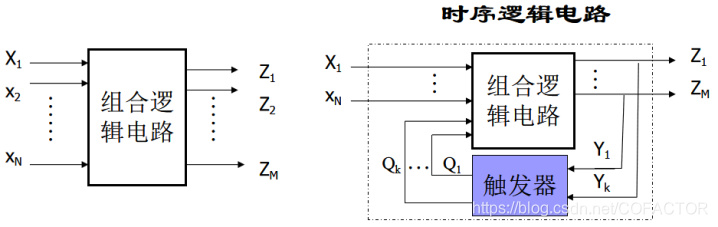

1、数字电路从结构和功能上可以分为组合逻辑电路和时序逻辑电路。组合逻辑电路是由逻辑门级联而成的,没有反馈通道,功能可以用真值表完全描述,电路为开环结构,无反馈,在任意时刻的输出完全由该时刻的输入决定,与以往的输入无关。而时序逻辑电路包含记忆元件,电路为闭环结构,有反馈,输出信号的取值与输入信号的历史有关。

2、数字设计包括低层次的物理级和晶体管设计、中层次的门级和模块级设计,以及高层次的系统级设计。

3、数字芯片的集成度分为六类:小规模集成电路(small scale integration,SSI)、中规模集成电路(medium scale integration,MSI)、大规模集成电路(large scale integration,LSI)、超大规模集成电路(very large scale integration,VLSI)、特大规模集成电路(ultra scale integration,ULSI)和巨大规模集成电路(gigantic scale integration,GLSI)。

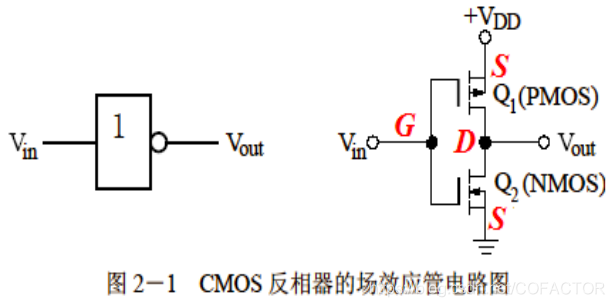

4、集成逻辑门是最基本的数字集成电路,按制作工艺与工作机理的不同可以分为TTL、CMOS和ECL三种。TTL(transistor-transistor logic,晶体管-晶体管逻辑)是由双极型晶体三极管构成的数字集成电路;ECL(emitter coupled logic,发射极耦合逻辑)也是由双极型晶体三极管构成的数字集成电路,在高速应用领域一枝独秀。而CMOS(complementary metal-oxide semiconductor)则是由单极型场效应管构成的集成电路,已经基本取代TTL,占领绝大部分世界IC市场。

5、最简单的集成逻辑门是CMOS非门,由两个互补的场效应管构成。

场效应管(field effect transistor,FET)是一种用输入电压控制输出电流的半导体器件,只有一种载流子(指可以自由移动的带有电荷的物质微粒,如电子和离子)——多子(多数载流子)参与导电,又称单极型晶体管。MOS(metal-oxide semiconductor)晶体管是FET的一种,全称金属-氧化物-半导体场效应晶体管(MOSFET)。MOS器件通过隔离的栅极电压控制沟道导电实现开关功能。NMOS(N沟道MOS管)的结构是在P型半导体上制作两个N型电极(源极S和漏级D)和一个隔离的金属栅极G。栅源电压大于开启电压(阈值电压)时,在源极和漏级之间产生N型导电沟道,源漏电阻较小(几百Ω以内),称为导通。栅源电压小于开启电压时,导电沟道消失,源漏电

本文介绍了数字设计的基础,重点关注集成逻辑门,包括TTL、CMOS和ECL类型。CMOS门电路因其低功耗、宽电压范围和高逻辑摆幅而具有优势。集成逻辑门的主要电气指标包括逻辑电平、噪声容限、驱动能力和功耗等。CMOS电路具有噪声容限大、输入阻抗高和温度稳定性好等优点。

本文介绍了数字设计的基础,重点关注集成逻辑门,包括TTL、CMOS和ECL类型。CMOS门电路因其低功耗、宽电压范围和高逻辑摆幅而具有优势。集成逻辑门的主要电气指标包括逻辑电平、噪声容限、驱动能力和功耗等。CMOS电路具有噪声容限大、输入阻抗高和温度稳定性好等优点。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?