I/O接口是位于系统与外设间、用来协助完成数据传送和控制任务的逻辑电路。

I/O接口的典型结构

CPU与外设主要有数据、状态和控制信息需要相互交换,于是从应用角度看内部:

(1)数据寄存器

输入数据寄存器:保存外设给CPU的数据

输出数据寄存器:保存CPU给外设的数据

(2)状态寄存器

保存外设或接口电路的状态

(3)控制寄存器

保存CPU给外设或接口电路的命令

I/O接口(电路)的主要功能

地址译码和设备选择

接口电路占用的I/O端口有两类形式。【16位I/O端口地址最多可寻址64K个端口地址】

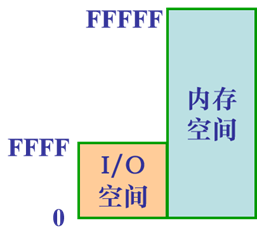

独立编址方式(或称I/O映射编址)

I/O地址空间独立于存储地址空间,如8086/8088

优点:

- I/O端口地址不占用存储器地址空间

- 控制和地址译码电路相对简单

- 专门的I/O指令使程序清晰易读

缺点:

- I/O指令没有存储器指令丰富

- 要求提供I/O读写控制信号,增加了复杂性

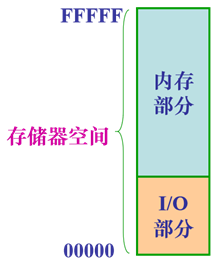

统一编址方式(或称存储器映射编址)

I/O与存储器共享一个地址空间,如M6800,ARM【位置自己定义,不共知】

优点:

- 不需要专门的I/O指令

- I/O数据存取与存储器数据存取一样灵活

- 外设数目几乎不受限制,而只受总存储容量的限制

- 读写控制逻辑较简单

缺点:

- I/O端口要占去部分存储器地址空间

- 程序中不易分清访问内存还是访问外设

信息转换【并串、DA/AD转换;数据格式;电平转换】

- 数据信息(Data)

- 数字量:以二进制形式表示的数

- 模拟量

- 开关量:表示两个状态的量,可用1位二进制数表示

- 状态信息(Status)

反映外设当前所处的工作状态,是外设通过接口传送给CPU的,如READY,BUSY

- 控制信息(Control)

CPU通过接口传送给外设的信息,如启停

对外设的控制与监测

- 主要体现在引脚上,分成两侧信号。

- 面向CPU一侧的信号:用于与CPU连接,主要是数据、地址和控制信号

- 面向外设一侧的信号:用于与外设连接,提供的信号五花八门;功能定义、时序及有效电平等差异较大

中断或DMA管理(重点)

详情看中断章和后面内容

可编程

接口需要进行物理连接,还需要编写接口软件。接口软件主要完成:

- 初始化——设定芯片工作方式等

- 数据交换——管理、控制、驱动外设,负责外设和系统间信息交换

错误检测

8088/8086的I/O端口

- 程序员能看到的外设是端口。

- 8088/8088CPU用于寻址外设端口的地址线为16根。

- 端口最多为216=65536(64K)个

- 端口号为0000H ~ FFFFH

- 每个端口用于传送一个字节的外设数据。

- 实际上PC/XT机只用了1024个端口:

- 端口号为0000H ~ 03FFH

- 地址线只用10条A0~A9

输入输出传送方式

外设与微机之间的信息传送实质是CPU与接口之间的信息传送。

无条件传送方式【前提:外设必须随时就绪】

特点:直接与外设进行数据传送。

适合于简单设备,如LED数码管、按键或按钮等。

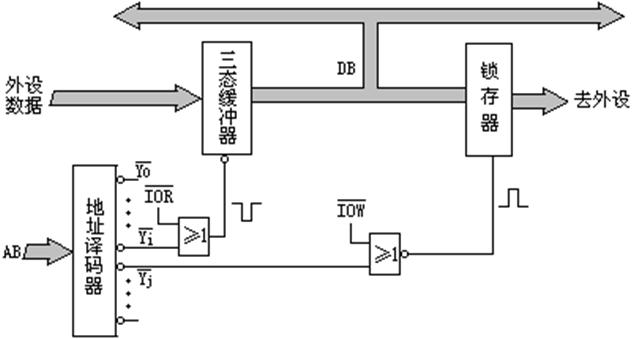

原理图

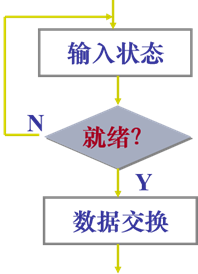

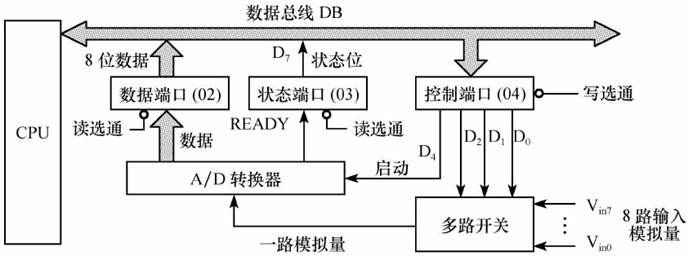

查询传送方式(条件传送方式)

CPU需要先查询外设的工作状态,然后在外设就绪后实现数据输入或输出。

特点:工作可靠,适用面宽;但传送效率低。

就绪的含义

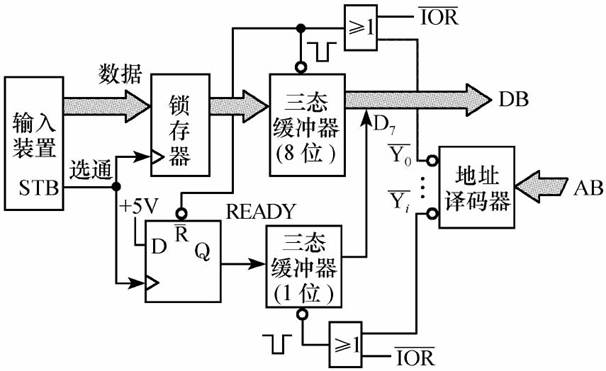

在输入场合【READY】

- 说明输入接口已准备好送往CPU的数据,正等着CPU来读取。

- 也可用接口中数据缓冲器已“满”来描述。

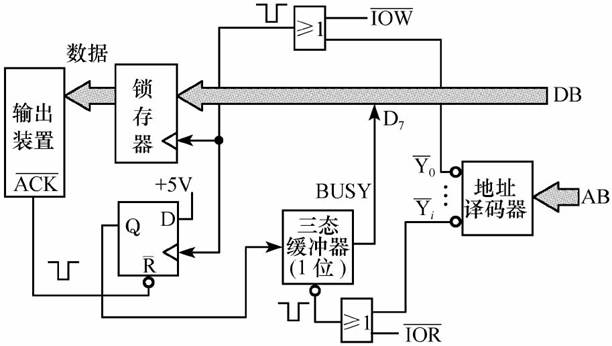

在输出场合【BUSY】

- 说明输出接口已做好准备,等待接收CPU要输出的数据。

- 也可用接口数据缓冲器已“空”、或者用外设“闲”或不“忙” (Busy)来描述。

1 查询环节

寻址状态端口

读取状态寄存器的标志位

若不就绪就继续查询,直至就绪

2 传送环节

寻址数据端口

输入:通过输入指令从数据端口读入数据

输出:通过输出指令向数据端口输出数据

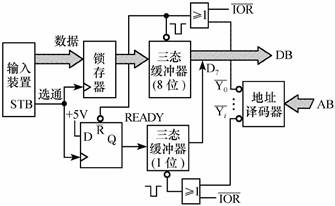

案例【查询输入/出接口】

案例【查询接口综合举例】

中断传送方式(效率更高)

CPU执行程序时,被内部或外部的事件所打断,转去执行一段预先安排好的中断服务程序服务结束后,又返回原来的断点,继续执行原来的程序。

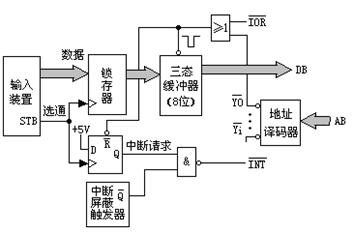

中断输入接口

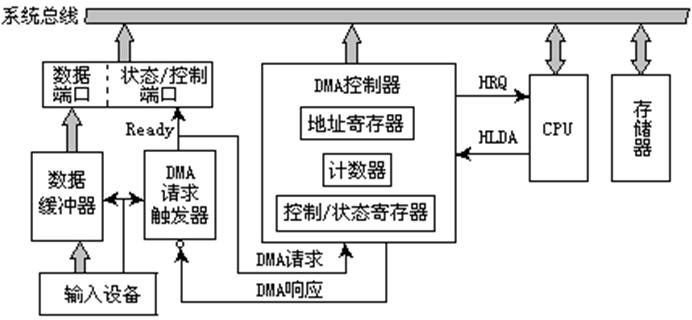

DMA传送方式

希望克服程序控制传送的不足:

外设 → CPU → 存储器

外设 ← CPU ← 存储器

直接存储器存取DMA:

外设 → 存储器

外设 ← 存储器

CPU释放总线,由DMA控制器(DMAC)管理。

工作过程

CPU对DMA控制器进行初始化设置。

外设、DMAC和CPU三者通过应答信号建立联系后,CPU将总线交给DMAC控制。

DMA传送

DMA读存储器:存储器 → 外设

DMA写存储器:存储器 ← 外设

自动增减地址和计数,判断传送完成否。

小结

无条件传送方式小结

硬件结构与软件设计均很简单,但传送可靠性差。

常用于同步传送系统和开放式传送系统中。

如广告牌、LED灯。

查询传送方式小结

传送数据可靠性很高,但CPU的使用效率很低。

常用在任务比较单一的系统中。

如一般测控系统。

中断传送方式小结

可靠性高,效率也高。

常用于外设的工作速度比CPU慢很多且传送数据量不大的系统中。

如实时系统。

DMA传送方式小结

可靠性和效率都很高,但硬件电路复杂。

常用于传送速度高、数据量大的系统。

如硬盘、光盘、高速数据采集系统、高速通信系统、图像处理等。

I/O端口地址译码与读写控制

I/O地址的译码方法与存储器地址的译码方法一样。

高位地址线与CPU的控制信号结合,经译码电路产生I/O接口芯片的片选信号。

低位地址线直接连到I/O接口芯片,实现I/O接口芯片的片内寻址。

I/O 地址译码电路的方式

利用门电路进行地址译码

利用译码器电路进行地址译码

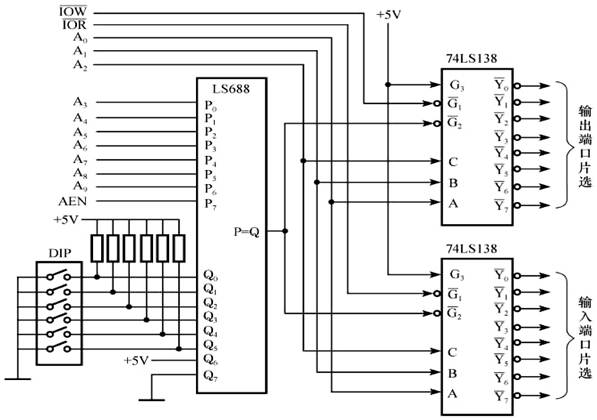

开关式可选择地址译码

开关式的-->开关闭合,电阻连通,Q0~Q5值为0

8位数据比较器74 LS688。当P0~P7与Q0~Q7状态一致时,P=Q输出低电平。

部分地址译码

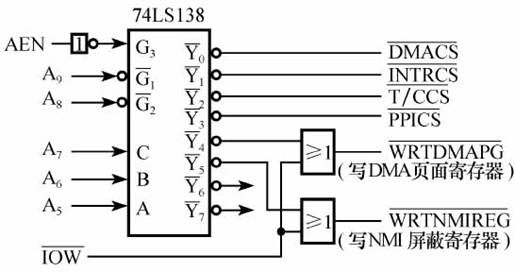

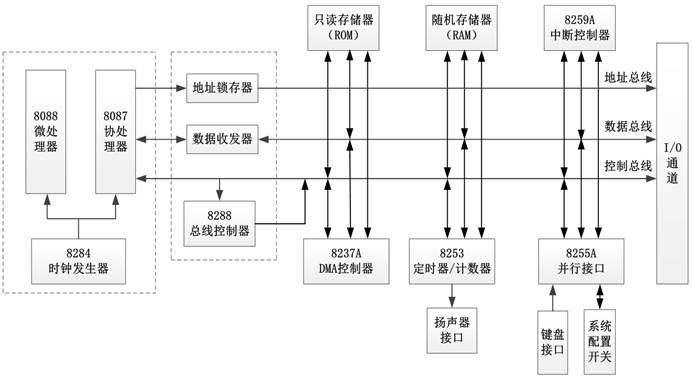

IBM PC系列机组成

处理器子系统、存储器子系统及I/O接口电路

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?