前言:以往许多 CPU 只携带USB2.0信号接口,无法满足许多应用场景的USB3.0信号。此时,就需要通过现有PCIE接口去进行信号转换为USB3.0信号支持产品功能。

就目前市面上常用转接芯片而言,主流以瑞萨µPD720201以及威锋VL805为主,今天就此机会介绍以下瑞萨µPD720201这颗芯片的具体参数。

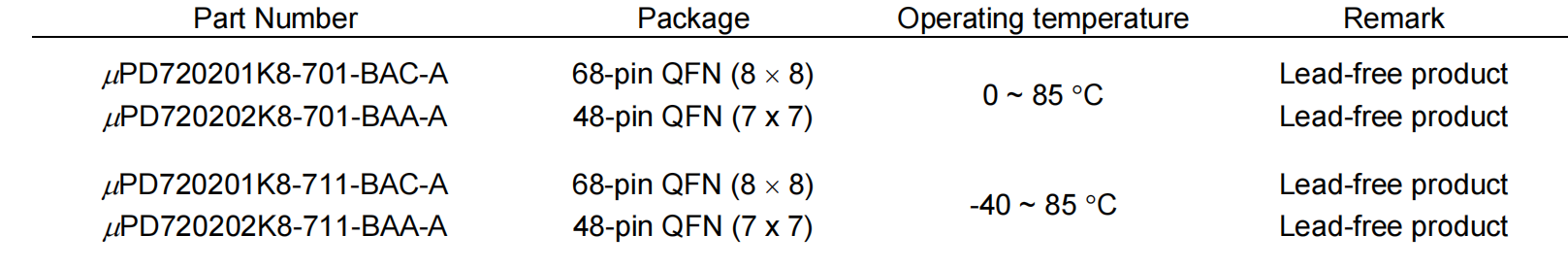

首先对二者做出对比,µPD720201相对于VL805而言,在功能上有部分优势的同时,应用场景也相对广泛,涵盖工规商规两种规格,两种封装,针对于不同应用场景下的合理搭配选择。而VL805目前仅支持商规级QFN64封装的产品开发,

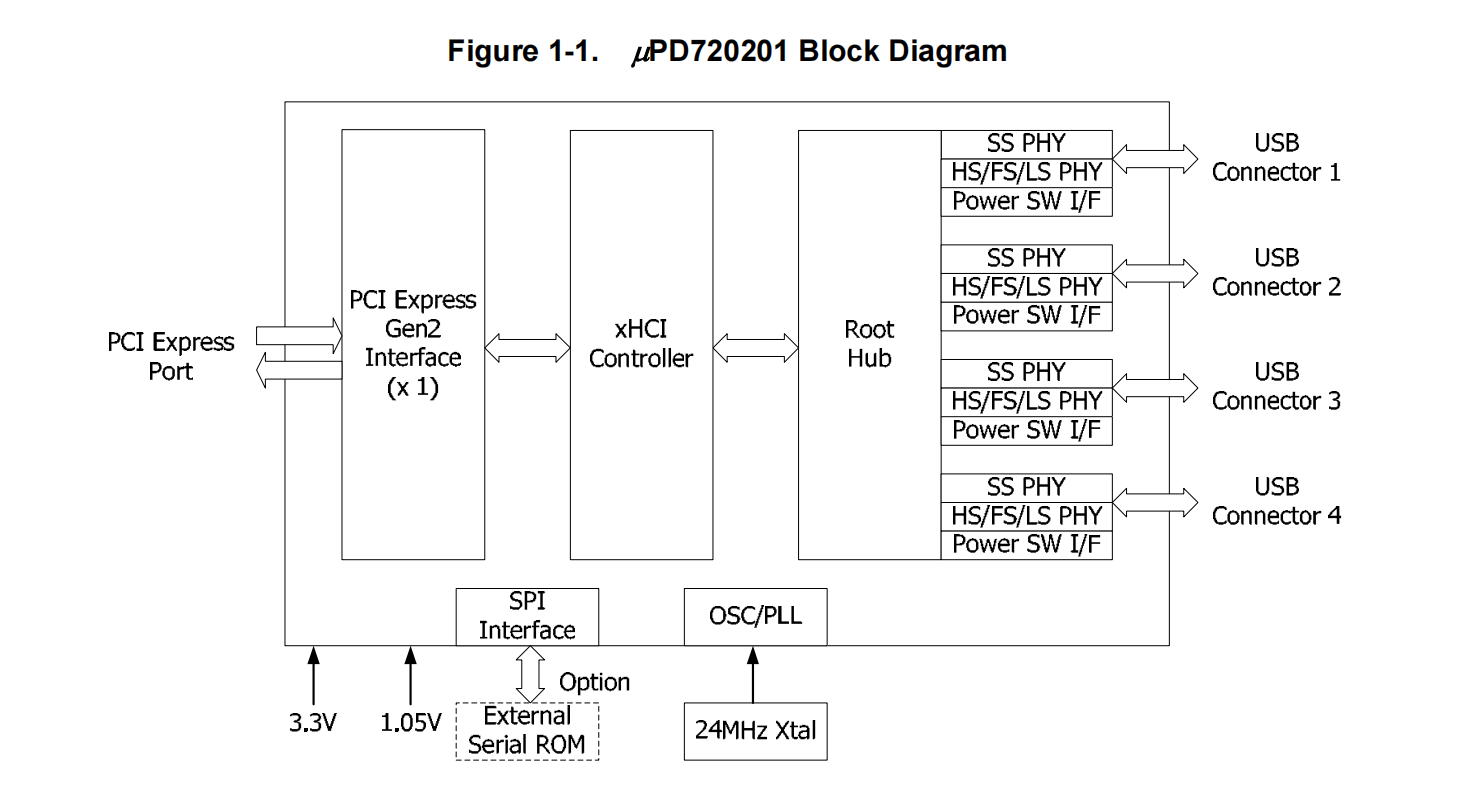

下图为µPD720201内部运行框图为例:

μPD720201 最多支持四个 USB3.0 个超高速端口,μ PD720202 最多支持两个USB3.0个超高速端口。μPD720201和 μPD720202 使用 PCI Express®Gen 2 系统接口总线,硬件设计工程师能够轻松添加多达四个(μPD720201)或两个(μPD720202)USB3.0个超高速端口连接到包含 PCI Express 总线接口的系统。

当连接到 USB 3.0兼容的外围设备,μPD720201和 μPD720202 可以以高达5Gbps 的时钟速度传输信息。μPD720201和 μPD720202 以及 USB3.0 标准与以前的 USB2 完全兼容并向后兼容。

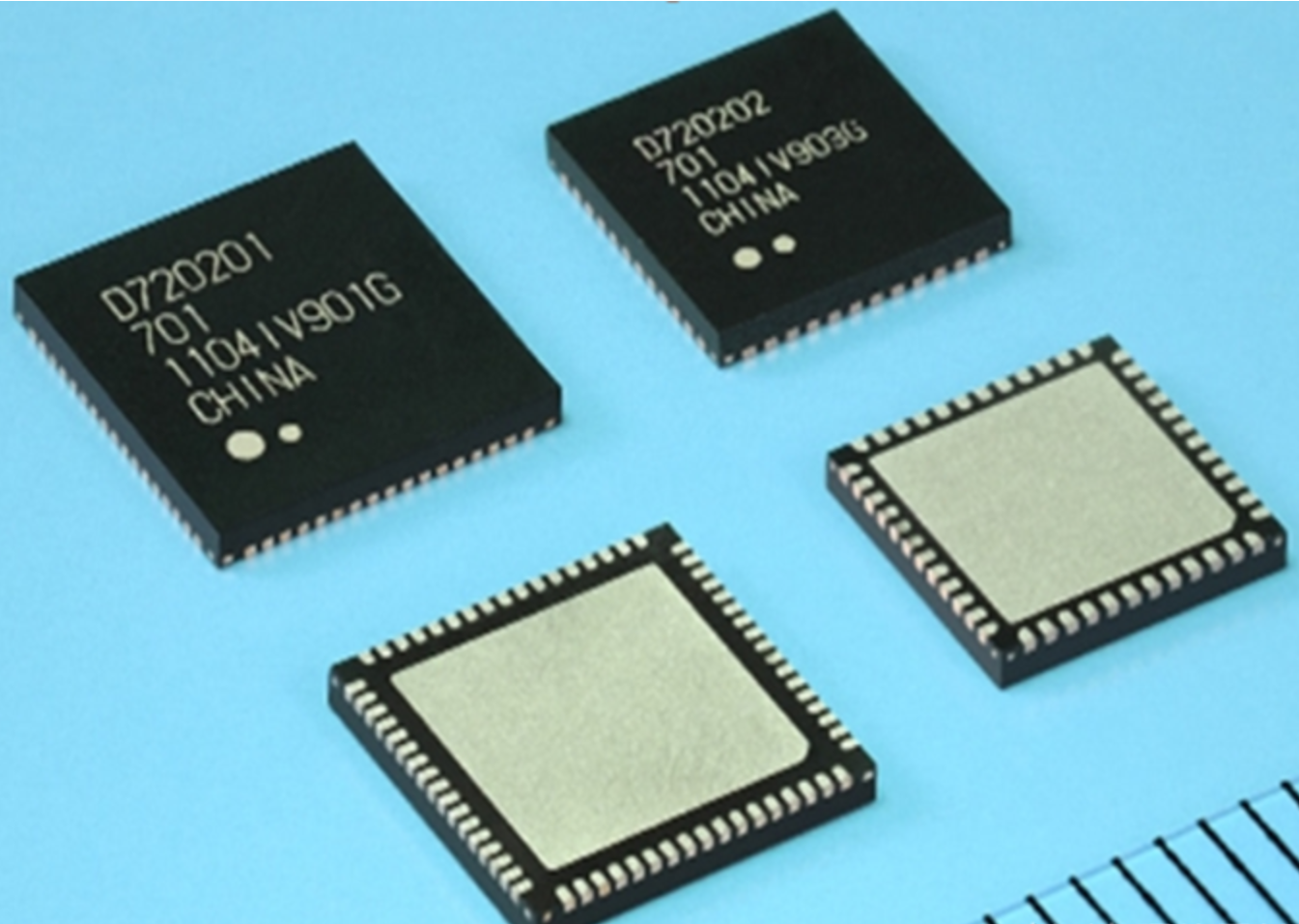

瑞萨 USB 3.0 控制器采用了 QFN 小尺寸封装,μPD720201 封装尺寸 8x8mm,μ PD720202 封装尺寸 7x7mm。新款芯片支持从 BIOS 通过 PCI-E 总线下载安装固件升级,不再需要搭配外置闪存,降低了整个解决方案的 PCB 面积和芯片数量。有效降低了芯片工作在低功耗状态(未连接 USB 外设)的漏电流水平,从而将低功耗状态功率降至 4.5mw,相比上代产品节电 90%。通过改善数据传送处理电路,使用外置硬盘等USB 3.0设备的实际传输速度相比上代 μPD720200A可提升40%。

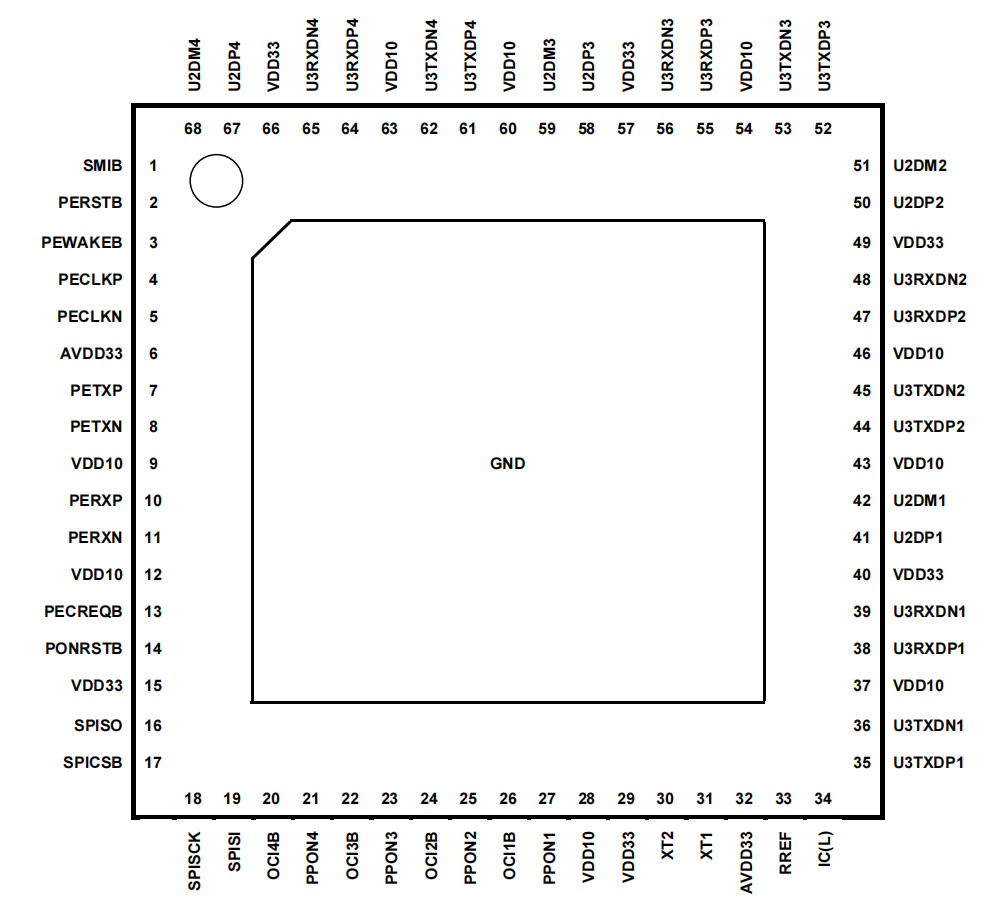

μPD720201封装pin脚示意例图:

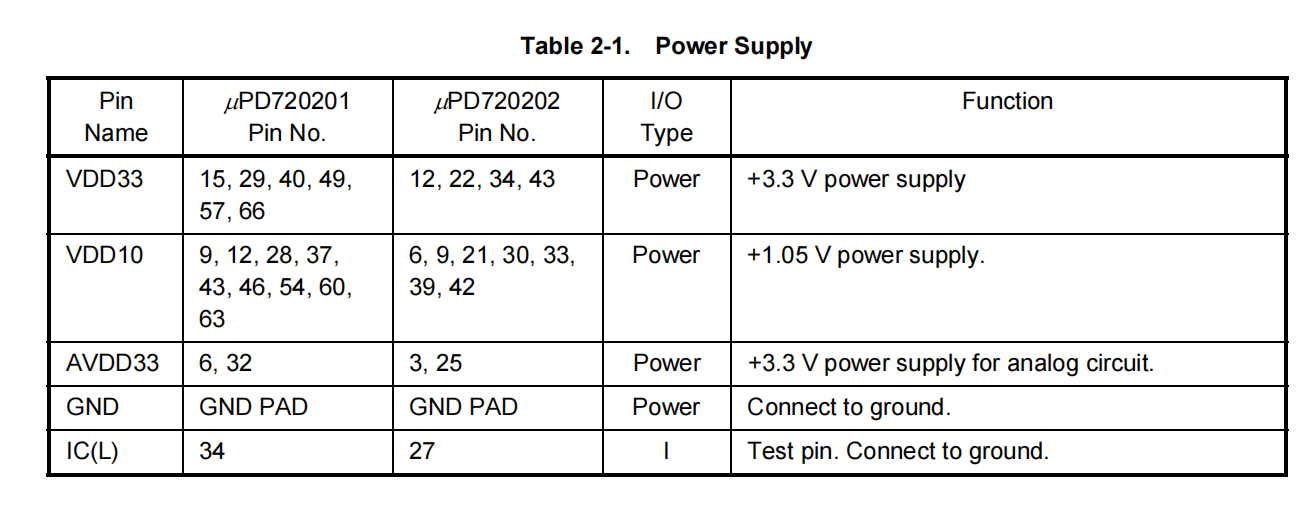

电源pin脚定义:常规3.3V,1.05V外围电路

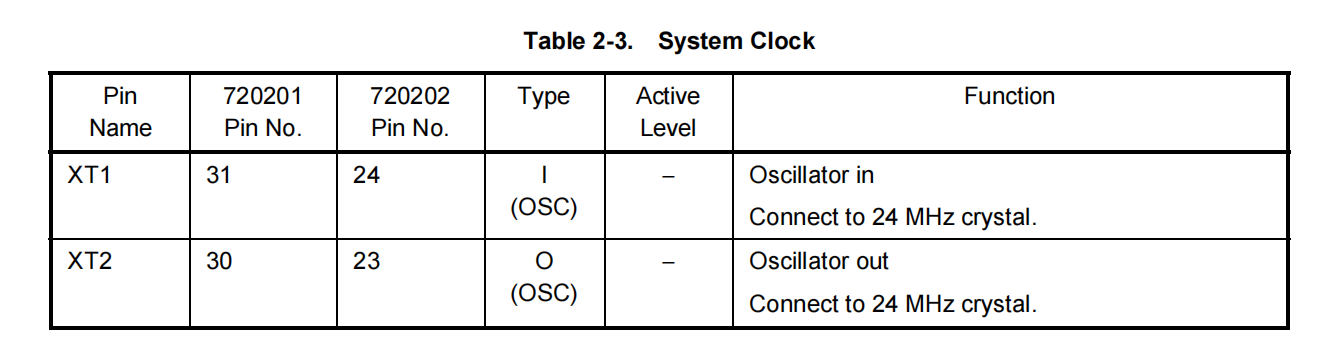

时钟PIN脚定义:支持24MHZ通用时钟。

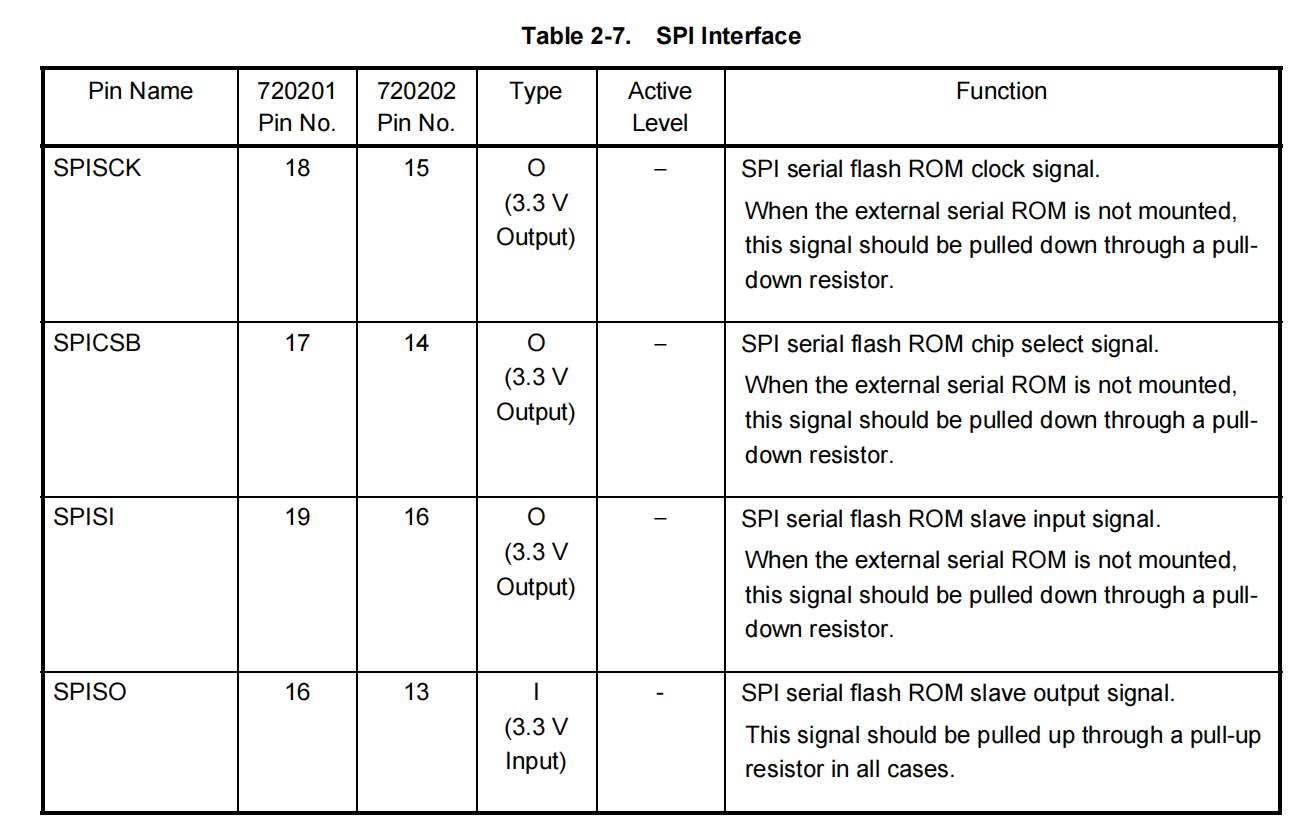

SPI串口PIN脚定义:

其余PCLE以及USB高速信号PIN脚定义详情请参考规格书以及Layout注意事项参考,篇幅有限就不在此赘叙,需要详细规格书原理图参考与样片测试的朋友可随时联系小编,该芯片配备完整的硬件平台和软件SDK。,尤其针对典型应用场景提供了源码级方案支撑,可帮助缩短产品开发周期、加快产品上市时间。随时欢迎联系,非诚勿扰。

903

903

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?