目录

2.3、CPSR-当前程序状态寄存器(Current Program Status Register)

1、嵌入式硬件系统

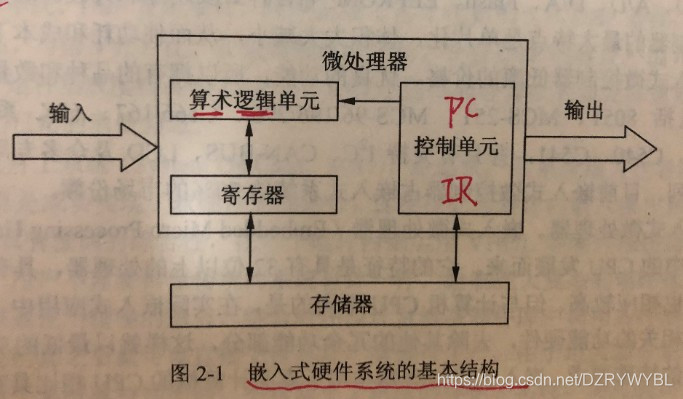

嵌入式硬件系统一般由嵌入式微处理器、存储器、输入/输出部分组成。嵌入式微处理器是嵌入式硬件的基础,通常由控制单元、算术逻辑单元和寄存器促成。

-

控制单元:

主要负责取址、译码、去操作数等基本动作。包含两个重要的寄存器,程序 计数器(PC)和指令寄存器(IR)。

程序计数器用于记录下一条程序指令在内存的位置,以便控制单元能到正确的内存单元取址。

指令寄存器负责存放被控制单元所取的指令,通过译码,产生必要的控制信号送到算术逻辑单元进行相关的数据处理。

-

算术逻辑单元

算术逻辑单元分为两部分,一部分是算术运算单元,主要处理数值型的数据,进行数学运算,例如加减乘除;另一部分是逻辑运算单元,主要处理逻辑运算工作,例如AND、OR、NOT.

-

寄存器

用于存储临时性的数据

2、典型8位微处理器的结构和特点

2.1、8051硬件结构

- CPU

- ROM:4096个8位掩膜存储器

- RAM:128个用户数据存储单元和128个专用寄存器单元

- 定时/计数器:两个16位可编程定时/计数器

- 输入输出口:四组8位I/O接口

- 全双工串口通信

- 中断系统:两个外部中断、两个定时/计数器中断和一个串行中断

- 时钟电路

2.2、MCS-51的寻址方式

-

直接寻址

MOV A,68H将内部RAM中的68H单元的数据内容传送到累加器A中

-

寄存器寻址

MOV A,R1-

寄存器间接寻址

MOV A,@R0-

立即寻址

MOVX A,#0EH立即寻址就是把操作数直接在指令中给出,即操作数包含在指令中,指令操作码的后面金紧跟着操作数,指令操作码的后面紧跟着操作数,一般吧之林中的操作数称为立即数。为了与直接寻址方式相区别,在立即数钱加上“#”符号。

-

变址寻址

MOV A,@A+DPTR

MOV A.@A+PC变址寻址是以DPTR或PC作为基址寄存器,以累加器A作为变址寄存器,将两寄存器的内容相加形成16位地址形成操作数的实际地址。

-

位寻址

-

相对寻址

2、ARM处理器

2.1、ARM概述

ARM(Advance RISC Machine)公司是一家专门从事芯片IP设计与授权业务的英国公司。许多一流的芯片厂商都是ARM的授权用户,如Inter、Samsung、TI、FreeScale、ST等公司。

2.2、ARM的运行方式

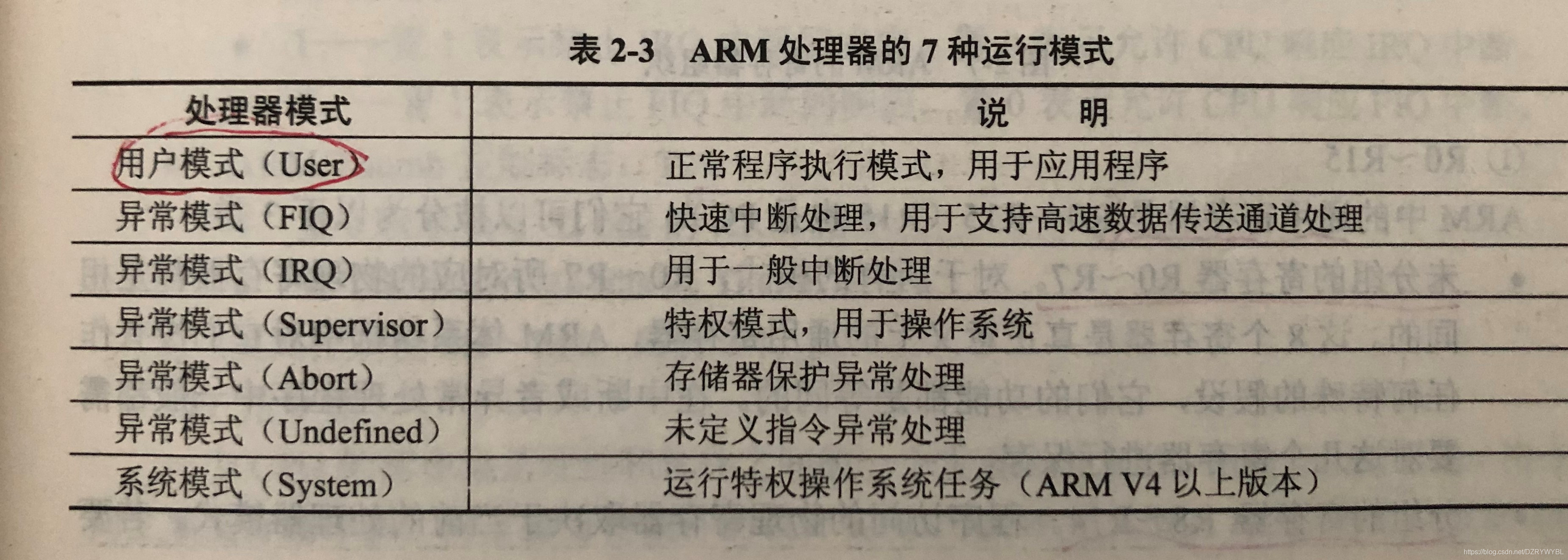

ARM有七种运行方式

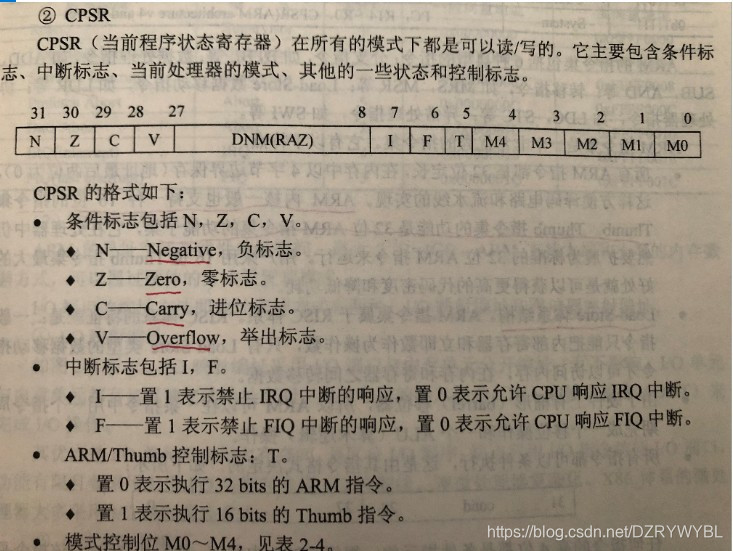

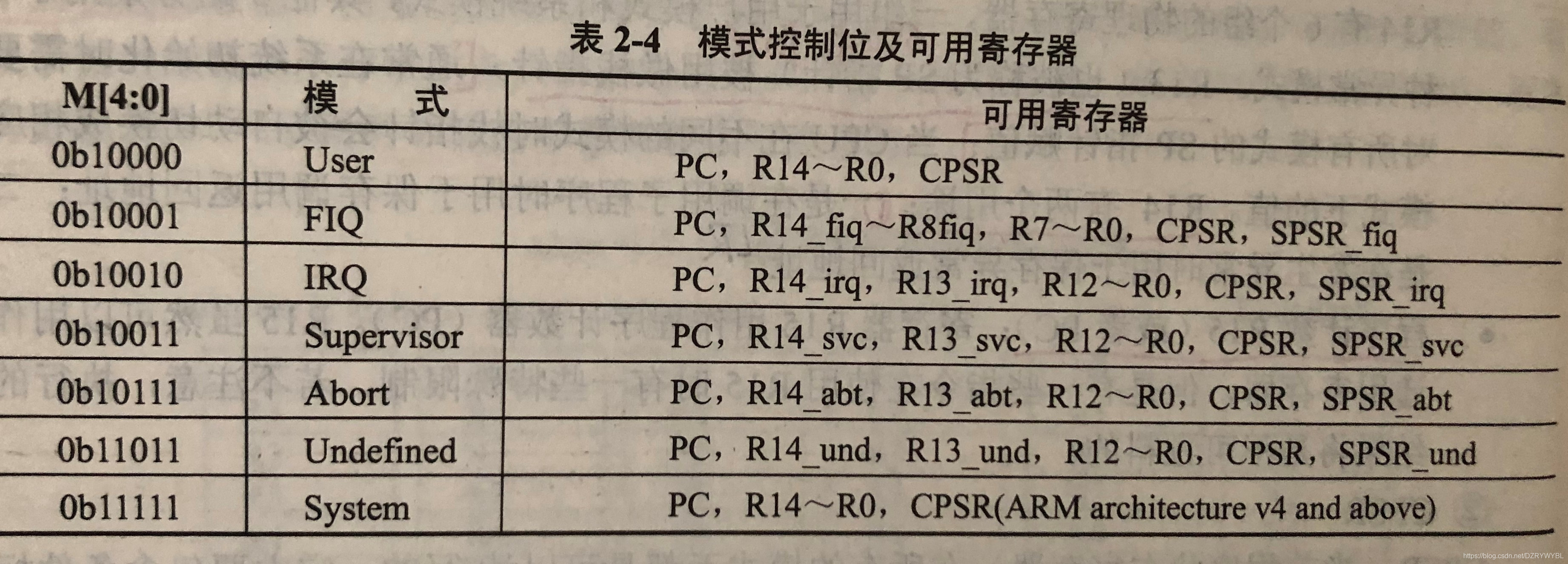

2.3、CPSR-当前程序状态寄存器(Current Program Status Register)

2.4、ARM中断与异常(摘自网络)

A、 ARM 内核支持7种中断,不同的中断处于不同的处理模式,具有不同的优先级,而且每个中断都有固定的中断地址入口。 当一个中断发生时, 相应的 R14(LR) 存储中断返回地址, SPSR 存储当前程序状态寄存器 CPSR 的值。

B、由于 ARM 内核支持流水线工作, LR 寄存器存储的地址可能是发生中断后面指令的地址, 所以不同的中断处理完成后,必须将 LR 寄存器值经过处理后再写入 P15(PC)寄存器。

C、ARM 异常的具体含义:

- 复位: 当处理器的复位电平有效时, 产生复位异常, 程序跳转到异常复位异常处理程序处执行。

- 未定义的指令:当 ARM 处理器或协处理器遇到不能处理的指令时,产生未定义指令异常。可以使用该异常机制进行软件仿真。

- 软件中断: 该异常由执行 SWI 指令产生, 可用于用户模式下的程序调用特权操作指令。 可使用该异常机制实现操作系统调用功能。

- 指令预取中止:如果处理器预取指令的地址不存在或该地址不允许当前指令访问,存储器向处理器发出中止信号,但当预取的指令被执行时,才会产生指令预取中止异常。

- 数据访问中止: 如果处理器数据访问指令的目标地址不存在, 或者该地址不允许当前指令访问,处理器产生数据访问中止异常。

- 外部中断请求:当 ARM 外部中断请求管脚有效,而且 CPSR 中的 I 位为0时,产生 IRQ 异常。

- 系统的外设可以通过该异常请求中断服务。

- 快速中断请求:当 ARM 快速中断请求管脚有效,而且 CPSR 的 F 位为0时,产生 FIQ 异常。

D、 ARM 处理器对异常中断的响应过程

- 将下一条指令的地址存入相应的连接寄存器 LR 中。

- 将 CPSR 复制到相应的 SPSR 中。

- 根据异常的类型,强制设置 CPSR 的运行模式位。

- 强制 PC 从相关的异常向量地址取下一条指令执行,从而跳转到相应的异常处理程序处。

E、 ARM 处理器从异常中断处理程序中返回

- 恢复中断的程序的处理器状态,将 SPSR 复制到 CPSR 中。

- 若在进入异常处理时设置了中断禁止位,要在此清除。

- 将连接寄存器 LR 的值减去相应的偏移量后送到 PC。

F、复位异常中断处理程序不需要返回。在复位异常中断程序开始整个用户程序的执行

4006

4006

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?