目录

1. 简介

在博文《Vitis HLS 学习笔记--资源绑定-使用URAM-CSDN博客》中,介绍了如何在Vitis HLS环境下设计一个简易的存储器模型。

通过以下编译器指令:

static data_t buffer[NWORDS];

#pragma HLS DEPENDENCE variable = buffer inter WAR false

#pragma HLS BIND_STORAGE variable = buffer type = ram_2p impl = uram

我们成功创建了一个既能读又能写的存储器,并且明确使用了 UltraRAM(URAM)作为其存储媒介。

本文旨在深入探讨该实现的内部机制,通过研究 HLS 工具所生成的 RTL 代码,解析该存储器模型的构建过程和工作原理。

2. 代码分析

2.1 存储器代码

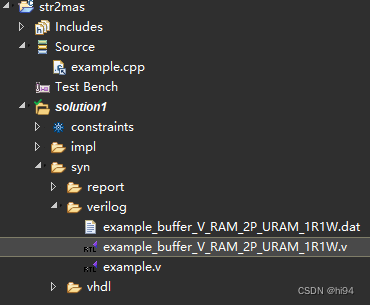

在以下路径,我们可以发现,生成了两个 verilog 文件:

其中 example.v 是顶层文件,而example_buffer_V_RAM_2P_URAM_1R1W.v 则是定义储存器的文件。

打开后,其内容如下:

`timescale 1 ns / 1 ps

module example_buffer_V_RAM_2P_URAM_1R1W (address0, ce0, q0, address1, ce1, d1, we1, reset,clk);

parameter DataWidth = 128;

parameter AddressWidth = 14;

parameter AddressRange = 16384;

input[AddressWidth-1:0] address0;

input ce0;

output reg[DataWidth-1:0] q0;

input[AddressWidth-1:0] address1;

input ce1;

input[DataWidth-1:0] d1;

input we1;

input reset;

input clk;

(* ram_style = "hls_ultra", cascade_height = 1 *)reg [DataWidth-1:0] ram[0:AddressRange-1];

initial begin

$readmemh("./example_buffer_V_RAM_2P_URAM_1R1W.dat", ram);

end

always @(posedge clk)

begin

if (ce0) begin

q0 <= ram[address0];

end

end

always @(posedge clk)

begin

if (ce1) begin

if (we1)

ram[address1] <= d1;

end

end

endmodule

其实代码逻辑功能很简单,创建一个具有两个端口(一个用于读取,一个用于写入)的RAM缓冲区。

2.2 Implementation报告

要查看IMPL 报告,需要运行“Run Implementation”:

我们关注报告中如下内容:

================================================================

== RTL Synthesis Resources

================================================================

+-------------------------+-----+----+-----+------+------+-----+--------+------+---------+----------+----------------+

| Name | LUT | FF | DSP | BRAM | URAM | SRL | Pragma | Impl | Latency | Variable | Source |

+-------------------------+-----+----+-----+------+------+-----+--------+------+---------+----------+----------------+

| inst | 136 | 4 | | | 8 | | | | | | |

| (inst) | 2 | 2 | | | | | | | | | |

| buffer_V_U | 134 | 2 | | | 8 | | | | | | |

| bind_storage ram_2p | | | | | | | pragma | uram | 1 | buffer_V | example.cpp:16 |

+-------------------------+-----+----+-----+------+------+-----+--------+------+---------+----------+----------------+可见,该存储器使用了8个 URAM来实现的,没有用到 BRAM。

2.3 存储器类型指定

(* ram_style = "hls_ultra", cascade_height = 1 *)reg [DataWidth-1:0] ram[0:AddressRange-1];ram_style = "hls_ultra",指定RAM类型。

cascade_height = 1,限制级联的深度或高度。在构建所需的存储器时,综合工具应尽量限制使用级联内存块的深度或高度为1。这可以理解为尽量不要让多个RAM块在垂直方向上连接形成更深的存储结构。

2.4 存储器初始化

initial begin

$readmemh("./example_buffer_V_RAM_2P_URAM_1R1W.dat", ram);

end需要特别注意,在大多数情况下,initial块通常被视为仅用于仿真目的,用于在仿真开始时执行一次性操作,而不是用于硬件实现。在此代码段中,initial块通过$readmemh系统任务从指定的文件 "./example_buffer_V_RAM_2P_URAM_1R1W.dat")中读取数据,并将这些数据初始化到URAM(超级RAM)的ram数组中。

然而,在Vitis HLS中,$readmemh,可以被识别并转化为硬件实现的一部分,实现硬件中预加载存储器内容。这一点我们可以在 Package IP 中确认。

3. 总结

通过本文深入探讨了在Vitis HLS环境下设计的存储器模型的内部机制。通过分析生成的RTL代码和IMPL报告,我们了解到该存储器模型利用URAM实现,具有读写功能,并且限制了级联深度为1。特别地,我们注意到存储器的初始化操作在Vitis HLS中被转化为硬件实现的一部分,这为预加载存储器内容提供了便利。总的来说,本文为使用Vitis HLS设计存储器提供了实用的指导,加深了对存储器设计原理的理解。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?