PCI-E和PCI-X规范定义了ECAM机制来通过内存访问设备配置寄存器。这段映射到内存的配置空间地址是BIOS分配的,并会传递给OS来使用。

对支持ECAM的设备来说,和PCI 2.3兼容的配置空间头256个字节(便宜为0-255)可以通过IO端口访问(CF8/CFC),或者使用ECAM。256-4096字节的内容可以用过PCIe驱动的ECAM来访问。

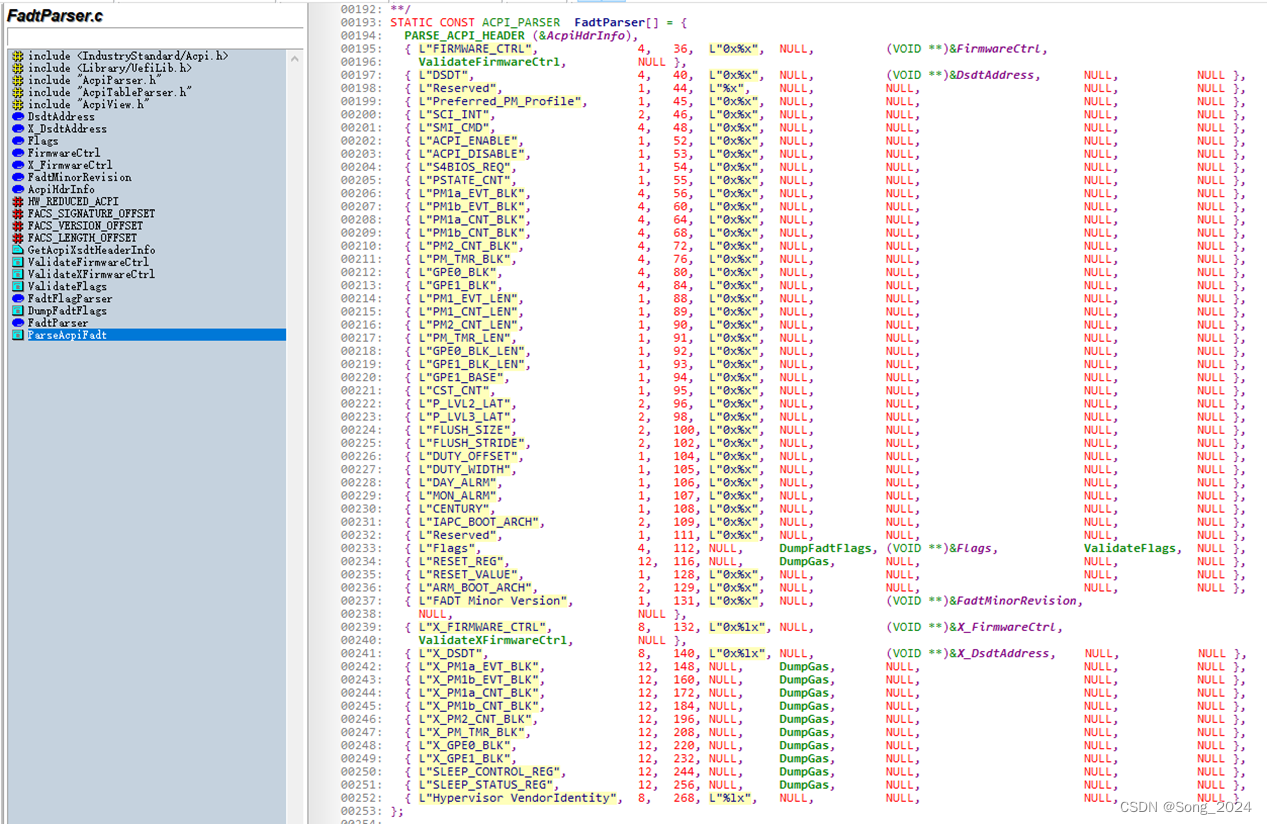

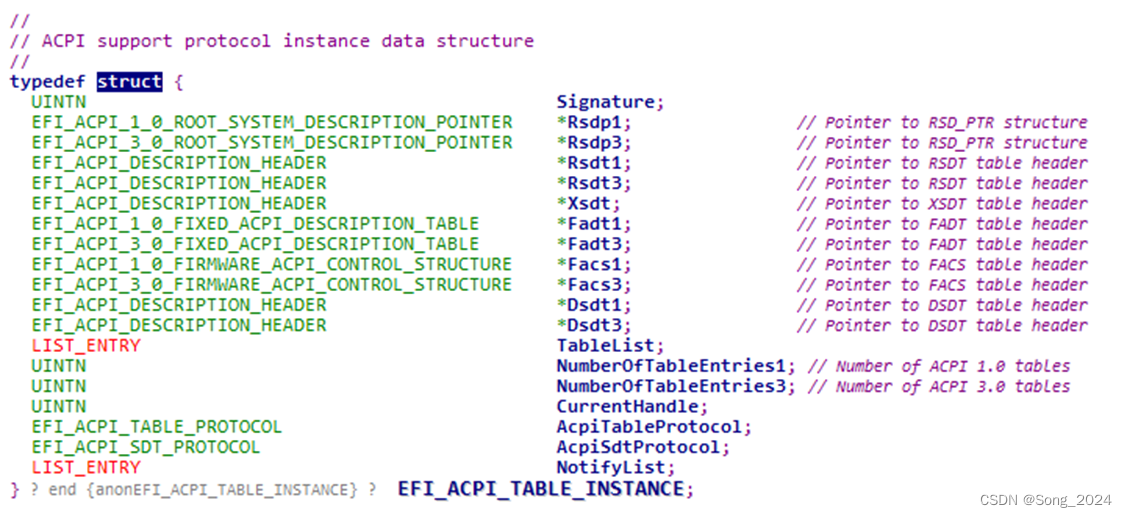

EDKII中创建的所有ACPI Tables。

CPU用来访问设备的地址不是必须和设备BAR中保存的一样。收发信息,如_TRA\_TTP\_TRS对OS来说不可得,直到OS启动了ACPT中断之后。OS必须等待,直到ACPI中断起来后决策好原先由BIOS设置的BAR地址,并设为当前处理器访问地址。在启动资源之前,OS必须用父Host Bridge的_CRS 描述符中定义的地址范围来重新配置BAR寄存器。OS必须确保地址范围没有被Host bridge下的其他设备占用。

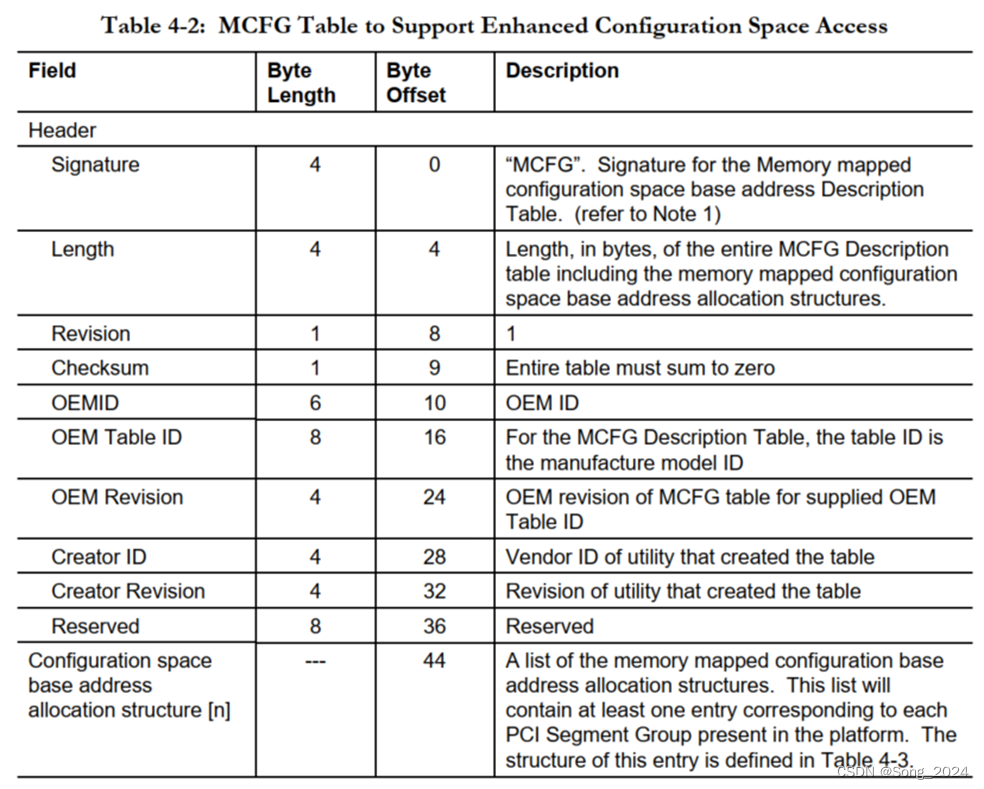

ACPI中的MCFG Table

MCFG: 用来记录非热插拔设备或者系统启动设备的MMIO CFG地址,是ACPI表形式提供的。在本次启动过程中,该地址不可更改。

CBA:用来访问设备的高级配置地址的ACPI接口,用来给热插拔设备实时更新用。

MCFG给启动过程中的非热插拔提供MMIO访问地址,CBA给热插拔设备提供MMIO地址。

固件对Host Bridges主桥设备的配置

固件必须配置系统中所有Host Bridges主桥设备,以便OS使用Host Bridges下的设备,即使它们没有连接到console或者boot device。Host Bridges不属于PCI规范中定义。对Host Bridge配置包括以下:

- 设置Host Bridges的内存和IO空间

- 所有Host Bridges消耗的资源,以及传递给下一级bus所需要的资源都需要被配置

- 桥要设置为能进行收和发包操作

- 桥要在安全模式下操作,安全模式包括

启动IO Port, Memory address,VGA routing,bus number等

启动奇偶校验和系统错误监测等

配置Cacheline,latency timer和其他PCI要求的寄存器

固件注册Host Bridge信息到ACPI Namespace

固件必须将Host Bridge信息注册到ACPI Namespace. 每个Host Bridge都必须包含如下内容:

BIOS配置PCIe设备的前提及如何查询某个PCIe设备CFG是否被BIOS配置过了

BIOS只配置boot和console devices,boot device需要在OS被加载前和用户进行交互。BIOS必须配置所有的Host Bridge和PCI-PCI Bridge桥设备。OS检测command registers里的IO Enable Bit、Memory Enable Bit和EXP ROM Enable Bit可以知道某个设备寄存器是否被BIOS配置过了。BIOS中可以打开或关闭某个PCIe slot:EP CFG 0x34->CapPtr->0x10 PCIe Capability Structure -> 0x14h Slot Capability Register -> bit2 MRL Sensor Present -> bit 4 Power indicator present。

EDKII中ACPI Table的构建

参考文档

2728

2728

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?