最近在复习本科的《现代操作系统》课本,一口气看完了3章,略有所感,故写下此篇。

使用操作系统的动机是它可以:

1/ 抽象物理底层的硬件,提供用户使用硬件的便利;

2/ 自动管理整合资源;

对运行的程序的抽象是:进程。这在这篇文章会详细叙述进程和进程集合的死锁问题:http://blog.csdn.net/firehotest/article/details/52310715

对主存的抽象是:地址空间。同时,一直以来,存储器的容量增长始终赶不上信息量的增长。大小远远落后于程序平均占用主存大小。所以产生了虚拟内存这种技术,建立页表,并发展了分页的算法和多种页面置换的算法。在本篇文章将详述。

对磁盘的抽象是:文件系统(树型系统)。详述地址:http://blog.csdn.net/firehotest/article/details/52348042

接下来,从总体来说说我们的计算机以及操作系统。

计算机模型及其硬件

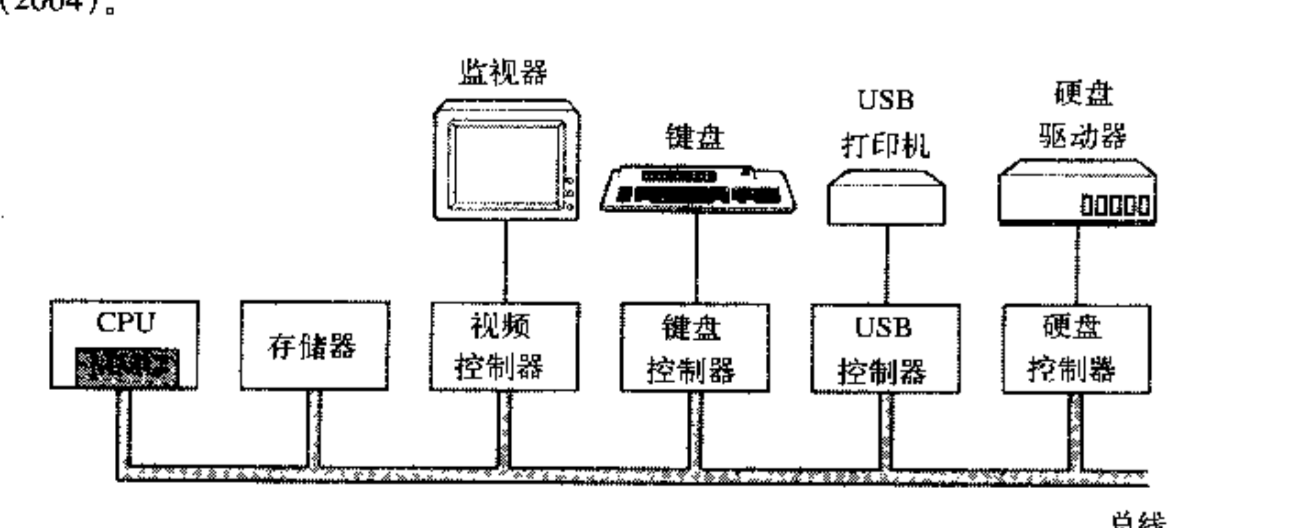

首先,我们从最简单的模型开始说起:

图来自《现代操作系统》

CPU中的MMU是(Memory Management Unit),用来把程序需要读取的虚拟地址转换为真实的物理地址。它具体原理在主存的抽象部分有提及。各种控制器就是我们常说的显卡等。

CPU和存储器插槽都是位于主板上。主板 (parent board)更称之为双亲板。有时,网卡、显卡(视频控制器)都可以集成到主板上。

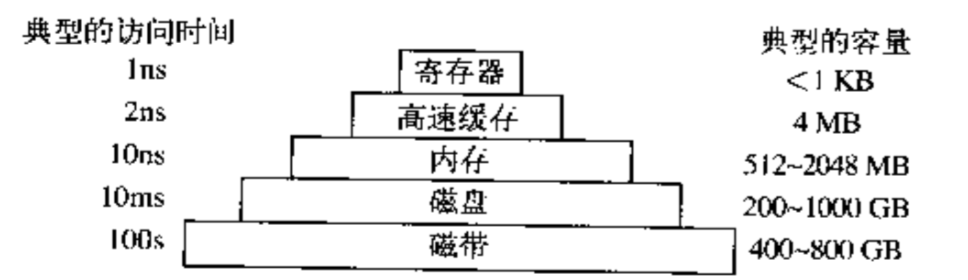

而存储器,因为需要在容量和成本上折中,被抽象成为了一个金字塔的结构。把这个金字塔结构熟记于心是一个合格的开发者的要求【1】:

CPU和存储器

CPU的工作流程是:取指 --> 解释指令 --> 执行指令。解释指令和执行指令的耗时短,当编译器承担了生成机器码的工作时,CPU甚至不需要解释指令。所以,CPU工作的耗时往往在于取出指令和相关数据。

所以,有了存储器最顶级(容量最小、速度最快且造价最贵)的寄存器的发明。CPU从寄存器读取数据的无延时的,因为寄存器的制造材料和CPU相同。CPU内部有专门保存临时变量和关键变量的寄存器。

关于寄存器和相关的知识,请参考这篇文章:http://blog.csdn.net/firehotest/article/details/58587701

比较重要的几个寄存器有如下三个:

① 程序计数器,存放着下一条将要执行的指令的内存地址。

② 堆栈指针,存放着目前程序的栈空间的顶端。一个程序在内存中保存的有:程序本身的指令代码、数据段(对象变量动态分配,释放)、堆栈段(函数的局部变量和返回地址)以及中间留空的内存空间。注意,指针指向的栈的顶端。(关于程序的内存模型以及内存的更深入分析,请见:)

③ PSW(程序状态字),存储当前CPU的模式是内核态(能执行所有指令)还是用户态(只能执行部分指令)等等的控制位。内核态和用户态的区分是操作系统用以保护计算机硬件的正确使用和安全的一种有效的机制。对于只有内核态才能使用的指令,用户程序可以使用陷阱(trap)机制去触发系统切换到内核态并调用内核函数(对应着用户态不能执行的指令)去解决。如read()就是一个内核函数。对应着把磁盘上的文件读到缓冲区中的一系列指令。

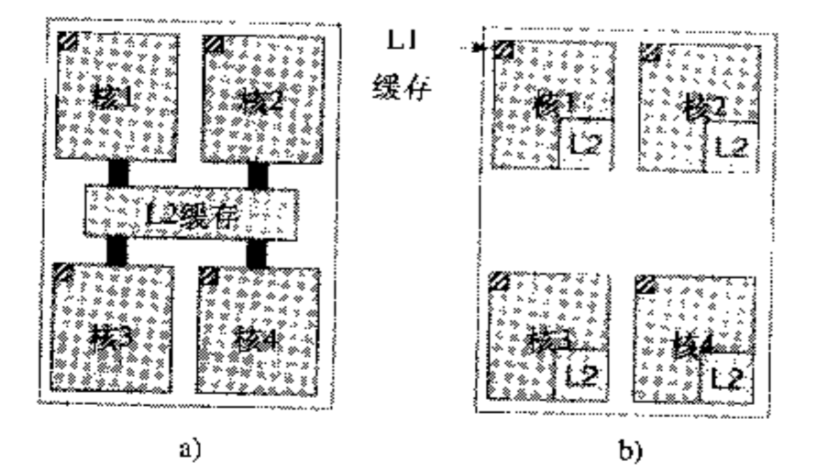

接下来的一级是高级缓存。目前计算机普遍把缓存分为3级。其中,L1缓存是CPU中每个核自备的,典型L1缓存大小是16KB。L2缓存也称为SRAM(Static Random Access Memory),一般L2缓存需要集成到CPU的内部。L1缓存的延时是可以忽略的,L2缓存则高级缓存命中约需要2个始终周期(2ns)左右。根据不同的厂商,其安置位置有所不同【1】,左边是Intel,右边的是AMD:

集成到CPU内部的好处是不需通过Bridge通信,但L2内存的速度要和CPU同频才能达到效果,而DRAM是无法达到这个速度的,所以L2缓存又称为SRAM,SRAM的设计使用的晶体管数量较多,价格高。通常,SRAM的电路构成是两个二极管。而DRAM的构成是用电容。

缓存被分为多个缓存行。(cache line)一个缓存行的典型大小是64Bytes.,一个Byte有一个地址索引。所以地址0到地址63对应缓存行0,64-127对应缓存行1。当CPU需要读取一个字(在intel的架构中,一个字约为2个字节)的数据时,如果这个字的数据在高级缓存中,则高级缓存命中。这种情况下,就不需要通过总线把访问请求送往主存。

假如出现miss的情况在,则需要从主存中调入对应的新内容进行高级缓存。通常使用的是高位定位法确定存储的缓存行。例如一个高级缓存行每行64字节,有4196(2^12)行数。所以,如果数据有32位,我们可以用0-5位共6位确认在行中的位置(2^6 = 64,确认第几个字节),在用6-17位共12位确定第几行。

关于缓存的结构和LRU(Least Recent Used)的原理请参考:http://blog.csdn.net/firehotest/article/details/58593042

DRAM就是我们常说的主存。关于它的抽象是操作系统的存储器管理器的主要功能。我们稍后再说。

从计算机启动说BIOS、ROM、Flash Memory和EEPROM

ROM是一种特殊的存储器。只能读,不能写,在数据断电后不会消失。目前已逐步采用Flash和Electronic Erasable PROM (EEPROM)代替。无论是Flash还是EEPROM,擦除过多会造成设备的损坏。它们的作用在于存放BIOS这个软件。

从速度上说,ROM > RAM > Flash > Disk.

主板上也有一块CMOS芯片,它需要一直通电,否则将失去数据。它的作用是保持当前的时间和日期和保存配置参数,即使计算机没有上电,时间仍然可以正常更新。配置参数指的是是否使用一些设备的参数,称为设备清单,决定网卡、显卡是否启动,以及系统从软盘、CD-ROM还是硬盘开始启动。

关于ROM和CMOS,要结合主板上的BIOS(basic input output system)以及开机过程来讲述:

主板上都有BIOS,BIOS内包含着底层的I/O程序,以前,BIOS都存在ROM当中,后来,由于ROM出厂后不能修改,给配件(I/O设备如键盘、显示器等)的升级带来不便,于是后来就存储在一块Flash memory中,也是是断电后不会消失的。

启动时,BIOS开始运行,首先通过I/O软件检查RAM大小和各种I/O设备是否正常,扫描ISA、 PCI总线的所有设备,如果发现新设备,则开始配置新设备。接着,BIOS在CMOS的设备清单中选择需要启动的设备和操作系统的启动源。然后,操作系统再次访问BIOS,检查每个设备的驱动程序是否存在,将驱动程序调入内核。如果发现有设备缺少驱动程序,则要求用户安装。

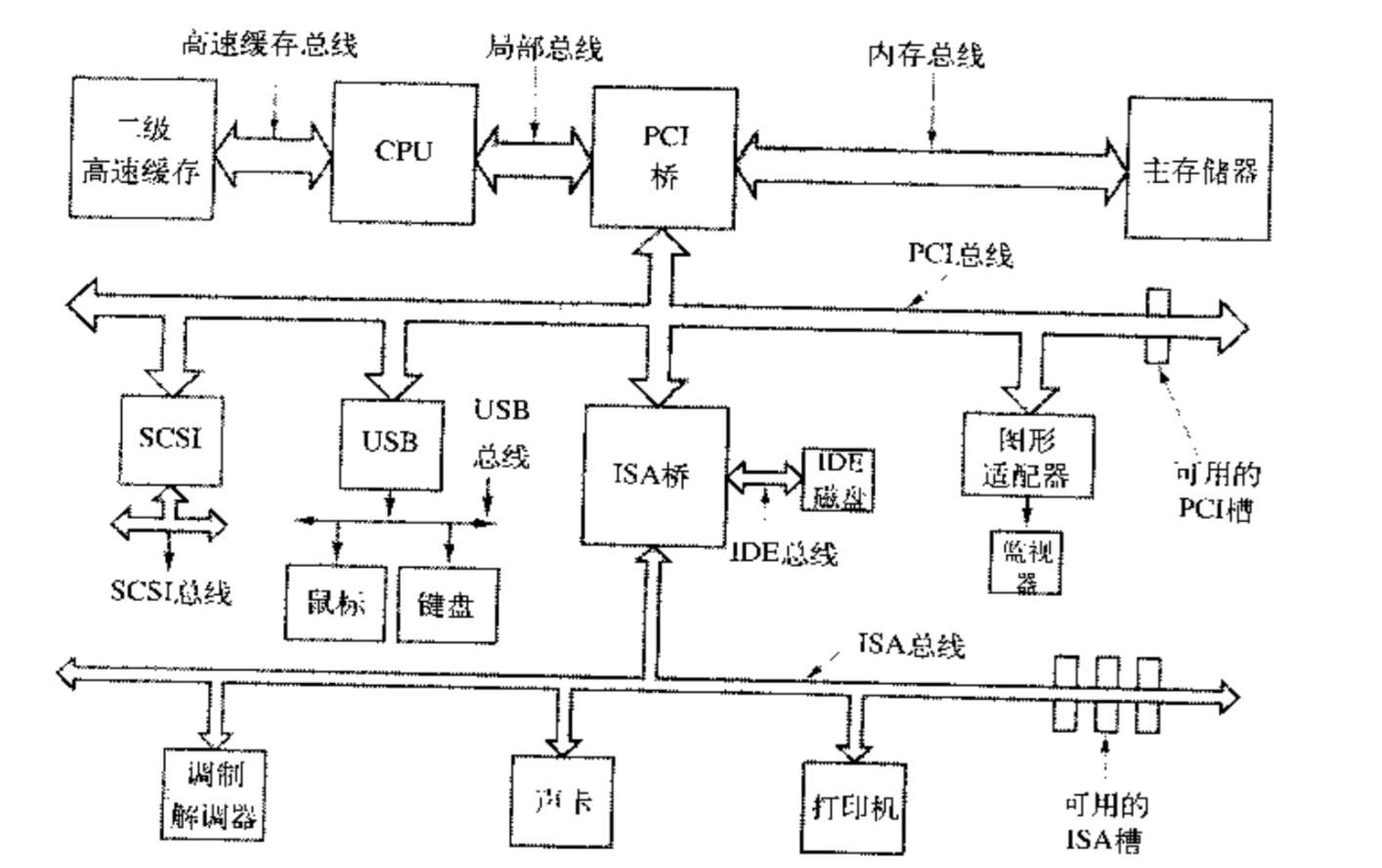

计算机总线

计算机总线最早的标准是IBM的ISA总线,8.33MHz频率,并行传送2字节,最大速率16MB/s。 后期Inter开发出PCI总线,对应告诉I/O,66MHz,并行传送8字节,最大速率528MB/s。对应的结构类似如下:

可以看出,ISA总线主要用来兼容老式的I/O设备,SATA/ IDE硬盘有专门的IDE总线。USB也有一种慢速设备的总线。全程是Universal Serial Bus,总共是4针的传送,其中2针是电源线。最原始的USB1.0 的传输速率只有1.5MB/s,2.0有60MB/s。其实一种集中式总线,每1ms轮询一次所有USB设备。所有的USB共享一个设备驱动器,所以新的USB设备无需安装驱动即可使用。

Reference:

本文图片来自《现代操作系统》 -- Andrew S.Tanenbaum

1407

1407

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?