开漏输出(Open-Drain) 和 推挽输出(Push-pull) 是两种常见的数字信号输出模式,它们用于控制电流流动的方式,不仅应用于 GPIO 引脚,也广泛应用于其他电子电路中,比如总线通信、驱动电路等。

1. 推挽输出(Push-pull Output)

推挽输出,简单的说,就是想输出高电平,就输出高电平,想输出低电平就输出低电平。

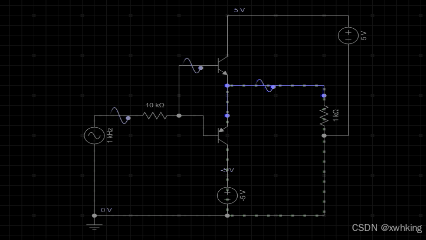

推挽输出 是最常见的输出方式,其原理是通过两个晶体管(一个是 NPN,一个是 PNP)来控制信号的输出。其工作原理是:

- 高电平:当需要输出高电平时,PNP 晶体管导通,NPN 晶体管截止,输出端与 Vcc(高电平)连接。

- 低电平:当需要输出低电平时,NPN 晶体管导通,PNP 晶体管截止,输出端与地(GND,低电平)连接。

工作原理图

Vcc

|

[PNP]

|----- Output

|

[NPN]

|

GND

- 输出高电平时:PNP 晶体管导通,NPN 晶体管截止,电流从 Vcc 通过 PNP 晶体管流到输出端。

- 输出低电平时:NPN 晶体管导通,PNP 晶体管截止,电流从输出端流到地。

特点:

- 输出高电平时:通过 PNP 晶体管将输出引脚拉到 Vcc 电压。

- 输出低电平时:通过 NPN 晶体管将输出引脚拉到地(0V)。

- 优点:推挽输出具有更强的驱动能力,可以提供较大的电流,因此适用于驱动负载如 LED、继电器、较大的电流设备等。

应用:

推挽输出通常用于需要驱动外部负载的场合,如控制 LED、马达、继电器等。

2. 开漏输出(Open-Drain Output)

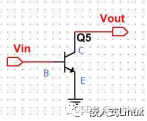

开漏输出是没有能力输出高电平驱动负载的,我们可以看看开漏输出的电路就知道了。

如上图,开漏输出就是输出端的C集是开路的,没有接恒流源,如果直接接负载,完全就没有驱动能力。

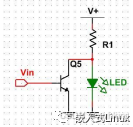

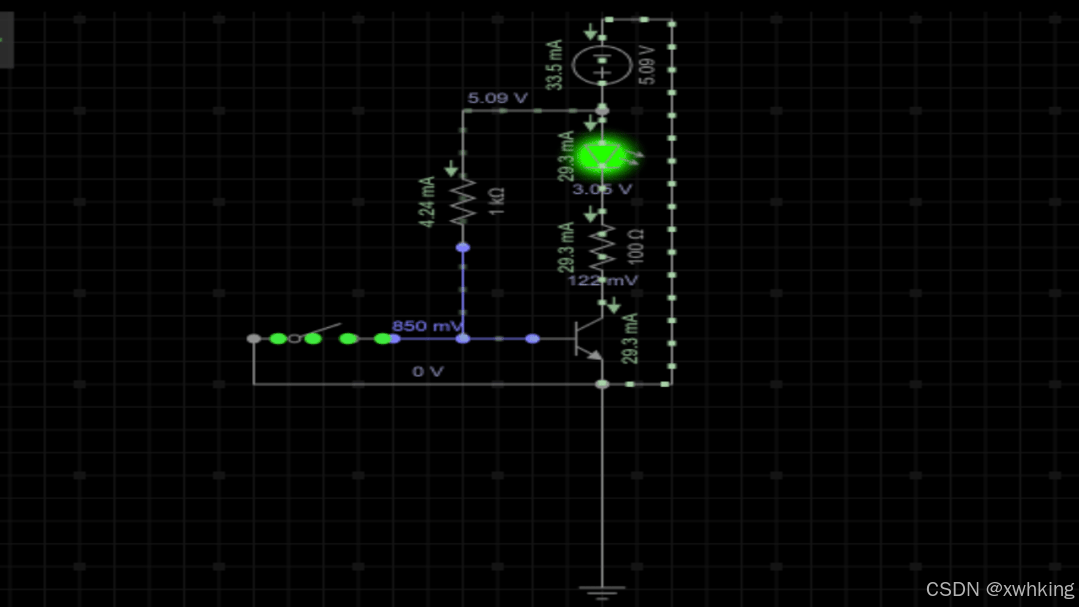

所以,开漏输出接负载的电路我们会这样设计

开漏输出 是指输出端仅通过一个晶体管(通常是 NPN 晶体管)连接到地。当需要输出高电平时,输出引脚处于 开路状态,并不连接到电源,只能通过外部上拉电阻来实现高电平。只有当需要输出低电平时,NPN 晶体管导通,输出端接地。

工作原理图

Vcc

|

R (上拉电阻)

|

|---- Output

|

[NPN]

|

GND

- 输出低电平时:NPN 晶体管导通,输出端直接连接到地(GND)。

- 输出高电平时:NPN 晶体管截止,输出端通过上拉电阻连接到 Vcc。

特点:

- 输出高电平时:输出端处于开路状态,电压由外部上拉电阻决定。没有驱动能力,必须通过外部电路来实现。

- 输出低电平时:通过晶体管导通将输出端拉低。

- 优点:开漏输出可以与多个设备共享一个总线,这对于总线通信非常有用,例如 I2C、1-Wire 协议中。

- 缺点:不能直接驱动高电平,必须依赖上拉电阻。

应用:

开漏输出广泛应用于以下场景:

- I2C 总线:I2C 是一种常见的开漏总线,所有的设备共享两条线路(SDA 和 SCL),每个设备都可以通过拉低总线来发送信号。

- 1-Wire 总线:1-Wire 是另一种开漏总线协议,只有一个引脚用于数据传输和电源供电,外部的上拉电阻用于将数据线拉高。

- 逻辑电平转换:在不同电压水平的电路中,开漏输出和上拉电阻可以帮助不同电平的设备进行通信。

比较:推挽输出与开漏输出

| 特性 | 推挽输出(Push-pull) | 开漏输出(Open-drain) |

|---|---|---|

| 工作原理 | 两个晶体管(NPN 和 PNP)用于拉高和拉低电平 | 只有一个 NPN 晶体管拉低电平,需外部上拉电阻 |

| 输出高电平时 | 输出端连接到 Vcc | 输出端开路,通过上拉电阻拉高电平 |

| 输出低电平时 | 输出端连接到 GND | 输出端连接到 GND |

| 驱动能力 | 可以提供较大的电流 | 只能提供较小的电流,仅能拉低电平 |

| 应用场景 | 驱动负载(如 LED、继电器等) | 总线通信(如 I2C、1-Wire)、逻辑电平转换等 |

总结

- 推挽输出:有两个晶体管控制电流,可以同时输出高电平和低电平,适用于需要驱动较大负载的场合。

- 开漏输出:仅使用一个晶体管,输出高电平时通过上拉电阻实现,适用于总线通信、多个设备共享一个信号线的场合。

参考:https://blog.csdn.net/weiqifa0/article/details/115191377

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?