Intel Spec. Processor Instructions 6 - Processor Instruction Set Reference

I. How to read the instruction set reference pages

- Opcode column

/digital: It indicates that the ModRM byte of the instruction uses only the r/m(register or memory) operand. The reg field of the ModRM byte contains the digit(0...7) that provides an extension to the instruction's opcode

/r: It indicates that the ModRM byte of the instruction contains both a register and an r/m operand

cb,cw,cd,cp: is a 1-byte, 2-byte, 4-byte, or 6-byte, the value following the opcode that is used to specify a code offset and possibly a new value for the code segment register

ib,iw,id: is a 1-byte, 2-byte, 4-byte, immediate operand to the instruction that follows the opcode, ModRM, and SIB bytes.

+rb,+rw,+rd: is a register code from 0~7. rb[0,7] = {al,cl,dl,bl,ah,ch,dh,bh}, rw[0,7] = {ax,cx,dx,bx,sp,bp,si,di}, rd[0,7] = {eax,ecx,edx,ebx,esp,ebp,esi,edi}

- Instruction column

r8: is one of the byte register, {al,cl,dl,bl,ah,ch,dh,bh}

r16: is one of the word register, {ax,cx,dx,bx,sp,bp,si,di}

r32: is one of the dword register, {eax,ecx,edx,ebx,esp,ebp,esi,edi}

r/m8,r/m16,r/m32: is a 1-byte, 2-byte, 4-byte register or memory operand

m8,m16,m32: is a 1-byte, 2-byte, 4-byte memory operand

m: is a memory operand whose type is not checked by the assembler. BTS and other bit instructions for usage

imm8,imm16,imm32: is a byte, word, dword immediate value

rel8,rel16,rel32: is a byte, word, dword label

ptr16:16,ptr16:32: is a FAR label

m16:16,m16:32: is a memory operand containing a full pointer composed of two numbers like the ptr16:16 and ptr16:32

m16&16,m16&32,m32&32: is a memory operand consisting of paired data items whose sizes are indicated on the left and the right side of ampersand. EX: lidt m16&32, lgdt m16&32

moffs8,moffs16,moffs32: is a simple memory variable of type byte, word, dword used by the mov instruction

Sreg: is a segment register, [0,5] = {ES,CS,SS,DS,FS,GS}

- *Clocks column

Gives the number of clock cycles for each form of the instruction, the clock count calculations make the following assumptions:

1. The instruction has been prefetched and decoded and is ready for execution

2. Bus cycles do not require wait states

3. There are no a numeric coprocessor data transfer or local bus hold requests delaying processor access to the bus

4. No exceptions are detected during instruction execution

5. Memory operands are aligned on 4-byte boundaries

- Description column

- Operation section

- Discussion section

- Flags affected section

- Exceptions by mode section

II. How to look up an instruction

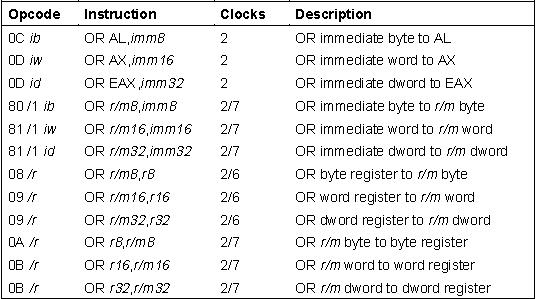

III. Processor instructions

575

575

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?