软件下载

| 软件:Quartus II | 版本:18.0 | ||

| 语言:英文 | 大小:2.62G | ||

| 安装环境:Win11/Win10/Win8/Win7 | |||

| 硬件要求:CPU@2.0GHz 内存@4G(或更高) | |||

| 下载通道①百度网盘丨64位下载链接: https://pan.baidu.com/s/1fiTFBMA149iBoEURslVoKQ 提取码:5678 | |||

| |||

软件介绍

Quartus II是一款综合性PLD/FPGA开发软件,支持原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

安装步骤

1.鼠标右击【Quartus II 18.0(64bit)】压缩包(win11及以上系统需先点击“显示更多选项”)选择【解压到Quartus II 18.0(64bit)】。

2.打开解压后的文件夹,鼠标右击【QuartusSetup-18.0】选择【以管理员身份运行】。

3.点击【Next】。

4.选择【I accept the agreement】,点击【Next>】。

5.修改路径地址中的首字符C可更改软件的安装位置(如:将C改为D表示安装到D盘),点击【Next>】。

6.点击【Next>】。

7.点击【Next>】。

8.软件安装中……

9.取消勾选【Launch USB Blaster …】,点击【Finish】。

10.选择【If you have a……】,点击【OK】(之后弹出的界面请勿关闭)。

11.打开安装包解压后的【Quartus II 18.0(64bit)】文件夹中的【license】文件夹。

12.❶鼠标右击【license.dat】❷选择【打开方式】❸选择【记事本】❹点击【确定】。

13.将打开的文档中的【XXXXXXXXXXX】全部替换为【(nic)ID后的字符】(步骤11后弹出的界面所显示),替换后保存。

14.将保存的文档复制到软件安装位置根目录下(步骤6设置的,我这里为:D:\intelFPGA\18.0)。

15.❶点击【…】❷选择【license】,❸点击【打开】。

16.点击【OK】。

17.点击软件右上角【X】先退出软件。

18.打开安装包解压后的【Quartus II 18.0(64bit)】,鼠标右击【Crack】选择【复制】。

19.鼠标右击桌面【Quartus (Quartus Prime 18.0) Standard Edition】选择【打开文件所在位置】。

20.在空白处鼠标右击选择【粘贴】。

21.鼠标右击粘贴后的【Crack】选择【以管理员身份运行】。

温馨提示

①运行【Crack】前:先关闭“所有杀毒软件(部分电脑自带的“迈克菲”也要关闭)、防火墙、Windows Defender”,否则可能会被杀毒软件误杀无法运行。若已经没有该文件,需重新解压安装包。

22.点击【确定】。

23.点击【确定】。

24.点击【否】。

25.双击桌面【Quartus II 18.0(64bit) (64-Bit)】图标启动软件。

26.安装成功。

题外话

初入计算机行业的人或者大学计算机相关专业毕业生,很多因缺少实战经验,就业处处碰壁。下面我们来看两组数据:

-

2023届全国高校毕业生预计达到1158万人,就业形势严峻;

-

国家网络安全宣传周公布的数据显示,到2027年我国网络安全人员缺口将达327万。

一方面是每年应届毕业生就业形势严峻,一方面是网络安全人才百万缺口。

6月9日,麦可思研究2023年版就业蓝皮书(包括《2023年中国本科生就业报告》《2023年中国高职生就业报告》)正式发布。

2022届大学毕业生月收入较高的前10个专业

本科计算机类、高职自动化类专业月收入较高。2022届本科计算机类、高职自动化类专业月收入分别为6863元、5339元。其中,本科计算机类专业起薪与2021届基本持平,高职自动化类月收入增长明显,2022届反超铁道运输类专业(5295元)排在第一位。

具体看专业,2022届本科月收入较高的专业是信息安全(7579元)。对比2018届,电子科学与技术、自动化等与人工智能相关的本科专业表现不俗,较五年前起薪涨幅均达到了19%。数据科学与大数据技术虽是近年新增专业但表现亮眼,已跻身2022届本科毕业生毕业半年后月收入较高专业前三。五年前唯一进入本科高薪榜前10的人文社科类专业——法语已退出前10之列。

“没有网络安全就没有国家安全”。当前,网络安全已被提升到国家战略的高度,成为影响国家安全、社会稳定至关重要的因素之一。

网络安全行业特点

1、就业薪资非常高,涨薪快 2021年猎聘网发布网络安全行业就业薪资行业最高人均33.77万!

2、人才缺口大,就业机会多

2019年9月18日《中华人民共和国中央人民政府》官方网站发表:我国网络空间安全人才 需求140万人,而全国各大学校每年培养的人员不到1.5W人。猎聘网《2021年上半年网络安全报告》预测2027年网安人才需求300W,现在从事网络安全行业的从业人员只有10W人。

行业发展空间大,岗位非常多

网络安全行业产业以来,随即新增加了几十个网络安全行业岗位︰网络安全专家、网络安全分析师、安全咨询师、网络安全工程师、安全架构师、安全运维工程师、渗透工程师、信息安全管理员、数据安全工程师、网络安全运营工程师、网络安全应急响应工程师、数据鉴定师、网络安全产品经理、网络安全服务工程师、网络安全培训师、网络安全审计员、威胁情报分析工程师、灾难恢复专业人员、实战攻防专业人员…

职业增值潜力大

网络安全专业具有很强的技术特性,尤其是掌握工作中的核心网络架构、安全技术,在职业发展上具有不可替代的竞争优势。

随着个人能力的不断提升,所从事工作的职业价值也会随着自身经验的丰富以及项目运作的成熟,升值空间一路看涨,这也是为什么受大家欢迎的主要原因。

从某种程度来讲,在网络安全领域,跟医生职业一样,越老越吃香,因为技术愈加成熟,自然工作会受到重视,升职加薪则是水到渠成之事。

`黑客&网络安全如何学习

今天只要你给我的文章点赞,我私藏的网安学习资料一样免费共享给你们,来看看有哪些东西。

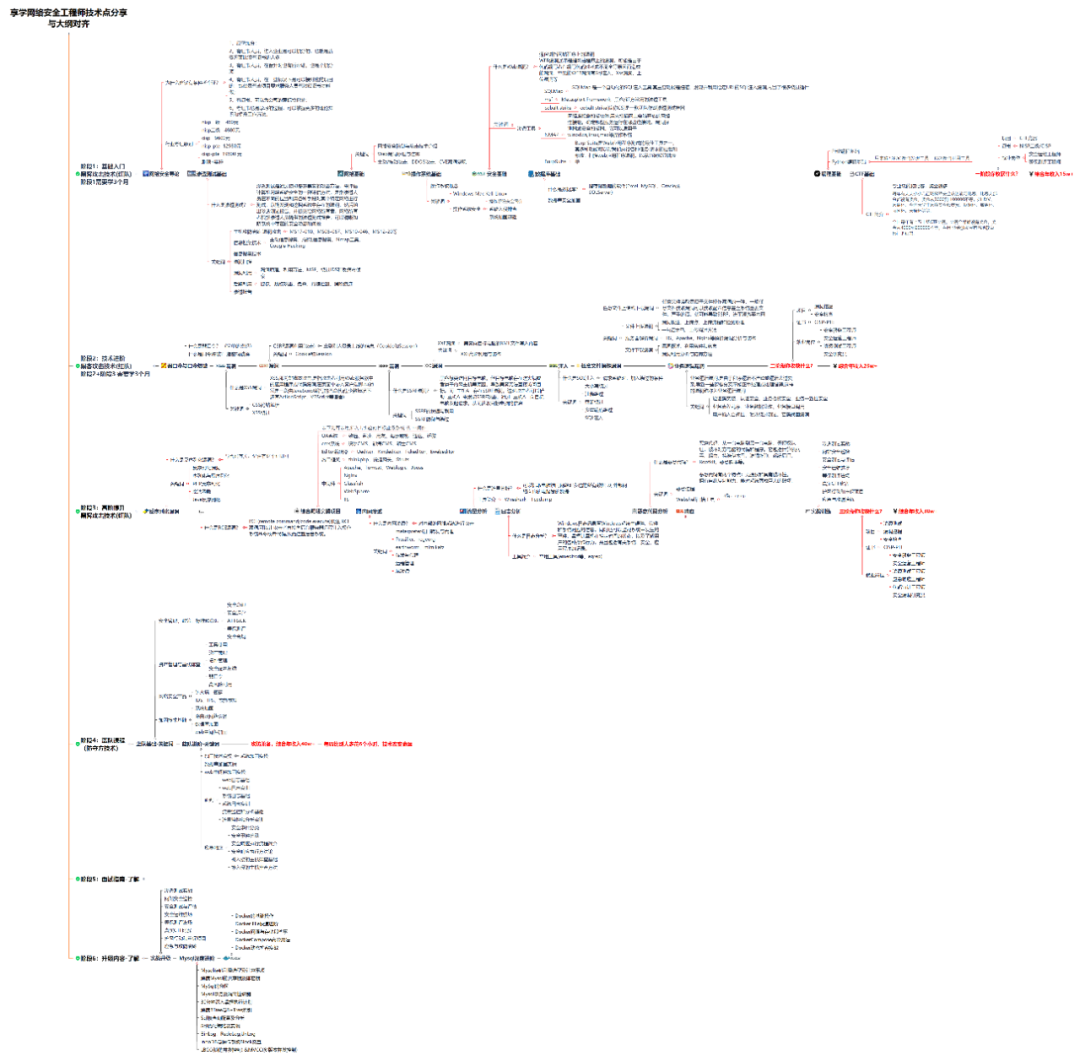

1.学习路线图

攻击和防守要学的东西也不少,具体要学的东西我都写在了上面的路线图,如果你能学完它们,你去就业和接私活完全没有问题。

2.视频教程

网上虽然也有很多的学习资源,但基本上都残缺不全的,这是我自己录的网安视频教程,上面路线图的每一个知识点,我都有配套的视频讲解。

内容涵盖了网络安全法学习、网络安全运营等保测评、渗透测试基础、漏洞详解、计算机基础知识等,都是网络安全入门必知必会的学习内容。

(都打包成一块的了,不能一一展开,总共300多集)

因篇幅有限,仅展示部分资料,需要点击下方链接即可前往获取

CSDN大礼包:《黑客&网络安全入门&进阶学习资源包》免费分享

3.技术文档和电子书

技术文档也是我自己整理的,包括我参加大型网安行动、CTF和挖SRC漏洞的经验和技术要点,电子书也有200多本,由于内容的敏感性,我就不一一展示了。

因篇幅有限,仅展示部分资料,需要点击下方链接即可前往获取

CSDN大礼包:《黑客&网络安全入门&进阶学习资源包》免费分享

4.工具包、面试题和源码

“工欲善其事必先利其器”我为大家总结出了最受欢迎的几十款款黑客工具。涉及范围主要集中在 信息收集、Android黑客工具、自动化工具、网络钓鱼等,感兴趣的同学不容错过。

还有我视频里讲的案例源码和对应的工具包,需要的话也可以拿走。

因篇幅有限,仅展示部分资料,需要点击下方链接即可前往获取

CSDN大礼包:《黑客&网络安全入门&进阶学习资源包》免费分享

最后就是我这几年整理的网安方面的面试题,如果你是要找网安方面的工作,它们绝对能帮你大忙。

这些题目都是大家在面试深信服、奇安信、腾讯或者其它大厂面试时经常遇到的,如果大家有好的题目或者好的见解欢迎分享。

参考解析:深信服官网、奇安信官网、Freebuf、csdn等

内容特点:条理清晰,含图像化表示更加易懂。

内容概要:包括 内网、操作系统、协议、渗透测试、安服、漏洞、注入、XSS、CSRF、SSRF、文件上传、文件下载、文件包含、XXE、逻辑漏洞、工具、SQLmap、NMAP、BP、MSF…

因篇幅有限,仅展示部分资料,需要点击下方链接即可前往获取

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?