双优先编码器

要求设计输入8位reg信号,输出是双优先级,分别用3位二进制代码表示最高优先级和次最高优先级。

1、列出真值表

2、设计电路、编写代码

3、设计测试电路代码

4、综合

5、用测试代码测试

6、设计实验电路(描述如何在实验室完成电路的硬件测试和验证)

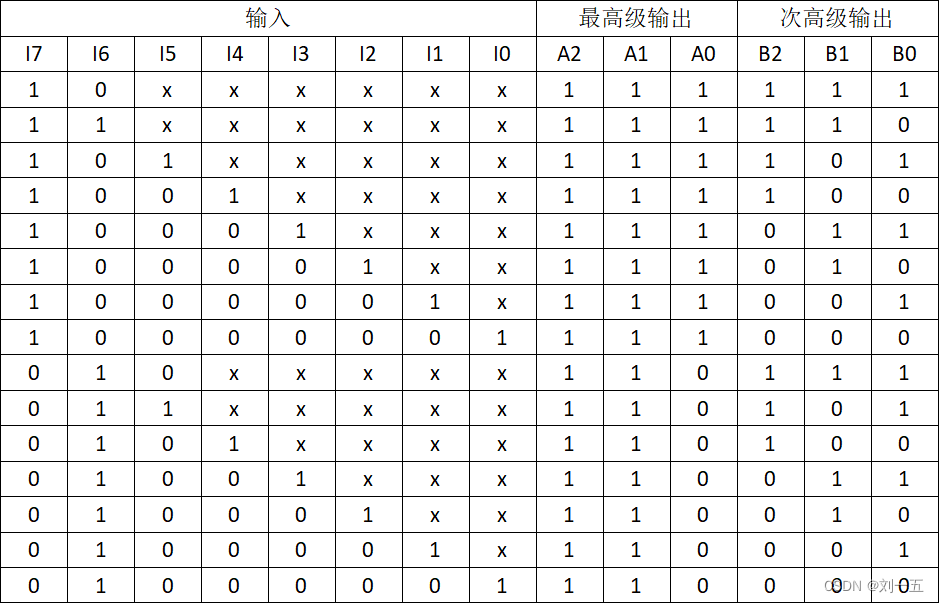

1、真值表

普通的优先编码器就是只对最高的输入响应,最高位无输入才对次高位进行响应,最高位、次高位都无输入才对第三高位进行响应,依次类推。。。

而双优先编码器是对输入中最高的两位进行响应,例如输入是[7:0]=01011010,第7位无输入,第6位有输入,第5位无输入……那么输出最高位为6,输出次高位为4。

考虑到输入只有1位的情况,那么该位作为最高位,次高位输出为7(在输入≥2位的情况下,次高位不可能为7)。

对应的真值表如下:

2、代码

module DualPriorityEncoder(input wire [7:0]datain,

output wire [2:0]St_priority,

output wire [2:0]Nd_priority);

reg St_flag;

reg Nd_flag;

reg [2:0]St_pri,Nd_pri;

always @* begin:fy

integer i;

St_flag=1'b0;

Nd_flag=1'b0;

$display(datain[1]);

for(i=7;i>=0;i=i-1)begin

if(datain[i]==1&&St_flag==0)begin

St_pri=i;

St_flag=1'b1;

end

else if(datain[i]==1&&St_flag==1&&Nd_flag==0)begin

Nd_pri=i;

Nd_flag=1'b1;

end

end

$display(St_priority,Nd_priority);

// if(Nd_flag==1'b0) Nd_pri=3'b111;

end

assign St_priority=St_pri;

assign Nd_priority=Nd_pri;

endmodule

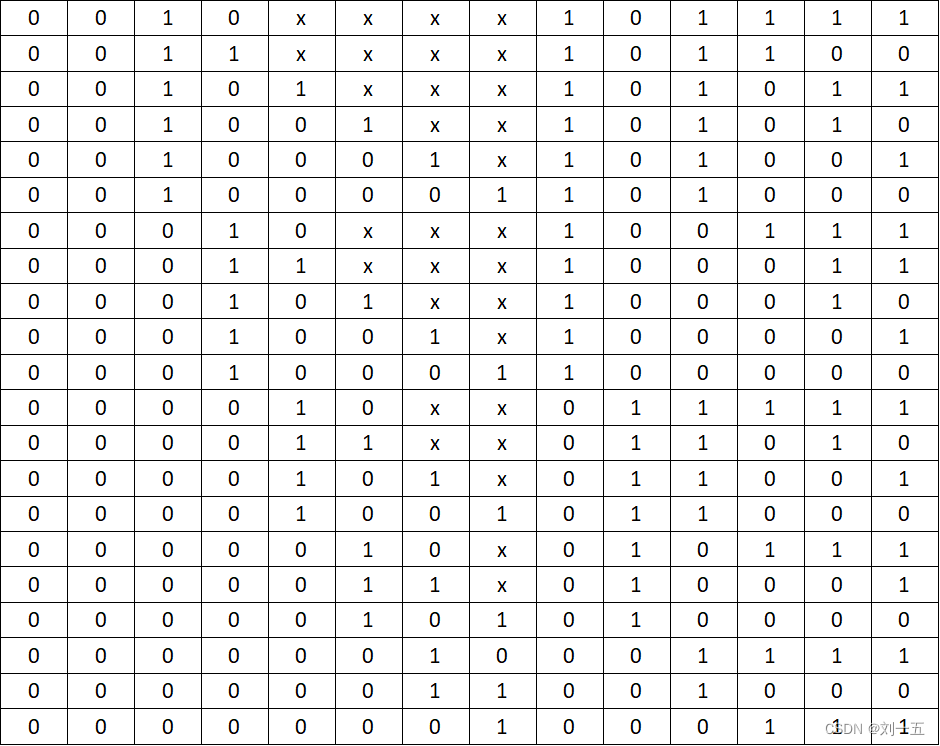

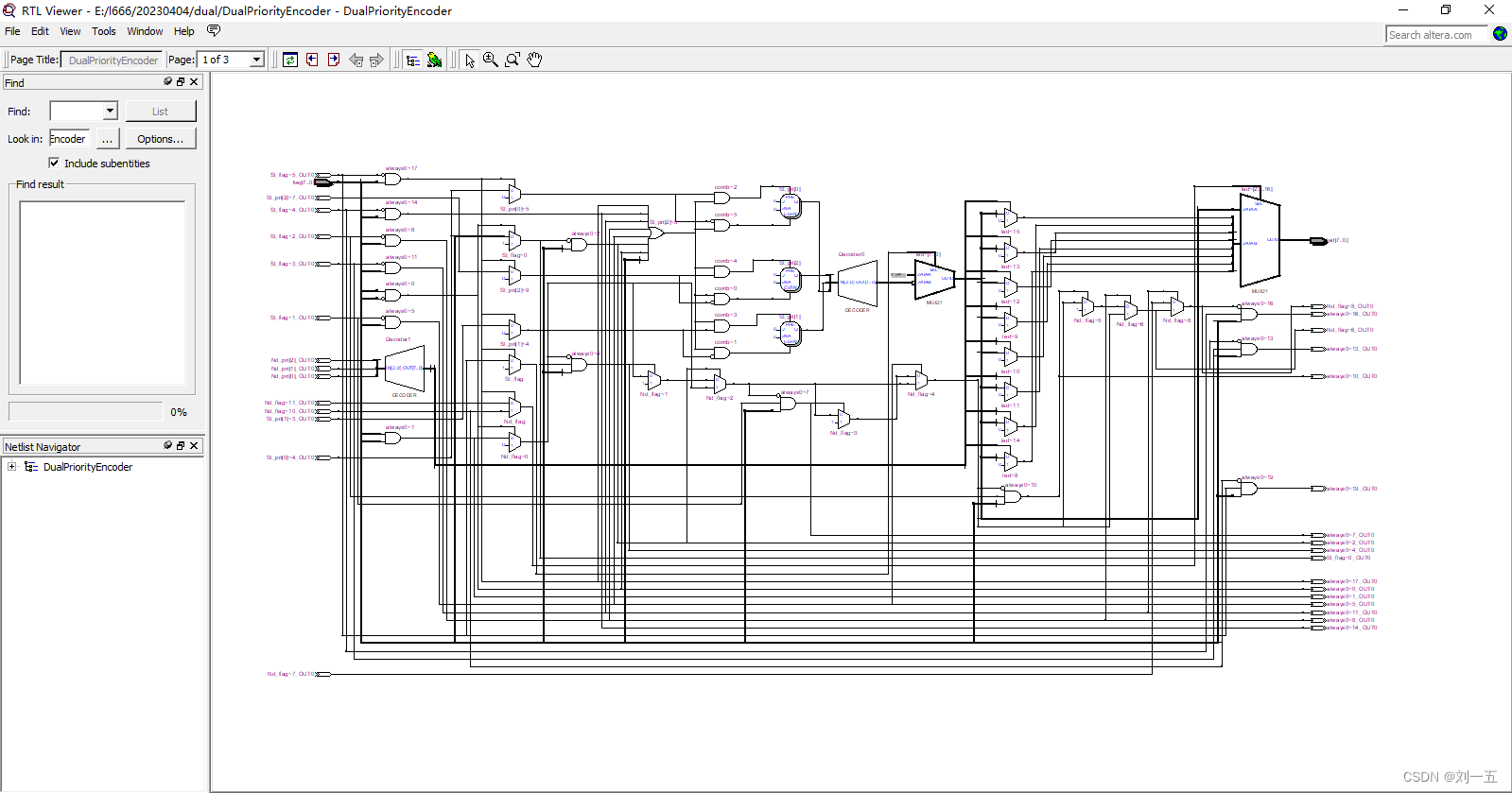

得到的RTL图如下:

3、测试代码

`timescale 1ns/100ps

module tb_DualPriorityEncoder;

reg[7:0]datain_1;

wire[2:0]St_priority_1,Nd_priority_1;

reg St_flag,Nd_flag,clk;

parameter CLK_PER=10;

always #(CLK_PER/2) clk=~clk;

initial begin

datain_1=8'b00000000;

// St_pri=1'b0;

// Nd_pri=1'b0;

St_flag=1'b0;

Nd_flag=1'b0;

clk=1'b0;

# 320 $stop(2);

end

always @(posedge clk)

datain_1=datain_1+1;

DualPriorityEncoder DPE_1(.datain(datain_1),.St_priority(St_priority_1),.Nd_priority(Nd_priority_1)); //实例化被测模块

endmodule

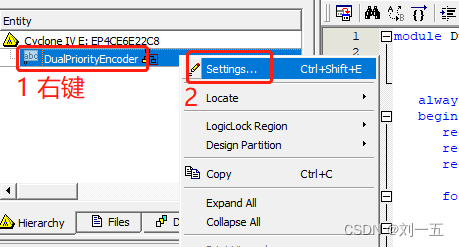

4、用测试代码测试

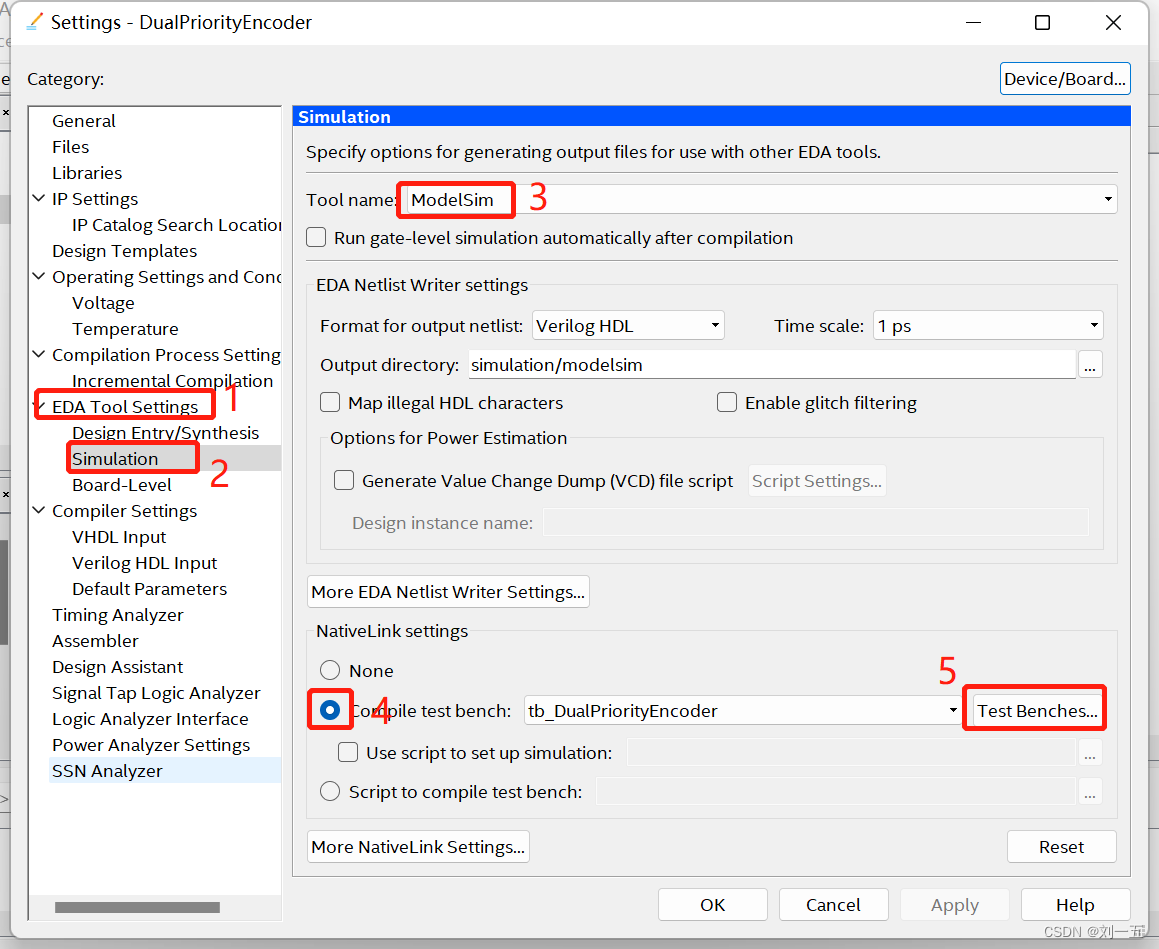

模块【右键】➡️【Settings】➡️【EDA Tools Settings】➡️【Simulation】

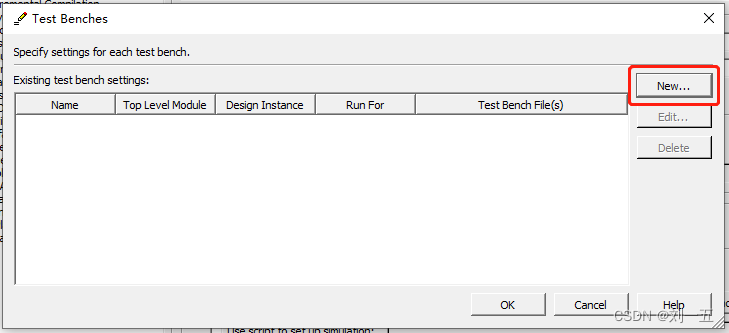

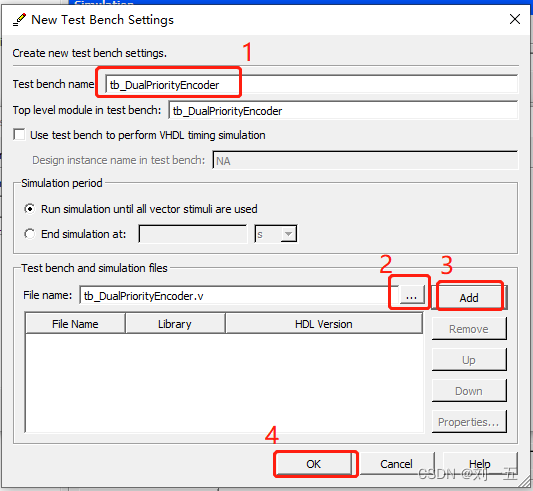

【Compile Test Bench】,把文件添加进去即可

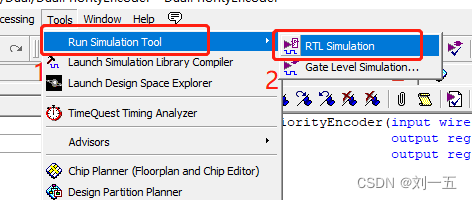

添加完成后,【Tools】➡️【Run Simulation Tool】➡️【RTL Simulation】

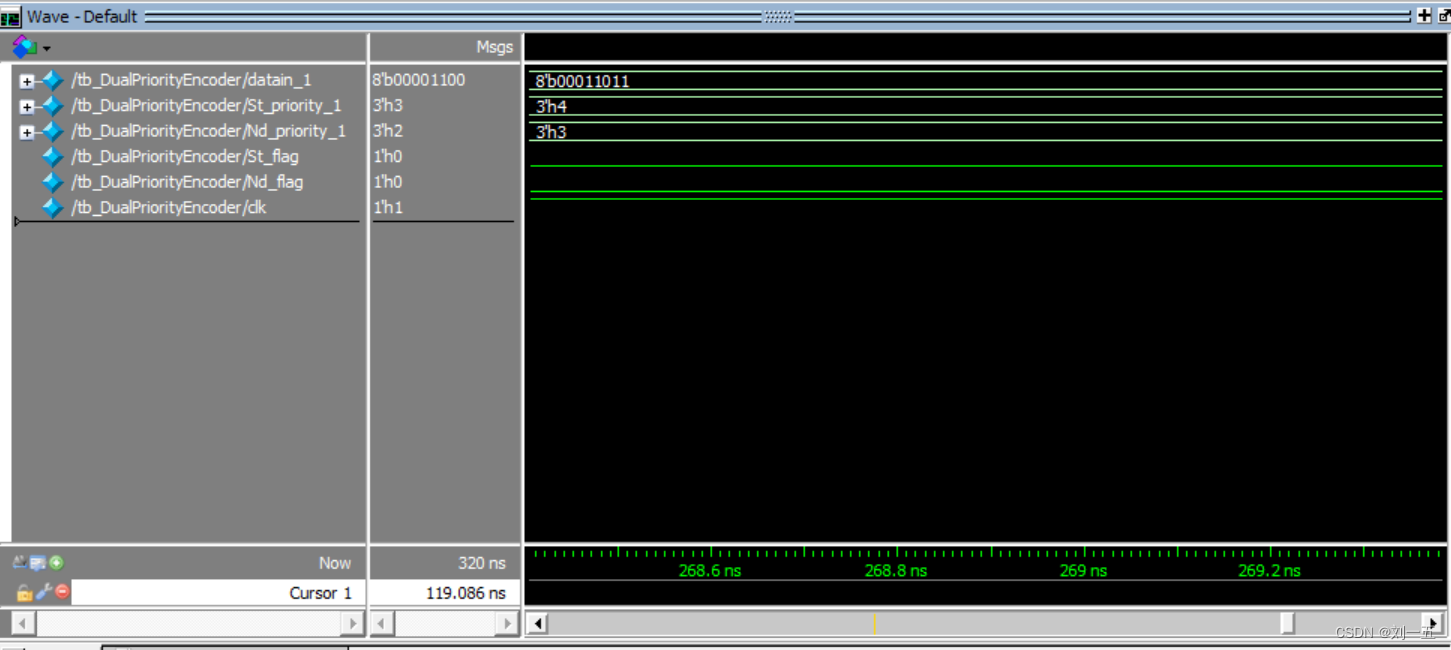

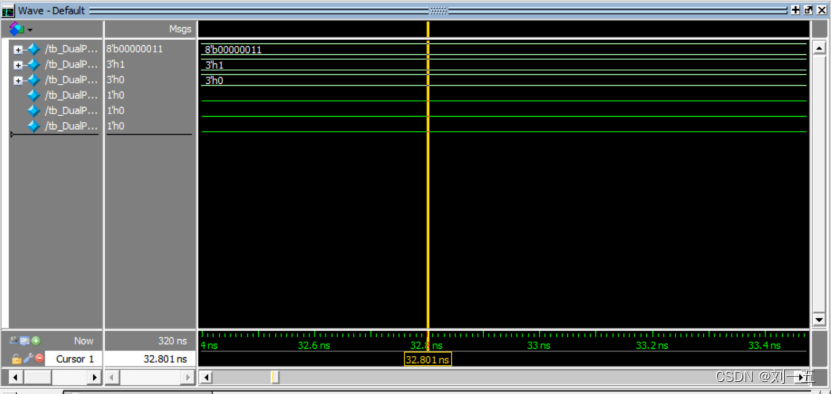

仿真结果如下所示,

当输入的8位信号是00011011时,最高优先位是4(第5位),次优先位为3(第4位),符合双优先编码器的功能。

当输入的8位信号是00000011时,最高优先位是1(第2位),次优先位为0(第1位),符合双优先编码器的功能。

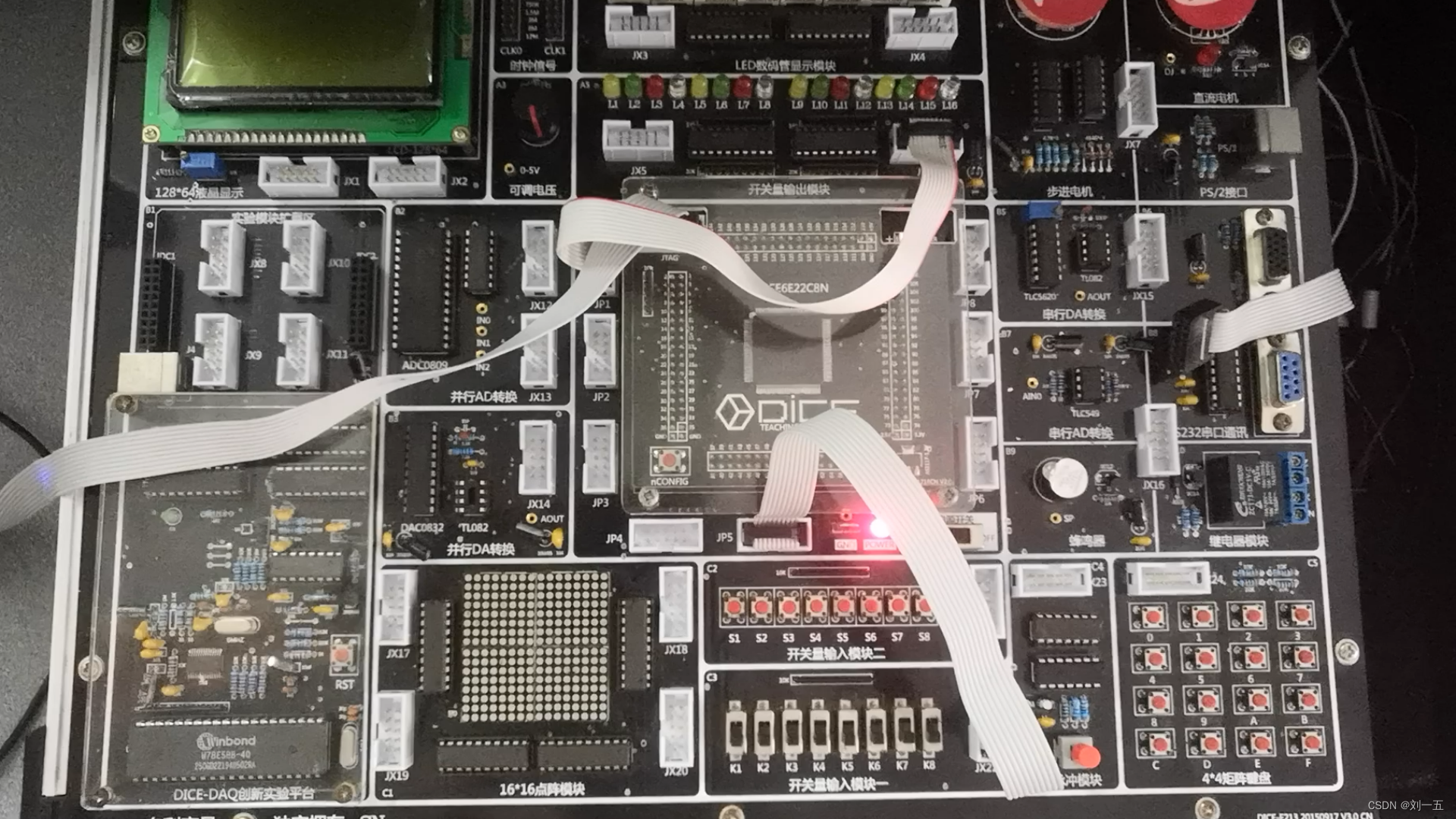

5、用实验箱完成验证

用8个按键K0~K7表示8路信号的输入,

用8个LED灯L7~L0其中两个的亮起来表示最高位信号和次高位信号。

当只有一个信号输入时,只有一个LED灯亮起;

无信号输入时,所有LED灯保持灭的状态。

(1)修改代码如下:

module DualPriorityEncoder(input wire [7:0]key,

output reg [7:0]led );

reg St_flag;

reg Nd_flag;

reg [2:0]St_pri,Nd_pri;

always @* begin:fy

integer i;

led=8'b11111111;

St_flag=1'b0;

Nd_flag=1'b0;

for(i=7;i>=0;i=i-1)begin

if(key[i]==1&&St_flag==0)begin

St_pri=i;

St_flag=1'b1;

end

else if(key[i]==1&&St_flag==1&&Nd_flag==0)begin

Nd_pri=i;

Nd_flag=1'b1;

end

end

if(St_flag==1) led[St_pri]=0;

if(Nd_flag==1) led[Nd_pri]=0;

end

endmodule

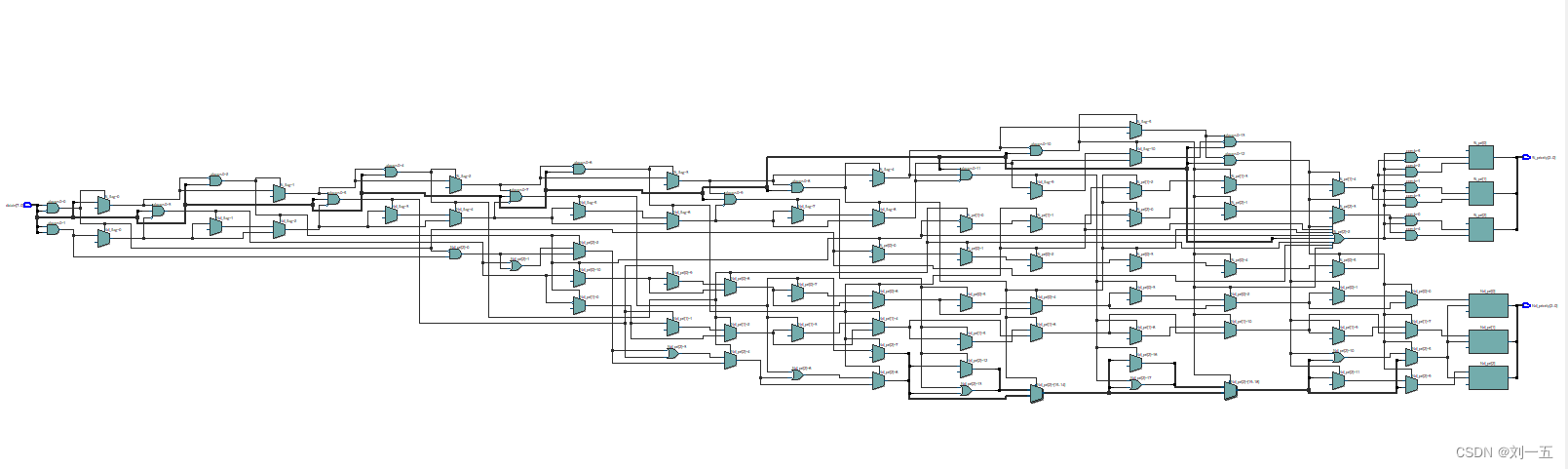

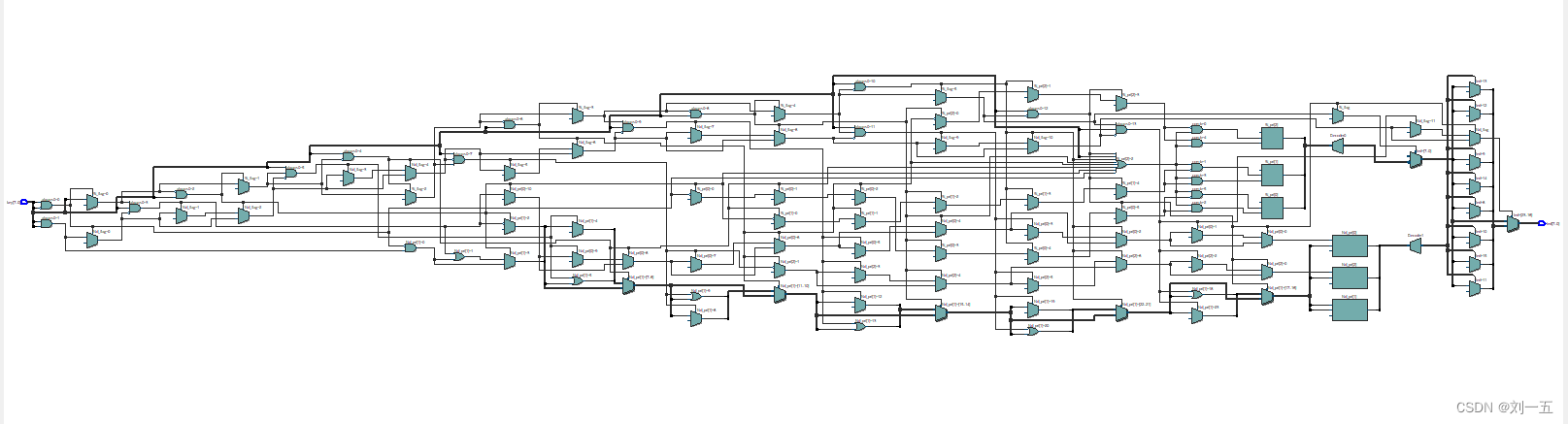

(2)对应的RTL图

Quartus 12对应的RTL图:

Quartus 18.0对应的RTL图:

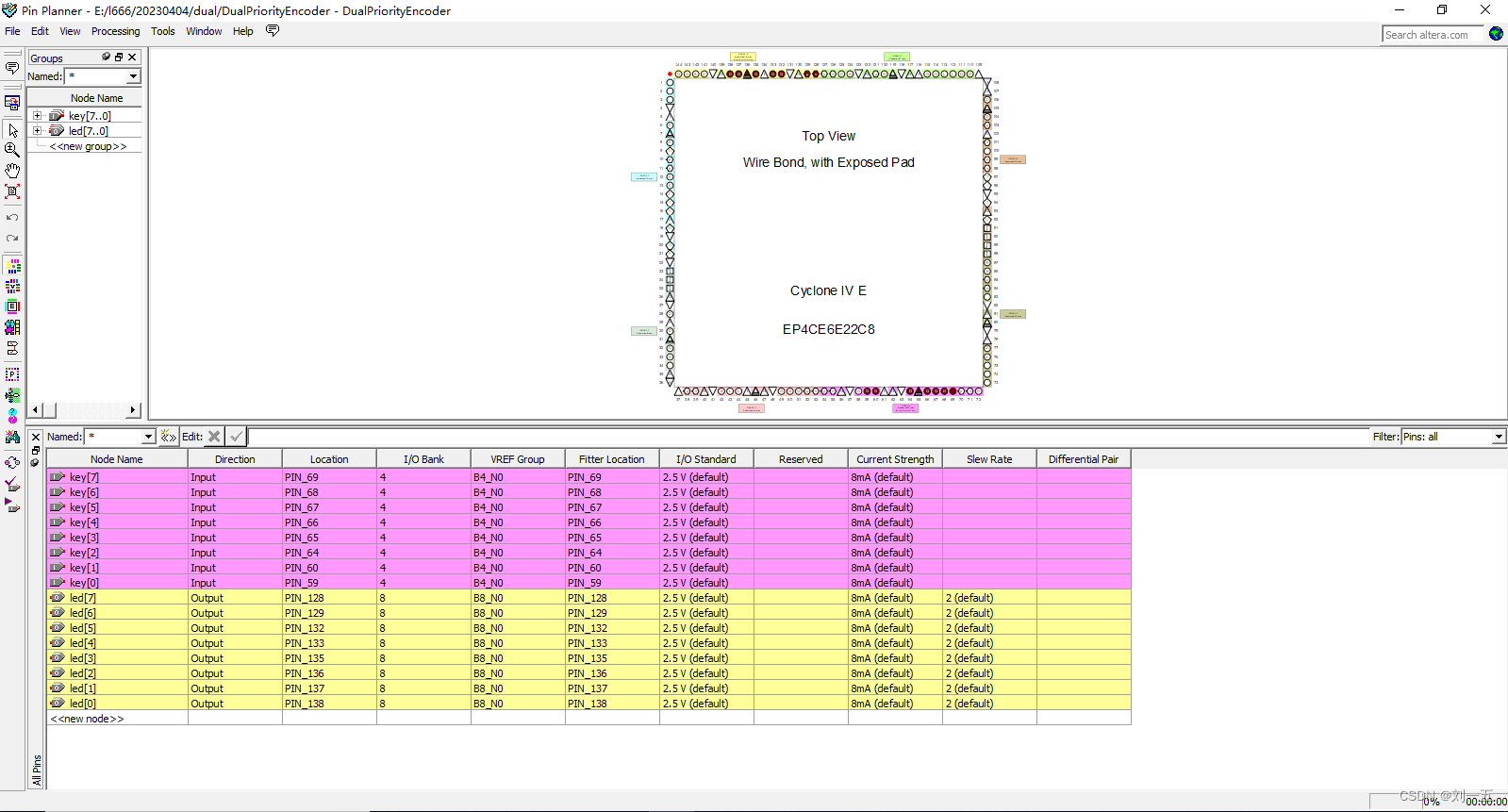

(3)引脚分配与接线

引脚分配接线如下

JP1连接到JX5或JX6,JP5连接到JX22。

(为什么这样接线可参考《【FPGA实验2】二进制转为格雷码》➡️三、试验箱实验➡️3、引脚分配)

(3)实验现象:

【FPGA实验3】双优先编码器

3885

3885

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?