程序:

module uart_byte_tx(

input Data,Send_en,Clk,Reset_n,bit,

output uart_tx,Tx_Done

);

//本实例比特率定为9600

wire [2:0] Baud_set;

wire [7:0] Data;

reg uart_tx,Tx_Done;

reg [15:0] counter0;

reg [3:0] counter1;

reg [12:0] Time;

always@(*) begin

case (Baud_set)

0:Time = 5208;//9600波特率

1:Time = 2604;//19200波特率

2:Time = 1302;//38400波特率

3:Time = 868;//57600波特率

4:Time = 434;//115200波特率

default:Time=0;

endcase

end

always@(posedge Clk or negedge Reset_n)

if (!Reset_n)

counter0<=0;

else if (Send_en) begin

if (counter0==Time-1)

counter0<=0;

else

counter0<=counter0+1'b1;//不同的波特率选择不同的时间间隔

end

else

counter0<=0;

always@(posedge Clk or negedge Reset_n)

if (!Reset_n)

counter1<=0;

else if (Send_en) begin

if(counter0==1)

begin

if (counter1==12)

counter1<=0;

else

counter1<=counter1+1'b1;

end

end

else

counter1<=0;

//11个状态为一次传输

always@(posedge Clk or negedge Reset_n)

if (!Reset_n) begin

uart_tx<=1'b1;

Tx_Done<=1'b0; end

else

case(counter1)

1: begin uart_tx <= 0;Tx_Done<=0;end//起始位

2: uart_tx <= Data[0];

3: uart_tx <= Data[1];

4: uart_tx <= Data[2];

5: uart_tx <= Data[3];

6: uart_tx <= Data[4];

7: uart_tx <= Data[5];

8: uart_tx <= Data[6];

9: uart_tx <= Data[7];

10: uart_tx <= 1;//结束位

11: begin uart_tx <= 1;Tx_Done<=1'b1; end //传输完成信号

default uart_tx<=1;

endcase

endmodule

仿真程序:

`timescale 1ns / 1ns

module uart_byte_tb();

reg Clk,Reset_n,Send_en;

reg [2:0] bit;

reg [7:0] Data;

wire uart_tx,Tx_Done;

uart_byte_tx uart_byte_inst0(

.Data(Data),

.Send_en(Send_en),

.Clk(Clk),

.Reset_n(Reset_n),

.bit(bit),

.uart_tx(uart_tx),

.Tx_Done(Tx_Done)

);

initial Clk=1;

always #10 Clk=~Clk;

initial begin

Reset_n=0;

Send_en=0;

Data=0;

bit=4;

#200001;

Reset_n=1;

Data=8'b0100_1101;

Send_en=1;

#20;

@(posedge Tx_Done)

Send_en=0;

#200001;

Data=8'b0101_1001;

Send_en=1;

#20;

@(posedge Tx_Done)

Send_en=0;

#200001;

$stop;

end

endmodule

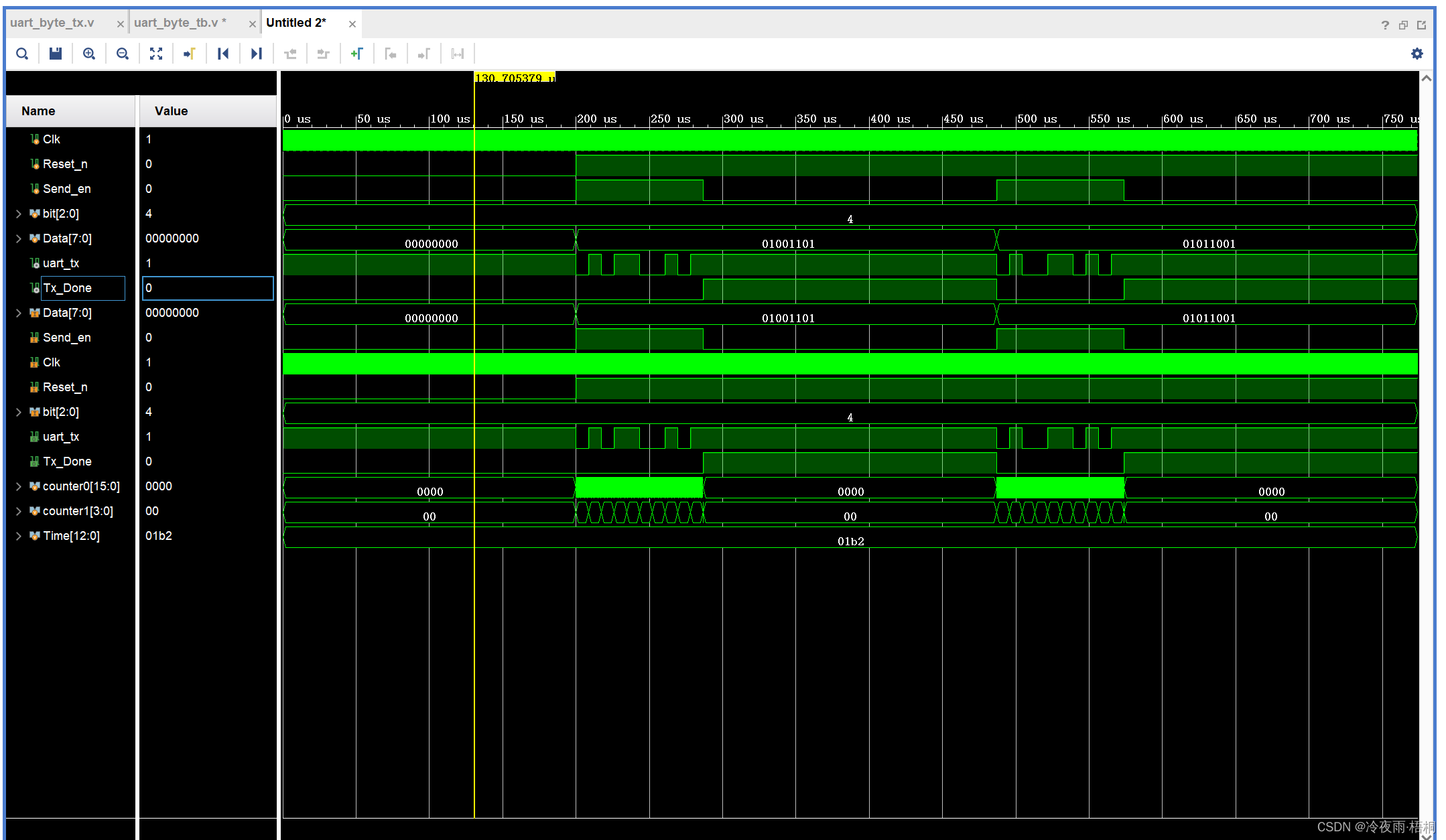

仿真结果:符合预期

该博客详细介绍了UART(通用异步收发传输器)的字节传输模块设计,包括9600到115200不同波特率的设置,以及起始位、数据位、停止位的传输过程。通过Verilog代码实现并进行了仿真,仿真结果符合预期。

该博客详细介绍了UART(通用异步收发传输器)的字节传输模块设计,包括9600到115200不同波特率的设置,以及起始位、数据位、停止位的传输过程。通过Verilog代码实现并进行了仿真,仿真结果符合预期。

2413

2413

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?