1.module

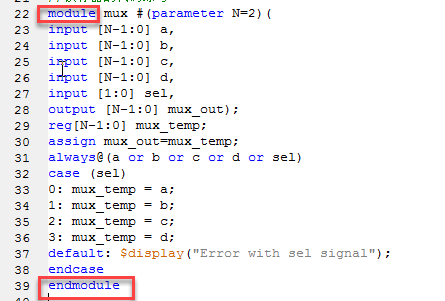

一个module就是一个完整的电路,如果有N个模块,则N个模块将会通过某种机制结合起来。组成一个大的电路,N个模块是独立运行的,并且是并行执行的。以下图选择器为例。

22-29是端口列表以及申明区,30-39是电路行为描述区。

2.赋值语句

赋值语句有连续赋值语句、过程赋值语句、过程连续赋值语句。

Assign赋值语句: 连续赋值语句,输入变化时输出一定会立刻响应,且整个过程持续不断的。多用于描述组合电路,常用于数据流行为建模。连续赋值用"="表示,并且只能对线网型变量不能对寄存器变量赋值。

过程赋值(Procedure Assignments):赋值的对象是寄存器、实数、整数或时间变量,只有在initial和always中使用。

过程赋值语句包括阻塞赋值和非阻塞赋值语句。

过程连续赋值语句(Procedural Continuous Assignments):在过程内对变量或者线网进行连续赋值。

| 阻塞赋值“=” | 非阻塞赋值“<=” |

| 阻塞赋值完成后才允许下一条语句的执行 | 在赋值开始时计算右值,本次仿真周期结束时才更新被赋值变量 |

| 赋值一旦完成左边的变量值立刻发生变化 | 同一顺序块中,非阻塞赋值表达式的书写顺序不影响赋值的结果 |

3.case语句语法

利用case语句描述组合电路时,要注意必须给出缺省项,防止产生锁存电路。锁存电路会带来额外的时钟延迟,并且引入异步时序,不适合常规电路设计。

4.always语句

图中31行所描述的always语句表明电路行为将被重复执行,执行机制是通过对敏感变量表驱动实现的。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?