计算机的基本组成

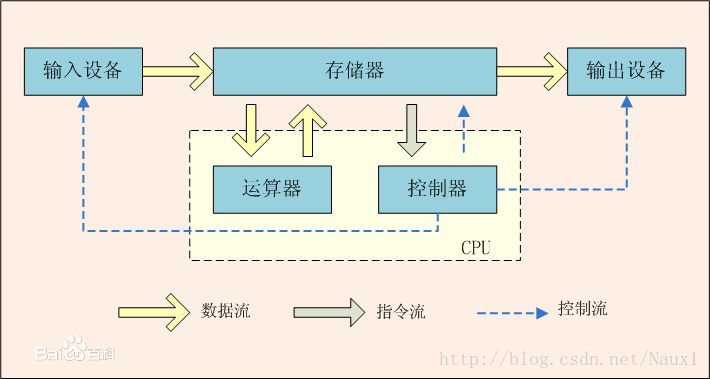

冯 诺依曼计算机的特点:

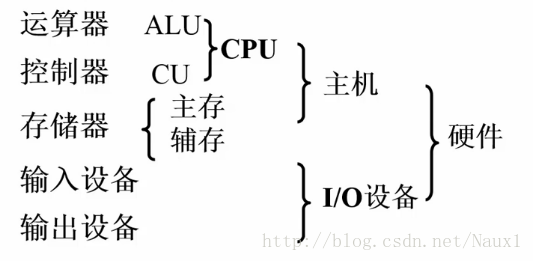

1. 计算机由五大部件组成(输入设备,输出,存储器,运算器,控制器)

2. 指令和数据以同等地位存于存储器,可按地址寻址

3. 指令和数据用二进制表示

4. 指令由操作码和地址码组成

5. 存储程序

6. 以运算器为中心

存储器的基本组成

存储体由若干个存储单元构成,存储单元由存储元件(0/1)构成(存储体相当于大楼,存储单元就是房间,存储元件就是床位(有人/无人))

存储单元 存放一串二进制代码

存储字 存储单元中二进制代码的组合

存储字长 存储单元中二进制代码位数

每个存储单元赋予一个地址(按地址访问)

MAR 存储器地址寄存器(存储单元的地址)反映存储单元的个数

MDR 存储器数据寄存器 反映存储字长

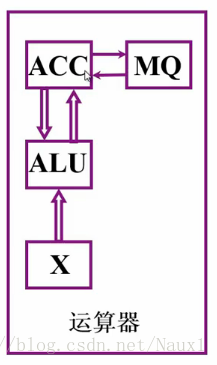

运算器的基本结构

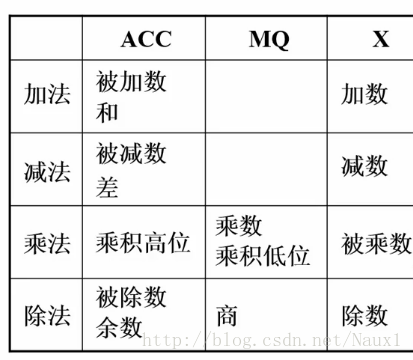

ACC和X作为运算的输入,ACC也用于保存运算的结果,相乘法操作运算长度会增加一倍,增加的长度保存在MQ当中

<1 加法操作过程

操作码指出当前操作是加法操作

寄存器只涉及到ACC和X寄存器

指令只有一个操作数,另一个操作数隐含在ACC当中

先有一个输入指令,将数据输入到ACC当中,因此初态ACC当中保存了被加数,把加数从指定的内存单元取出,保存到X寄存器当中。

执行加法指令的第一个步骤就是:

[M] ——> X 将M地址中的数据放入X寄存器当中

现在两个操作数都被放入指定的寄存器中

加法操作在ALU中完成,保存在ACC当中

<2 减法操作过程

操作码指出当前操作是减法操作

先将被减数取出来放入ACC这个寄存器当中

被减数——>ACC

减数放在地址是M当中

[M]——> X

然后就可以进行减法操作

[ACC]-[X]——>ACC

<2 乘法操作过程

操作码指出当前操作是乘法操作

地址码指出乘数所在单元的地址

被乘数——> ACC

(乘数)[M] ——> MQ

[ACC] ——> X

乘法是通过累加和移位的方法完成的,因此要有寄存器保存累加的内容,在这之前要给该寄存器清理。即ACC

0 ——> ACC

[X] x [MQ] ——> ACC(高位)//MQ(低位)

这些操作的先后顺序,就是由控制器控制的

<2 除法操作过程

操作码指出我们要做除法

地址码指出我们的除数保存在内存单元为M的地址当中

被除数 ——> ACC

除数 [M] ——> X

[ACC] / [M] ——>MQ(商) 余数在ACC当中

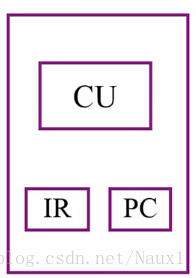

控制器的基本结构

控制器的功能:

解释指令

保证指令的按序执行

控制器的基本组成

完成一条指令的步骤:

取指令 (PC)— 分析指令 (IR) — 执行指令 (CU控制单元)

PC存放当前欲执行指令的地址,下一条指令 (PC)+1 ——>PC

控制单元从IR中取出指令的操作码进行分析

IR存放的当前欲执行的指令

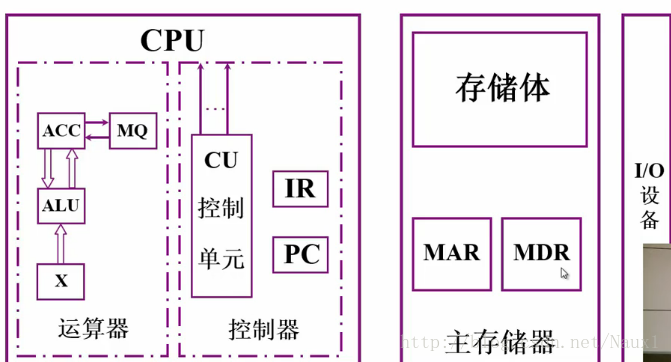

运算器,控制器,存储器构成了主机

运算器的核心是ALU(还有三个寄存器是ACC,X,MQ)

控制器包含了CU,IR,PC

存储器包含存储体,MAR,MDR

因此硬件系统的结构图

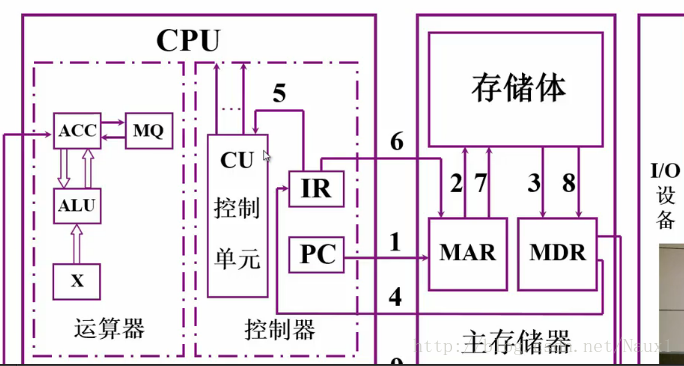

主机完成一条指令的过程

以取数指令为例

取指令—>分析指令 —> 完成指令

1. 取指令

指令的地址保存在PC当中,指令内容保存在存储体当中

PC将指令地址 —> MAR,MAR —> 存储体,存储体把指定存储单元当中存储的取数指令取出,送入MDR。再将MDR中保存的指令 —> IR(保存指令)

2. 分析指令

IR保存指令的操作码送入CU,经过译码以后,控制单元执行指令相应操作,因为此时解析的是取数指令,即将指定地址的数据放入ACC中

3. 执行指令

因此IR将地址码 —> MAR ,MAR —>存储体,存储体将该地址当中的数据 —> MDR , MDR中的数据 —>ACC

以存数指令为例

取指令—>分析指令 —> 完成指令

1. 取指令

指令的地址保存在PC当中,指令内容保存在存储体当中

PC将指令地址 —> MAR,MAR —> 存储体,存储体把指定存储单元当中存储的指令取出,送入MDR。再将MDR中保存的指令 —> IR(保存指令)

2. 分析指令

IR保存指令的操作码 —> CU CU对指令进行分析

3. 执行指令

CU控制将IR中的地址码给MAR , MAR —> 存储体,存储体知道存数的地址,将ACC中的数据—>MDR, MDR —> 存储体 , 将数据存入该地址当中

ax^2+bx+c程序执行过程

将程序通过输入设备送至计算机

程序首地址 —> PC

启动程序运行

<1 PC第一条指令 — 取数指令

1. 取指令(取完后将PC+1 —> PC)

PC —> MAR —> 存储体(M) —> MDR —> IR

2. 分析指令

将指令的操作码(OP)取出 —> CU

3. 执行指令

IR将地址码部分(Ad) —> MAR —>M中取出数据 —> MDR —> ACC

<2 乘法指令

<3 打印结果

<4 停机

*计算机硬件的主要技术指标

*1. 机器字长

CPU一次能处理数据的位数

与CPU中的寄存器位数有关

机器字长越长,机器性能越好

(如一个cpu可以对两个8位的二进制数做加法,结果还是一个8位二进制数,此cpu是8位)

2. 运算速度

- 主频

- 核数:每个核支持的线程数

- CPI :执行一条指令所需时钟周期数

- MIPS :每秒执行百万条指令

FLOPS :每秒浮点运算次数

3. 存储容量

主存容量:

<1 存储单元个数x存储字长 如:MAR MDR容量(10 8 1K(2^10) x 8位)

<2 字节数

赋存容量:

字节数

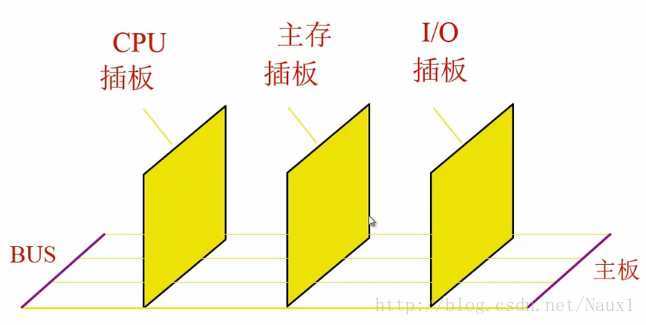

总线

什么是总线?

总线是连接各个部件的信息传输线

是各个部件共享的传输介质

总线上信息的传输:

串行 :把要传输的信息一位一位的放到总线上去,然后接收方一位一位接收

并行:把要传输的信息多位一起放到总线上去,然后接收方一起接收,需要多条数据线

一般并行传输距离较短,串行较长

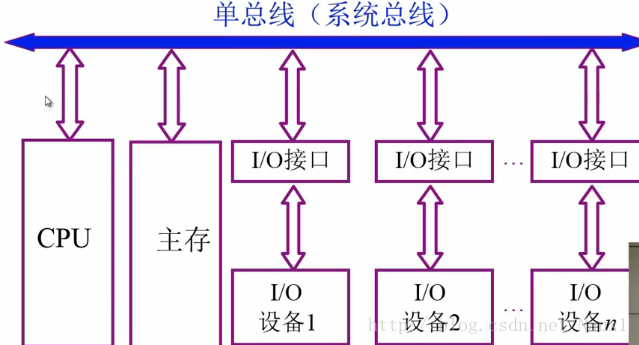

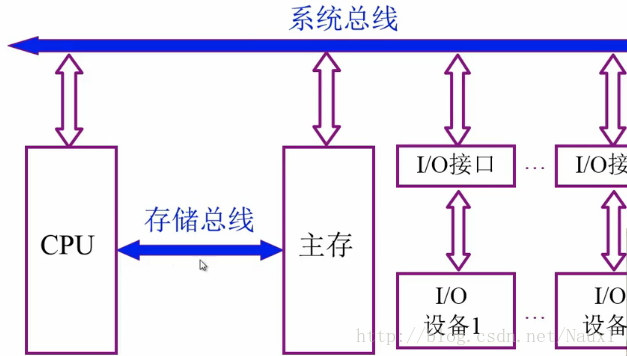

1. 单总线结构框图

计算机的各个部件均由系统总线相连,在单总线结构中,CPU与主存之间、CPU与I/O设备之间、I/O设备与主存之间、各种设备之间都通过系统总线交换信息。单总线结构的优点是控制简单方便,扩充方便。但由于所有设备部件均挂在单一总线上,使这种结构只能分时工作,即同一时刻只能在两个设备之间传送数据,这就使系统总体数据传输的效率和速度受到限制

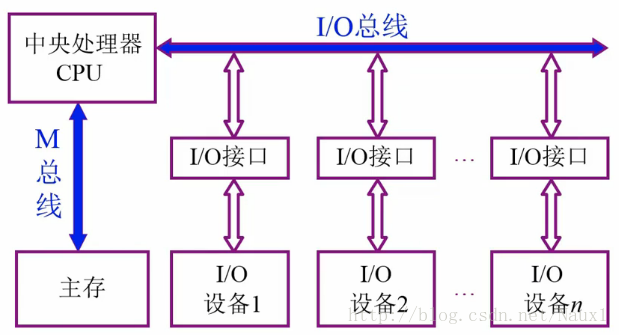

2.面向CPU的双总线结构框图

缺点:主存要与外部设备进行信息的传输,只能以CPU进行媒介

3.以存储器为中心的双总线结构框图

总线的分类

1. 片内总线 :芯片内部的总线

2. 系统总线

数据总线 (双向,与机器字长,存储字长有关), 地址总线 (单向,与储存地址,I/O地址有关) , 控制总线(有出,有入)

3. 通信总线

用于计算机系统之间或计算机系统与其他系统之间的通信

总线特性及性能指标

一 . 总线物理实现

总线印刷在主板上,在总线上留出一些接口,计算机系统其他的部件可以通过这些接口连接在主板上

三. 总线特性

1. 机械特性 : 尺寸,形状,管脚数

2. 电气特性 : 传输方向和有效的点平范围

3. 功能特性 : 每根传输线的功能

4. 时间特性

二. 总线的性能指标

1. 总线宽度 : 总线的根数

2. 标准传输率 : 每秒传输的最大字节数

3. 时钟同步/异步

4. 总线复用 : 地址线(8086有20条,有16条作为数据线复用)和数据线复用

5. 信号线数 : 地址线,数据线和控制线的总和

6. 总线控制方式

7. 其他指标

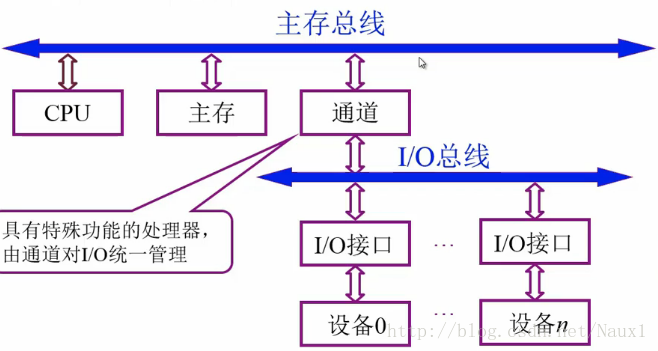

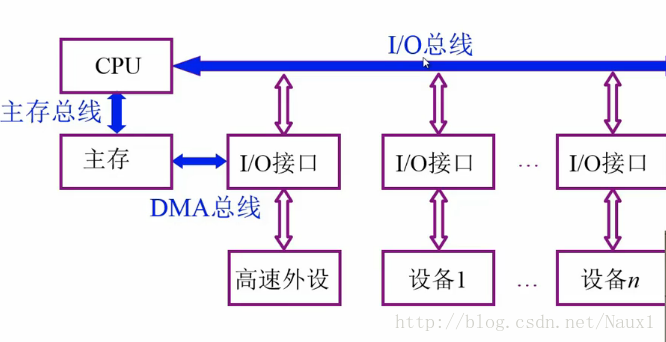

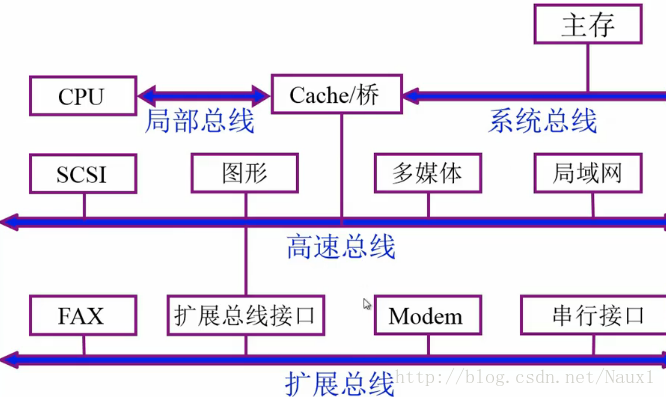

总线结构

1. 单总线结构

2. 多总线结构

<1 双总线结构

<2 三总线结构

<2 四总线结构

总线控制

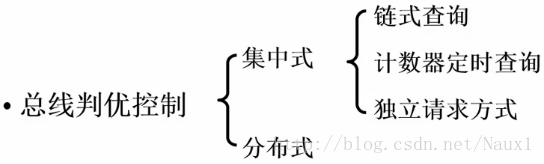

1. 总线判优控制

主设备 : 对总线有控制权

从设备 : 响应从主设备发来的总线命令

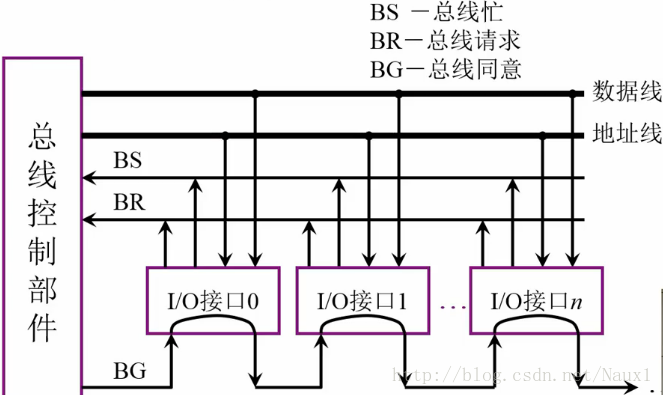

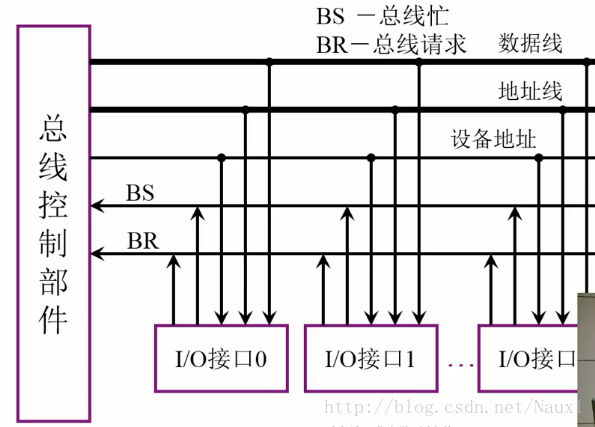

<1 链式查询方式

BG一个一个向下进行查询,如果挂接在总线上的这些I/O接口有总线占用请求,它会通过BR这条线向总线控制部件提出占用请求,总线控制部件接收到占用请求之后,可以让出总线的控制权,交给i/o设备使用,这时要进行查询,因为所有的I/O设备都用这一条线提出总线请求,不知道到底是哪个设备,谁的优先权更高,总线的控制权应该交给哪个设备。BG这条线逐个向下进行查询,首先查的是I/O接口0,看它是否发出总线占用请求,如果是它,总线使用权就交给I/O接口0。假如是I/O接口1提出占用请求,总线使用权就交给I/O接口1,接口1通过BS告诉总线忙

各个接口的占用总线优先级是根据连接方式事先确定的,如果一个接口优先权比较靠后,它可能一直无法获得总线的使用权。

缺点: 对电路故障特别敏感

这种结构一般用于微型计算机或简单的嵌入式结构

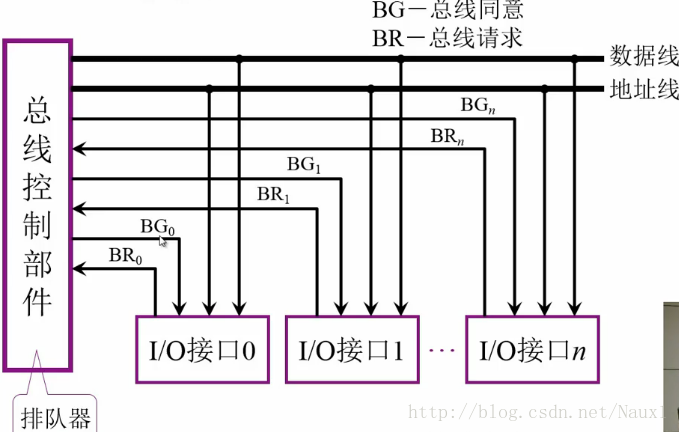

<2.计数器定时查询方式

设备地址:传输的地址是由一个计数器给出的,通过这个查找某一设备是否发出了占用请求。

总线控制部件里有一个计数器,它的初值可以是0也可以是其他一个值,如果某一个主设备想要占据总线,某一从设备要进行数据传输,它通过BR这条线向总线控制部件提出总线占用请求,总线控制器可以让占用的情况下,就启动计数器,计数器的值是通过设备地址向外进行输出的,设备地址这条线给出信号以后,比如此时计数器值为0,就对I/O接口为0的查看是否有占用请求,若没有计数器就会自动加1,查看i/o接口为1的是否有占用请求,若有,BS进行反应

<3.独立请求方式

2. 总线通讯控制

目的:解决通信双方协调配合问题

总线传输周期

- 申请分配阶段 主模块申请,总线仲裁决定(总线的判优)

- 寻址阶段 主模块向模块给出地址和命令

- 传数阶段 主模块和从模块交换数据

- 结束阶段 主模块撤销有关信息

总线通信的四种方式

1. 同步通信

2. 异步通信

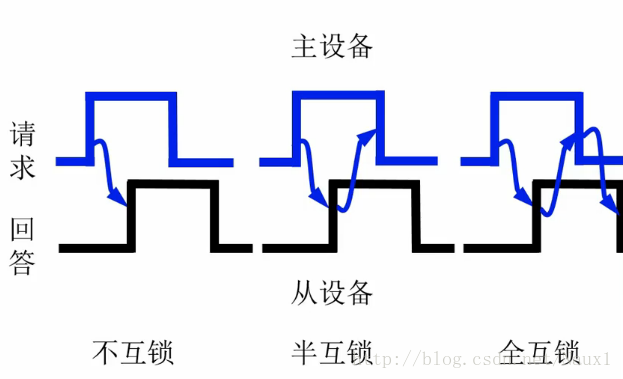

不互锁:

主设备发出通信请求,从设备接收到通信请求后进行应答。之后主设备撤销发出信号,从设备撤销应答信号。主设备不管从设备是否接收到应答信号,只要过一段时间后就会撤回。从设备也不管主设备是否接收到应答信号,过一段时间都会撤回应答信号

半互锁:

主设备发出通信请求,从设备接收到通信请求后发出应答信号。主设备接收到应答信号以后,再撤销请求。如果接收不到,这个请求会保持。而从设备不管主设备是否接收到应答信号,过一段时间都会撤回应答信号

全互锁:

主设备发出通信请求,从设备接收到通信请求后发出应答信号。主设备接收到应答信号以后,再撤销请求。同样只有主设备的信号撤销以后,从设备才会撤销自己的应答信号

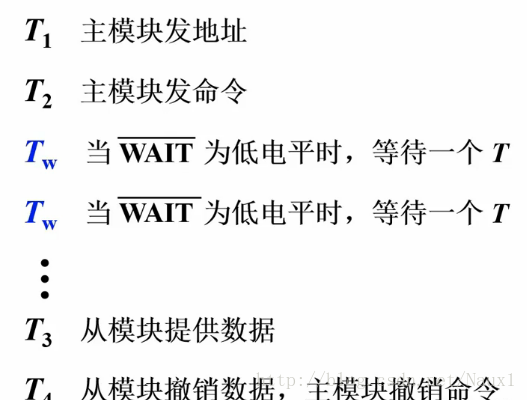

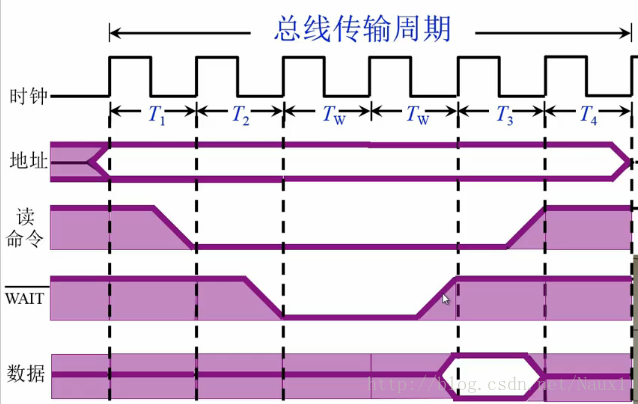

- 半同步通信(同步,异步结合)

同步 发送方用系统时钟前沿发信号

接收方有系统时钟后沿判断,识别

异步 允许不同速度的模块和谐工作

增加一条“等待”响应信号

以输入数据为例的半同步通信时序

上述三种通信共同点:

一个总线传输周期(以输入数据为例)

主模块发地址,命令 占用总线

从模块准备数据 不占用总线(总线空闲)

从模块向主模块发数据 占用总线

4. 分离式通信

第四种就是对上面三种进行改进,使总线不留空闲的时间

一个总线传输周期

子周期1 : 主模块申请占用总线,使用完后即放弃总线的使用权

子周期2 : 从模块申请占用总线,将各种信息送至总线上

分离式通信的特点:

1. 各模式有权申请占用总线

2. 采用同步方式通信,不等对方回答

3. 各个模块准备数据时,不占用总线

4. 总线被占用时,无空闲

252

252

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?