上节已经为OpenOCD增添了CH347的JTAG接口,

本文将用来展示,如何使用OpenOCD来操作CH347的JTAG接口对FPGA进行程序的下载,其可固化到FPGA的Flash中达到下载的效果。【2】CH347应用--在OpenOCD添加CH347-USB转JTAG接口_OIDCAT的博客-CSDN博客_openocd添加芯片![]() https://blog.csdn.net/OIDCAT/article/details/126876159?spm=1001.2014.3001.5501

https://blog.csdn.net/OIDCAT/article/details/126876159?spm=1001.2014.3001.5501

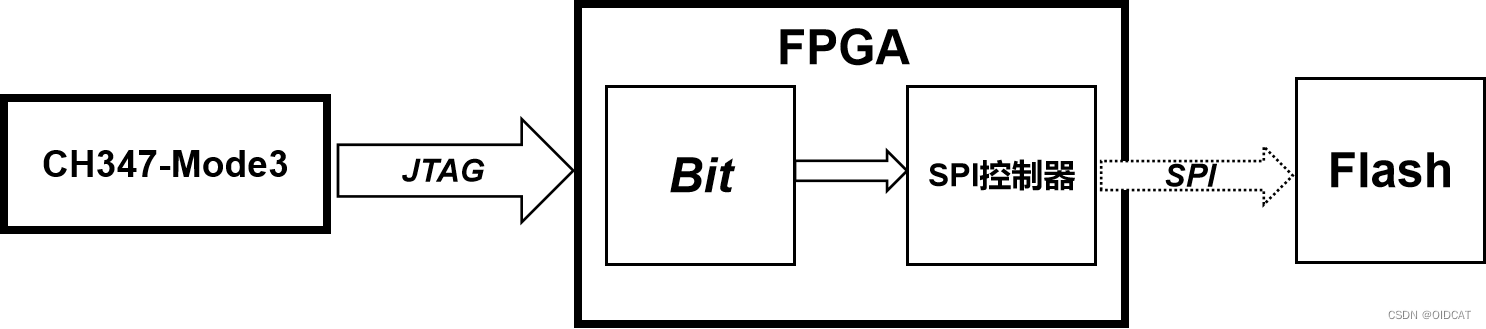

1、过程分析

在CH347的Mode3(UART+JTAG模式)下,通过JTAG先将Bit流程序文件下载入FPGA中,Bit文件将操作FPGA的SPI控制器,将JTAG数据转换为SPI数据写入Flash,此步骤即将BIN文件写入,从而实现其程序固化过程。

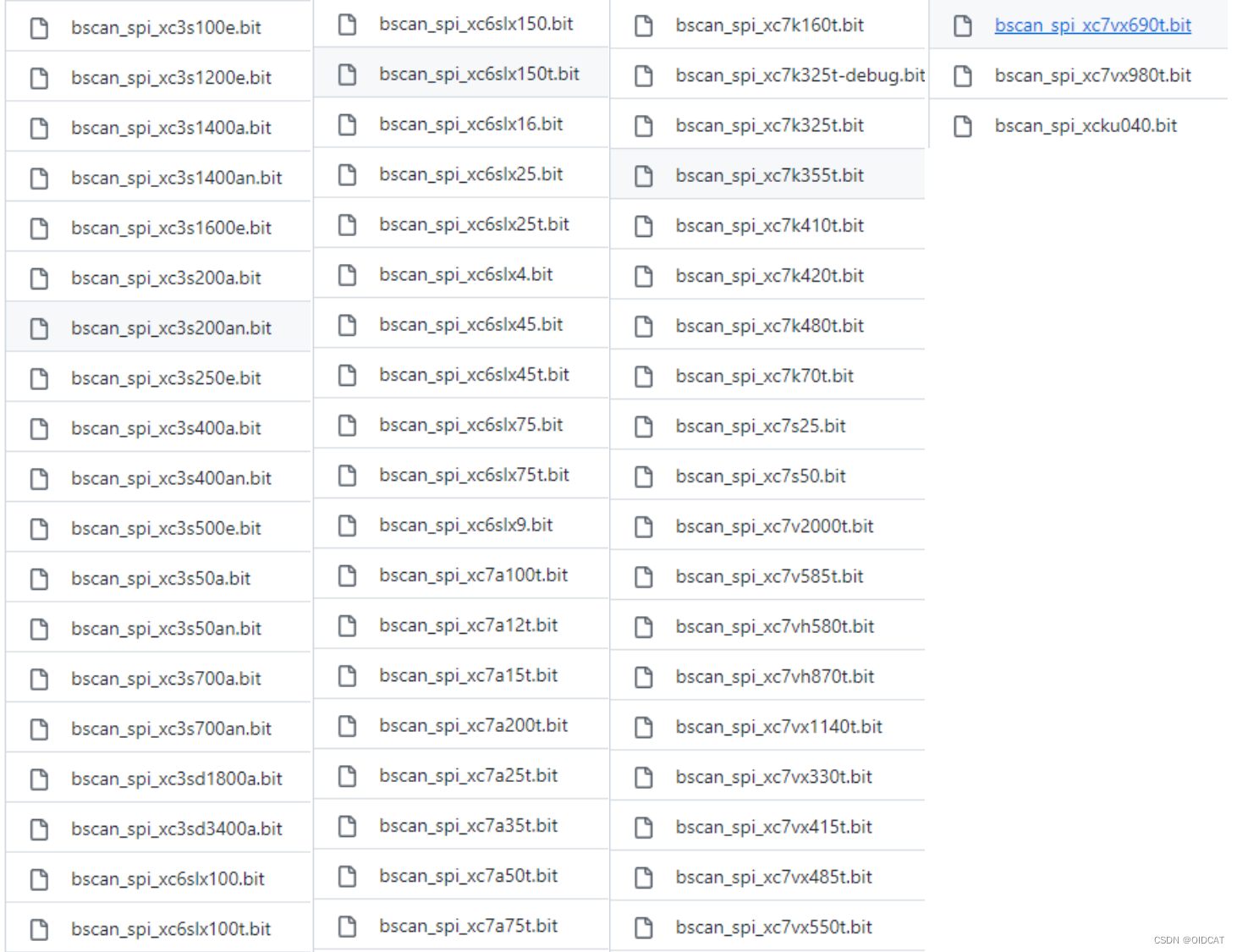

当前支持FPGA型号列表如下:

2、实现操作

此处选用FPGA为Xilinx的xc7a35t。编写CFG文件,使用"openocd -f"指定来调用。

将CFG文件命名为ch347-xilinx-flashDn.cfg

# 指定CH347-JTAG 调试器

adapter driver ch347

ch347 vid_pid 0x1a86 0x55dd

# 设置TCK时钟频率

adapter speed 10000

# 指定操作的TARGET,加载OpenOCD中JTAG-SPI驱动

source [find cpld/xilinx-xc7.cfg]

source [find cpld/jtagspi.cfg]

# 设置TARGET的IR命令

set XC7_JSHUTDOWN 0x0d

set XC7_JPROGRAM 0x0b

set XC7_JSTART 0x0c

set XC7_BYPASS 0x3f

# 下载流程

init

# 先下载Bit文件至TARGET

pld load 0 bscan_spi_xc7a35t.bit

reset halt

# 检测Flash信息

flash probe 0

# 下载Bin文件至Flash中

flash write_image erase test.bin 0x0 bin

# 生效固件操作

irscan xc7.tap $XC7_JSHUTDOWN

irscan xc7.tap $XC7_JPROGRAM

runtest 60000

runtest 2000

irscan xc7.tap $XC7_BYPASS

runtest 2000

exit3、执行结果

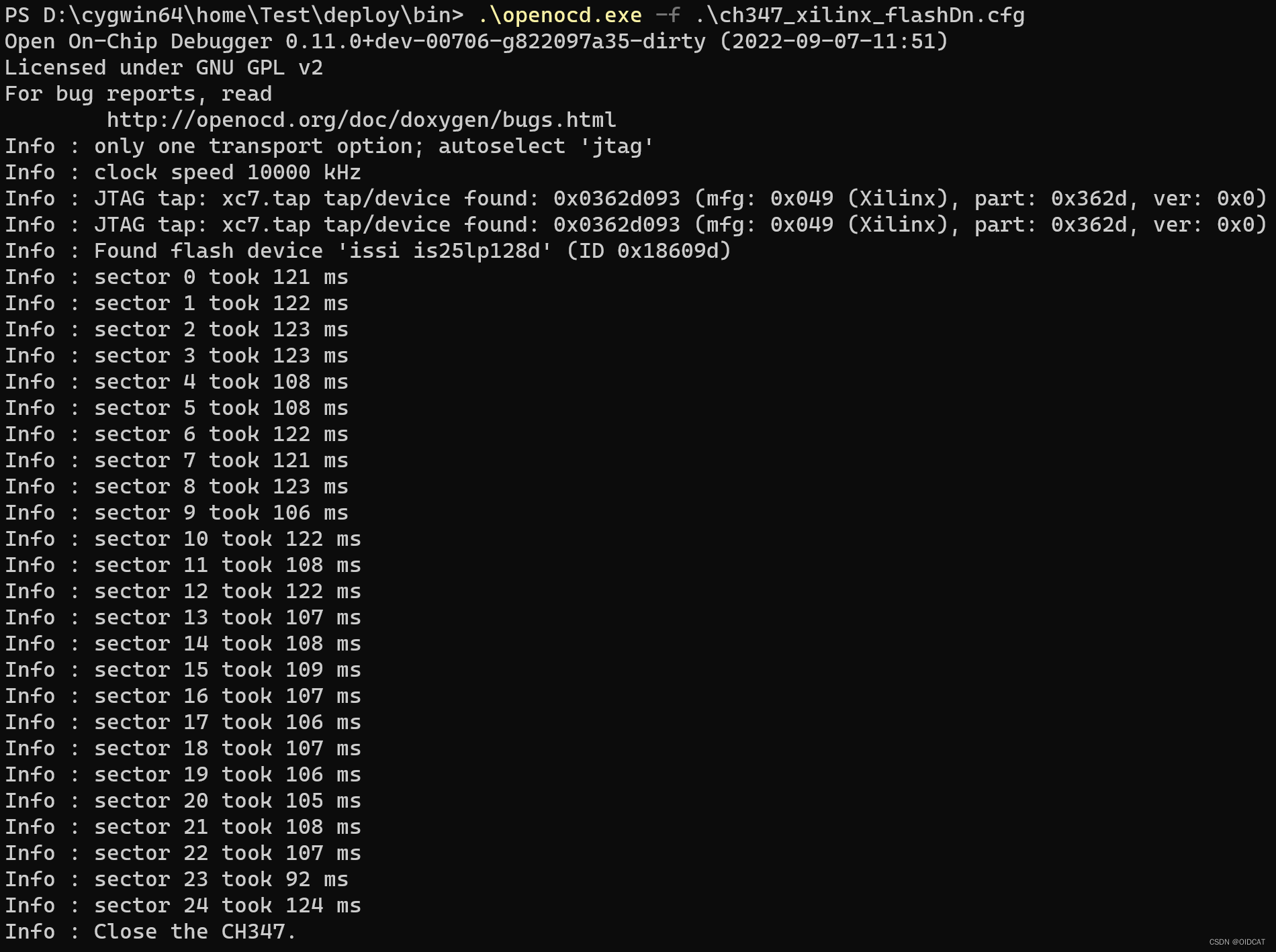

在Windows终端运行命令:[.\openocd.exe -f .\ch347_xilinx_flashDn.cfg],执行如下

此时下载结束,设备正常运行。

4825

4825

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?