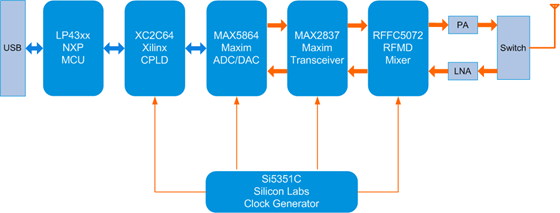

HackRF One硬件架构如图1所示。

图1 HackRF One硬件架构图[1]

- PC机通过USB接口与NXP LP43xx微控制器通信

- 微控制器通过并行总线及GPIO模拟的JTAG接口与CPLD连接

- MAX5864对【发送的数据】进行数模转换DAC,对【接收到的数据】进行模数转换ADC

- MAX2837完成上/下变频,并通过宽带混频器RFFC5072提高频率范围

- 射频前端采用一级LNA/PA进行放大,并最终通过TR Switch与天线连接

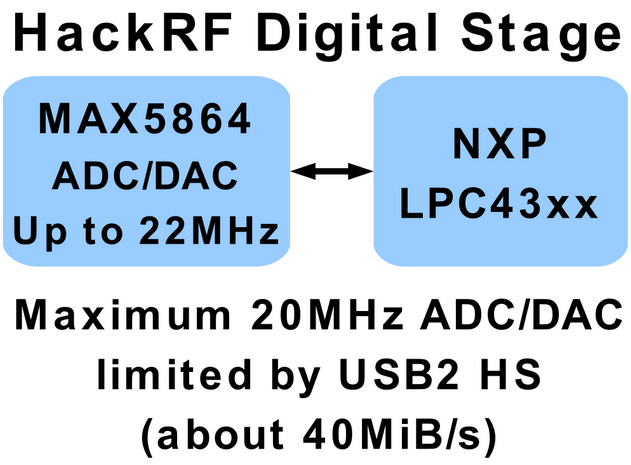

LPC4320/4330: ARM Cortex M4处理器, 主频204MHz

XC2C64A:Xilinx,CoolRunner-II系列CPLD,1500门

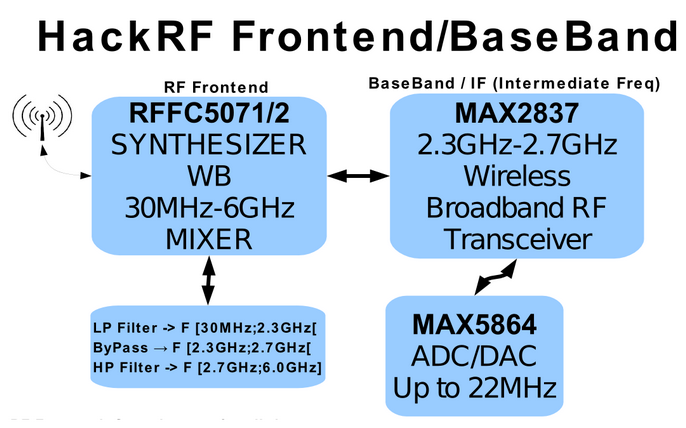

MAX2837:2.3GHz to 2.7GHz 无线宽带射频收发器

RFFC5072:混频器,提供80MHz到4200MHz的本振

MAX5864:ADC/DAC, 8-bit,22MHz采样率

Si5351C:I2C可编程任意CMOS时钟生成器

MGA-81563:0.1–6GHz 3V, 14 dBm 放大器

SKY13317:20 MHz-6.0 GHz 射频单刀三掷(SP3T)开关

SKY13350:0.01-6.0 GHz 射频单刀双掷(SPDT)开关

图2 HackRF Frontend/Baseband[2]

图3 HackRF Digital Stage[2]

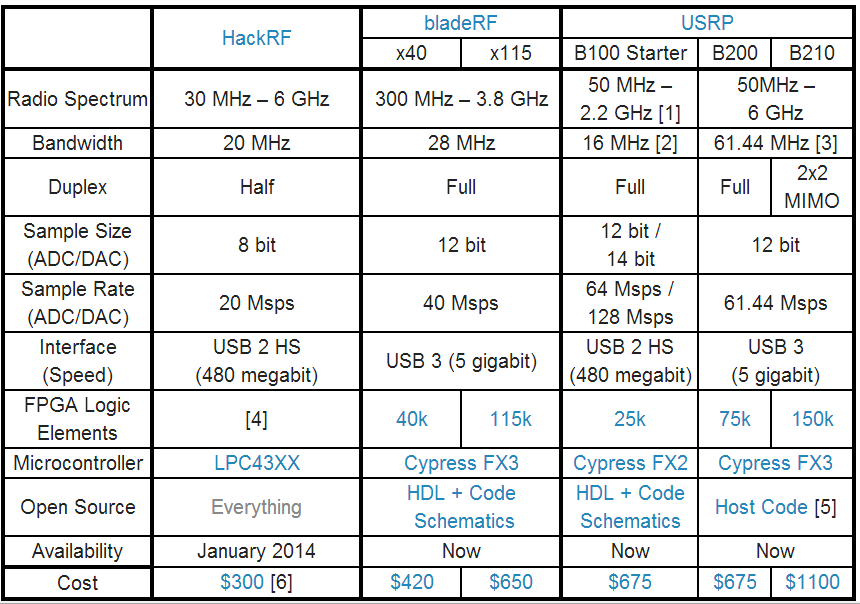

图4 HackRF One参数[3]

参考文献:

[1]http://bbs.eeworld.com.cn/thread-465790-1-1.html

[2]https://github.com/mossmann/hackrf/wiki/Hardware-Components

[3]http://www.taylorkillian.com/2013/08/sdr-showdown-hackrf-vs-bladerf-vs-usrp.html

397

397

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?