PCB Layout 注意事项——布线

目录

一、EMC优化

●调整过孔位置,使覆铜连成整块

●易受干扰的关键信号线作包地处理

●特殊封装——导线直连焊盘的“0欧电阻”

●关键信号或元件的背面铺地,不要走线,避免干扰

●蛇形线绕等长

●电源线按“主线——支线”走成分支形,避免环形

●电源先经过滤波电容,再进元件,先大电容后小电容

●延伸出去的铜皮要打地孔接地,避免悬空形成“天线”

补充:加地孔让元件接地良好

二、批量生产相关问题

●导线远离螺丝孔

附:PCB Layout 一般安全距离

●IC或贴片插座中,同一网络的相邻引脚,先引出导线再相连

三、其他布线规则

●进出线同宽

●对称出线

●走线方向统一

●焊盘出线位置优化

●兼顾多条规则,如EMC最佳、线路最短,布局整齐,方便检修等……

●布线次序、线宽

说明:本文所有文字及截图,均整理自本人日常工作总结,用于个人学习及同行交流,不足之处,欢迎交流指正!

--Perry

2019.12

一、EMC优化

●调整过孔位置,使覆铜连成整块

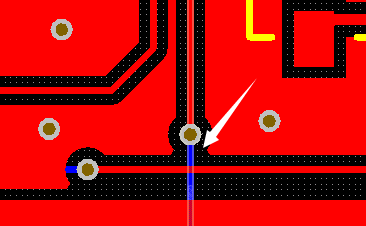

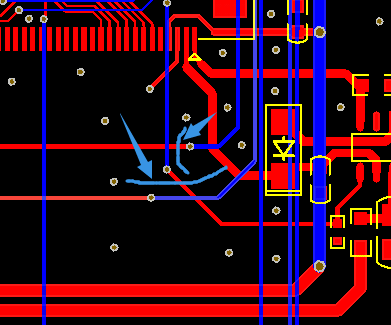

1、下左图,白色箭头处过孔太靠下,覆铜被分成左右两块。

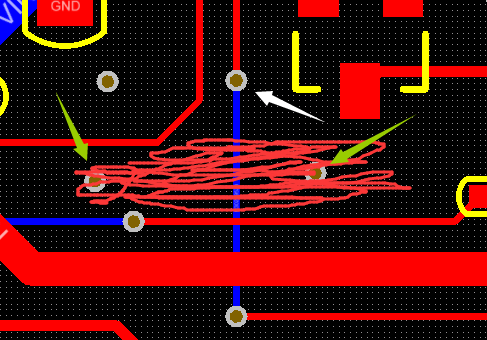

右图,过孔上移,下方可完整覆铜。绿箭头所指的两边区域能通过大块铜皮良好连接。

总结:布线阶段要提前考虑,避免零碎覆铜,影响EMC。甚至形成孤岛死铜,使元件接地脚接不到地。

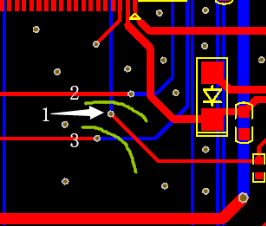

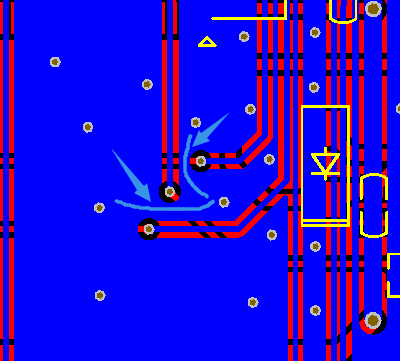

2、尽量避免割裂铜皮。下图,过孔1跟上下导线2和3保持足够距离,顶层覆铜时绿线标记处的铜皮就能连起来(右图示),不会断开。

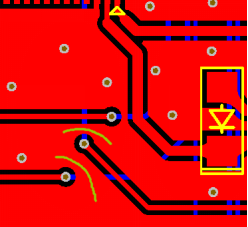

下图,底层同样留有空间,使蓝线标记处的底层铜皮相连。

总结:布线时要合理安排导线和过孔位置,构造出大块的地,提高板子的EMC性能。

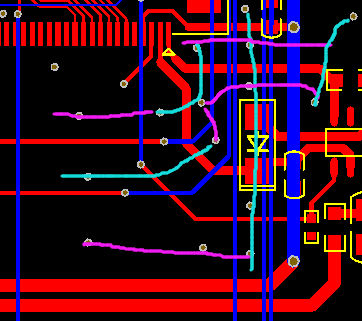

使顶层(粉色)跟底层(青色)的覆铜相连。

●易受干扰的关键信号线作包地处理

如时钟信号MCLK、PCLK。低压差分信号LVDSP、LVDSN。MIPI信号、M

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?