文章目录

前言

-

本笔记内容,为本人依据B站UP主“铁头山羊”视频内容(本人为其粉丝),归纳整理总结而来,如有侵权,联系立即删除,同时有想详细了解的也可进行观看bilibili铁头山羊 。

-

硬件:STM32F103C8T6

-

软件:Keil

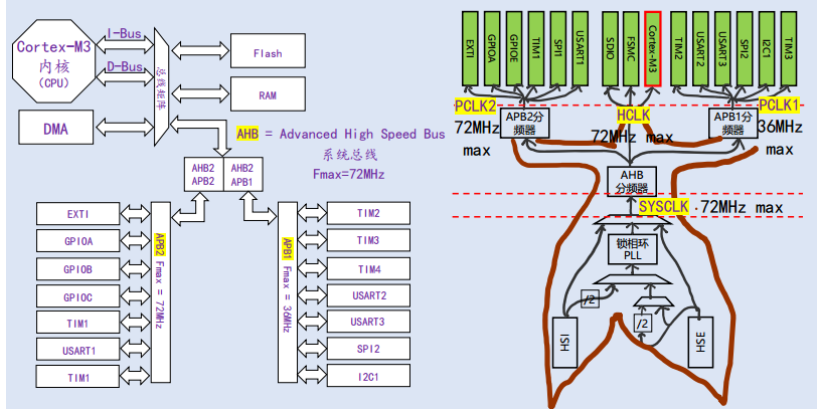

5-1 时钟树(下)

总线和树叶

外设的使能和禁止

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOC, ENABLE/DISABLE);

RCC_APB2PeriphClockCmd(RCC_APB2Periph_USART1, ENABLE/DISABLE);

RCC_APB1PeriphClockCmd(RCC_APB1Periph_USART2, ENABLE/DISABLE);

RCC_APB1PeriphClockCmd(RCC_APB1Periph_USART3, ENABLE/DISABLE);

RCC_APB1PeriphClockCmd(RCC_APB1Periph_UART4, ENABLE/DISABLE);

RCC_APB1PeriphClockCmd(RCC_APB1Periph_UART5, ENABLE/DISABLE);

外设复位

RCC_APB2PeriphResetCmd(RCC_APB2Periph_USART1, ENABLE); // 复位(按下复位按键)

RCC_APB2PeriphResetCmd(RCC_APB2Periph_USART1, DISABLE); // 释放(松开复位按键)

随堂测试

题目1:什么是分频和倍频,如何实现分频和倍频

答:

(1)分频:做除法 配置;

(2)倍频:做乘法 配置PLL锁相环。

题目2:时钟的4个最终来源分别是什么?

答:

(1)LSI;

(2)LSE;

(3)HIS;

(4)HSE。

题目3:简述SYSTICK的3种来源

答:

(1)HCLK;

(2)PCLK1;

(3)PCLK2。

题目4:HCLK\PCLK1\PCLK2是如何产生的

答:

HCLK:由系统时钟 SYSCLK 经 AHB 预分频器(HPRE)分频产生;

PCLK1:由 HCLK 经 APB1 预分频器(PPRE1)分频产生;

PCLK2:由 HCLK 经 APB2 预分频器(PPRE2)分频产生。

题目5:锁相环的倍频系数范围是多少?

答:2-16

题目6:内核的时钟来自哪里?

答:

(1)HSI(High-Speed Internal clock)

内部高速 RC 振荡器,频率固定为 8MHz。启动后默认使用 HSI,无需外部晶振,适合快速启动或低成本场景。

(2)HSE(High-Speed External clock)

外部高速晶振,通常连接 8MHz 晶振(典型值),需外接晶体谐振器(如 8MHz 晶振 + 22pF 负载电容)。HSE 精度高于 HSI,适合对时钟精度要求高的场景。

(3)PLL(Phase-Locked Loop)

锁相环倍频器,可将 HSI 或 HSE 倍频至更高频率(如 72MHz)。PLL 是最常用的 SYSCLK 来源,通过倍频实现高性能。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?