Reference:

V2静态时序分析与时序约束文档

入门

无时序约束场景中,普通图像显示不清晰,千兆网口接收Ethernet package 数据不正常,红外场景中图像显示不正常

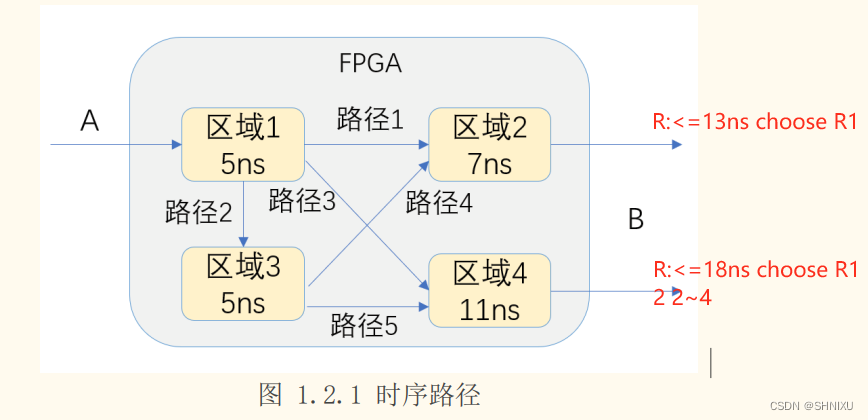

Definition: 我们提出一些特定的时序要求(或者说是添加特定的时

序约束),使用特定的时序模型,针对特定的电路进行分析。分析的最终结果是要求系统时序满足我们提出的要求。

R 是约束条件 有约束才会有分析

添加时时序约束之后,系统时序问题才会出现

添加时时序约束之后,系统时序问题才会出现

- 常见的高速接口

Quartus 使用 SDC约束

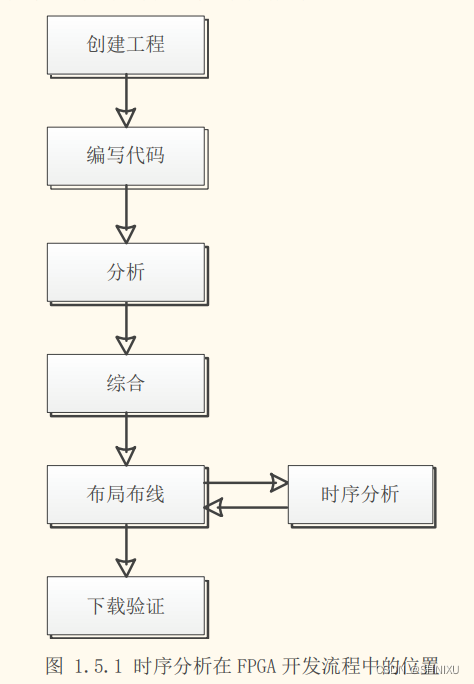

Static Timing Analysis 执行顺序:

Analysis — Synthesis:生成 netlist 做 map — sdc / xdc 指定时序,Compile Design: Fitter对结果进行 Place& Route(PR影响最终性能)— Verify Timing – Download

Clock Jitter:clock pluse width 发生暂时性变化 T cycle 或大或小

Clock Skew:同一个时钟域内的时钟信号达到数字电路各个部分所用时间的差异;define source: reg1, goal: reg2, clkToreg1 delay: Tc2s, reg1Toreg2:Tc2d, Tskew= Tc2d -Tc2s

Clock Uncertatinty = Skew + Jitter, 时序约束文件中经常出现,为了让时序分析更贴近真实电路设计

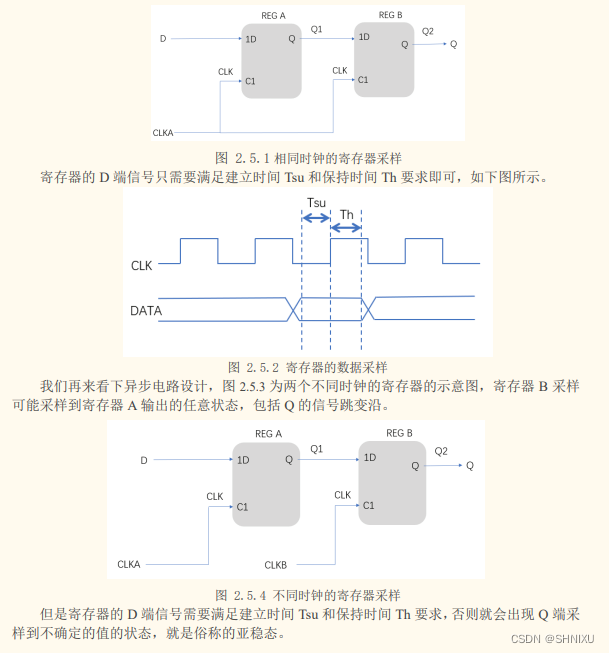

时序分析是在同步电路中使用(all regs in one PLL

& 异步电路 解释图

Setup Time: Tsu 时钟上升沿之前数据必须稳定的最短时间

Hold Time: Th 时钟上升沿之后数据必须稳定的最短时间

寄存器采样需要同时满足 Tsu & Th 才能采样成功

Launch edge: 发送数据的时钟边沿,通常选择上升沿

Capture edge: 采样到该数据的时钟边沿,通常也是上升沿

![![[Pasted image 20240613153948.png]]](https://img-blog.csdnimg.cn/direct/291a958a052e42e6adde11228483caf9.png)

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?