10 EMMC 总线

eMMC总线有11条通信线路:

. CMD:命令是一个双向信号。主机和设备驱动程序以两种模式运行,开排水和推拉。·

. DAT0-7:数据线是双向信号。主机和设备驱动程序在推拉模式下运行,·

. CLK:时钟是一个主机到设备的信号。CLK操作在推拉模式下的·

. 数据频闪器:数据频闪器是一个设备到信号的主机。数据频闪器以推拉模式运行。

主机通过开漏和推拉模式切换同步开启和关闭滚杆。主机不必有打开的排水驱动程序,但必须识别此模式才能打开ROD。RDAT和RCMD是上拉电阻器,当所有设备驱动器都处于高阻抗模式时,保护CMD和DAT线不受总线浮动设备的影响。

恒流源可以通过获得更好的性能(信号上升和下降边缘的恒定斜率)来代替ROD。如果主机不允许使用可切换的ROD实现,则可以使用一个固定的RCMD)。因此,如果所使用的RCMD值高于中给出的最小工作值,则必须降低开漏极模式下的最大工作频率。

RData Strobe 在HS400设备中使用下拉电阻

10.1 通电

eMMC总线的通电在设备和总线主线中本地处理。

. 通电后(包括热插入,即在总线运行时插入设备),设备进入预空闲状态。电源电压的通电时间应小于总线主电源电压下的规定tPRU。·

. 如果设备不支持启动模式,或者其BOOT_PARTITION_ENABLE位被清除,则设备将立即移动到空闲状态。在空闲状态时,设备会忽略所有总线事务,直到接收到CMD1。如果设备只支持标准的v4.2或更早版本,则它会在开机后立即进入空闲状态。

. 如果设置了Device BOOT_PARTITION_ENABLE位,则设备将移动到启动前状态。然后,设备将等待启动启动序列。在启动操作期之后,设备将进入空闲状态。在预引导状态期间,如果设备接收到除CMD1或引导启动序列以外的任何CMD行事务(将CMD行保持低至少74个时钟周期,或以0x FFFFFFF A的参数发出CMD0),设备移动到空闲状态。如果设备接收到启动启动序列(将CMD线保持在最低水平至少74个时钟周期,或以0x FFFFFFF A的参数发出CMD0),则设备将开始启动操作。如果启用了启动确认,则设备应在指定的时间内向主机发送确认模式“010”。启动操作终止后,设备进入空闲状态,并准备好进行CMD1操作。如果设备在预引导状态下接收到CMD1,那么它将开始响应该命令并移动到设备识别模式。

. 在空闲状态时,设备会忽略所有总线事务,直到接收到CMD1。

. eMMC在VCC和VCCQ线路上的最大初始负载(通电或热插入后)最大为10 uF,最小为330 Ω。在运行期间,VCCQ线路上的设备电容不得超过10 uF。

. CMD1是一种特殊的同步命令,用于协商操作电压范围,并轮询设备,直到其脱离其上电顺序。除了设备的工作电压配置文件外,对CMD1的响应还包含一个忙标志,这表明设备仍在进行其通电程序,并且还没有准备好进行识别。此位将通知主机设备尚未准备就绪。主机必须等到该位被清除之后再。

。 如果没有执行启动操作,该设备应在从第一个CMD1开始后的1秒内以有效的OCR范围完成其初始化

。 使设备脱离空闲状态应由总线主机负责。由于通电时间和电源上升时间取决于总线长度和电源单元等应用参数,主机必须确保在传输CMD1之前将电源建立到运行水平(在CMD1中指定的相同水平)。

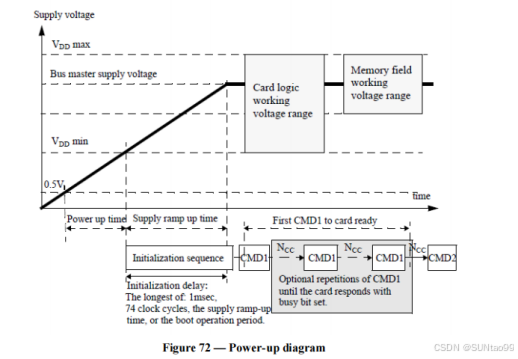

。 通电后,主机启动时钟,并在CMD线上发送初始化序列。序列长度是最长的:1毫秒、74个时钟、供应加速时间或引导操作周期。另外还提供了额外的10个时钟(超过了设备应该准备好进行通信之后的64个时钟),以消除通电同步问题。

。 每个总线主机都必须实现CMD1。CMD1的实现对所有的emmc都是强制性的。

10.1.1 e•MMC power-up

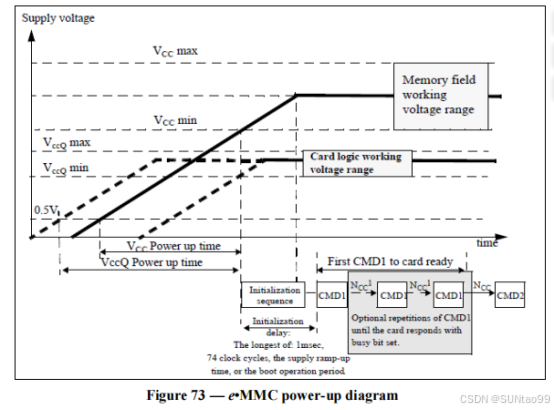

eMMC总线通电在每个设备和总线主中本地处理。图73显示了上电序列,后面是关于上电序列的具体说明

10.1.2eMMC通电指南

eMMC通电必须遵循以下准则:

. 当启动电源时,VCC或VCCQ可以首先升级,或者两者都可以同时升级。

. 通电后,eMMC进入预空闲状态。每个电源电压的通电时间应小于规定的tPRU(tPRUH、tPRUL或tPRUV)。

. 如果eMMC不支持启动模式或其BOOT_PARTITION_ENABLE位被清除,则eMMC将立即移动到空闲状态。在空闲状态时,eMMC忽略所有总线事务,直到接收到CMD1。如果eMMC只支持标准的v4.2或更早版本,则设备在通电后立即进入空闲状态。

. 如果设置了BOOT_PARTITION_ENABLE位,则MMC移动到启动前状态,并且MMC等待启动启动序列。在启动操作期之后,eMMC进入空闲状态。在预引导状态期间,如果eMMC接收到除引导启动序列(保持CMD行低至少74个时钟周期,或发出CMD0与参数0x FFFFFFF A)和CMD1之外的任何CMD行事务,则eMMC移动到空闲状态。如果eMMC接收到引导启动序列(保持CMD线处于较低位置至少74个时钟周期,或以0x FFFFFFF A的参数发出CMD0),则eMMC开始启动操作。如果启用了启动确认,则eMMC应在指定的时间内向主机发送确认模式“010”。在启动操作终止后,eMMC进入空闲状态,并应准备好进行CMD1操作。如果eMMC在启动前的状态下接收到CMD1,那么它将开始响应该命令并移动到设备识别模式。

. 在空闲状态时,eMMC忽略所有总线事务,直到接收到CMD1。

. CMD1是一种特殊的同步命令,用于协商操作电压范围和轮询设备,直到它超出其通电序列。除了该设备的工作电压分布外,对CMD1的响应还包含一个繁忙标志,表明该设备仍在进行其通电过程,且尚未准备好进行识别。此位通知主机设备尚未准备好,主机必须等待此位被清除。设备必须在具有有效OCR范围的第一个CMD1的1秒内完成其初始化。

. 如果eMMC设备在上一个通电会话期间成功分区(EXT_CSD字节[155] PARTITION_SETTING_COMPLETED成功设置的第0位),那么初始化延迟将从INI_TIMEOUT_PA(EXT_CSD字节[241])计算出来(而不是1秒)。此超时仅适用于分区成功后的第一次初始化。对于所有连续的初始化,将应用1秒的超时。

. 总线主服务器会将该设备移出空闲状态。因为通电时间和电源上升时间取决于母线长度和电源单元等应用参数,主机必须确保在传输CMD1之前电源达到运行水平(CMD1中指定的相同水平)。

. 上电后,主机启动时钟,并在CMD线上发送初始化序列。序列长度为最长的:1 ms、74个时钟、电源上升时间或引导操作周期。另外还提供了10个时钟(超过通电序列的64个时钟),以消除通电同步问题。

. 每个总线主机都必须实现CMD1。

. 以上所有规则也适用于e2MMC(VCC和VCCQ)。此外,e2MMCD-VDD必须在D-VDDQ之前上升。对于提高VCC/VCCQ和D-VDD/D-VDDQ的顺序没有限制。

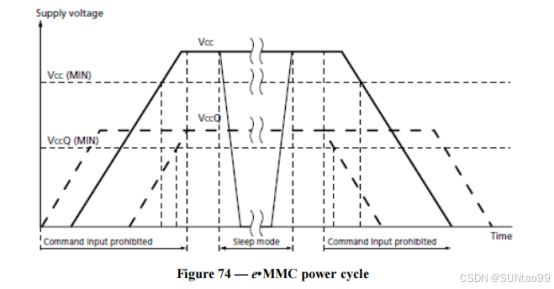

10.1.3 e•MMC power cycling 电源循环

主服务器可以执行任何序列的VCC和VCCQ通电/下电。但是,在VCC和VCCQ在每个工作电压范围内稳定之前,主控不能发出任何命令。从机进入睡眠模式后,主服务器可以断电VCC,降低功耗。在主机发出CMD5(SLEEP_AWAKE)以唤醒从单元之前,必须将从单元提升到VCC。

如果VCC或VCCQ低于0.5 V超过1 ms,从服务器应始终返回到预空闲状态,并执行适当的引导行为。一旦电压恢复到其功能范围,从机将表现为标准的通电状态。

这种行为的一个异常状态是,如果设备处于睡眠状态,其中不监测VCC上的电压。

除上述规则外,对于e2MMC,应在D-VDD之前降低D-VDDQ,同时D-VDDQ / D-VDD均应在工作电压范围内处于稳定状态,然后才能发出任何命令。D-VDDQ和D-VDD都可能在设备处于睡眠状态时断电。同样,在主机发出CMD5以唤醒从设备之前,D-VDDQ和D-VDD都应通电。

10.2 可编程设备输出驱动程序

eMMC总线的每条线路的总线电容是总线主电容、总线电容本身和每个插入装置的电容之和。主机和总线电容的总和是固定的,但在不同的应用中可能会有所不同。设备负载可以在一个应用程序中随每个插入的设备而变化。

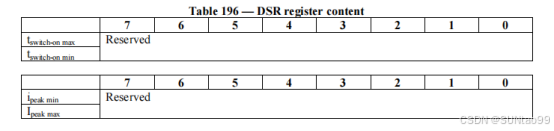

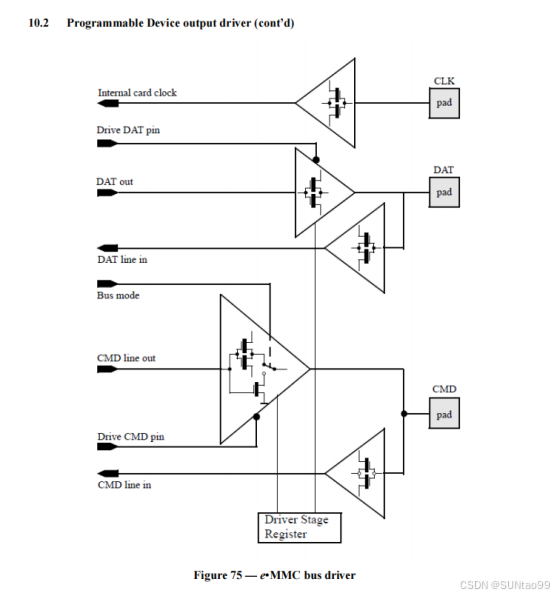

CMD和DAT总线驱动器由一个预驱动器级和一个互补的驱动器晶体管组成(图75)。DSR寄存器用于配置预驱动级输出的上升和下降时间,以及互补驱动级晶体管的尺寸。两者的适当组合可以实现最佳的总线性能。表196定义了DSR寄存器的内容:

所有数据对指定的工作范围(电压、温度)都有效。DSR寄存器具有两个字节码(例如,位0-7 = 0x02,位8-15 = 0x01),这些字节码分别定义了寄存器的切换速度和当前驱动器的特定最小值和最大值(实际值为TBD)。开关速度和驱动力的任何组合。所选择的速度设置必须与系统的频率相一致。必须保持以下关系:t

switch-on-max ±0.4 * (FOD)-1

10.3 总线运行条件

10.3.1 emmc电源供电

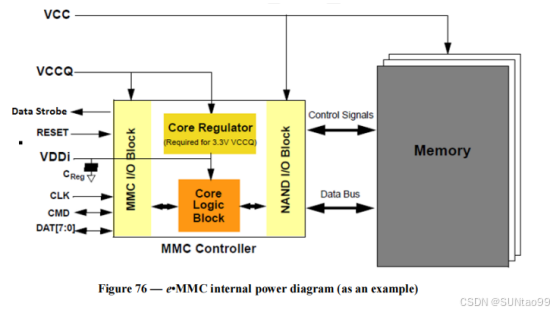

在eMMC中,VCC用于存储设备;VCCQ用于控制器和MMC接口电压。VCC或VCCQ为内存接口电压。铁芯调节器是可选的,仅在内部铁芯逻辑电压由VCCQ调节时才需要。一个Creg电容器必须连接到VDDi端子,以稳定系统上的调节器输出。

10.3.2 e2mmc电源供电

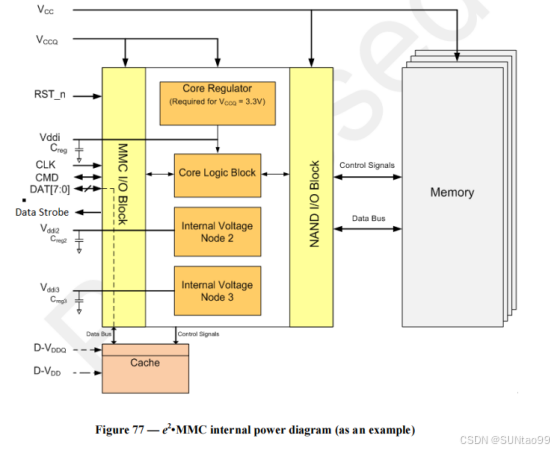

在eMMC中,VCC用于内存设备;VCCQ用于控制器和MMC。VCC或VCCQ均可用于图77中所示的内存接口电压。铁芯调节器是可选的,仅在内部铁芯逻辑电压由VCCQ调节时才需要。一个Creg电容器必须连接到VDDi端子,以稳定系统上的调节器输出。

D-VDDQ和D-VDD用于高速缓存内存。D-VDD用于缓存内存的核心,D-VDDQ用于内存控制器和缓存存储器之间的IO。

- VDDi2和VDDi3是其他内部电压端子。每一个都是由一个外部电源通过调节器产生的,以减少功耗或避免内部的噪声干扰。Creg2和Creg3电容器必须分别连接到VDDi2和VDDi3。这些都是e2MMC设备的可选设备。

10.3.3电源供电电源

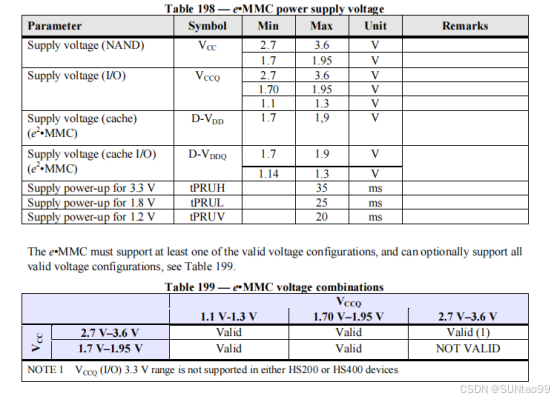

eMMC支持一个或多个VCC和VCCQ的组合,以及D-VDDQ和D-VDD的任意一个组合,如表197所示。VCCQ必须被定义为等于或小于VCC。可用的电压配置见表198

10.3.4 总线信号线负载

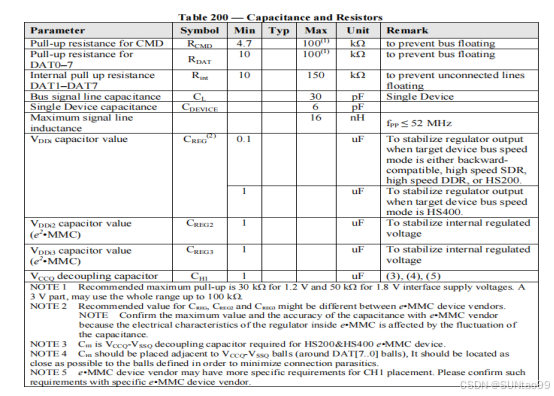

eMMC总线的每条线路的总电容CL是总线总电容CHOST、总线电容CBUS本身和连接到该线路的设备的电容器件的和,

CL = CHOST + CBUS + CDEVICE

并要求主机和总线电容之和不超过20 pF,见表200错误!找不到引用源。错误!

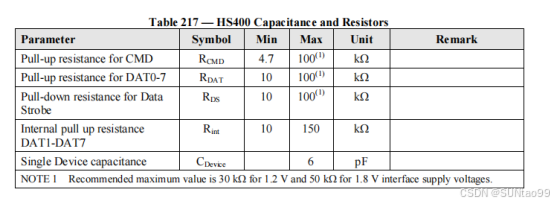

10.3.5 HS400参考负载

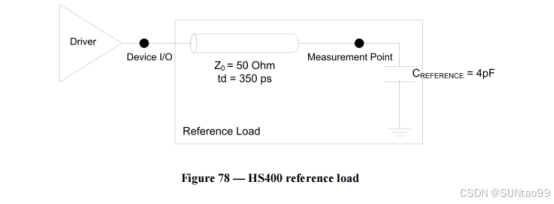

图78中的电路显示了用于定义HS400设备输出时间和超调/欠调参数的参考负载。

参考负载由输电线和干扰电容组成。

参考负载并不是对典型系统环境的精确表示,也不是对生产测试人员提供的实际负载的描述。

系统设计人员应该使用IBIS或其他模拟工具来将参考负载与系统环境关联起来。制造商应与他们的生产测试条件相关联。

引入了传输线路的延迟时间(td),使参考负载与PCB技术和跟踪长度无关。

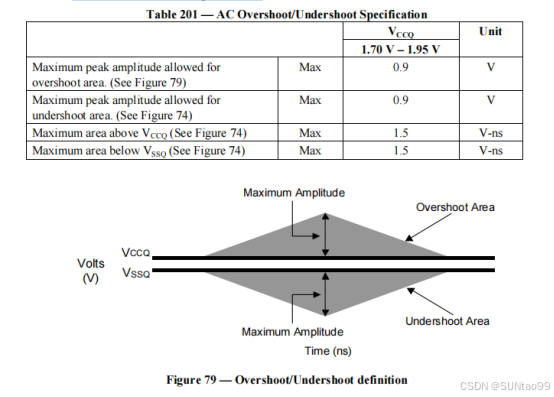

10.4 超调技术规范

10.5 总线信号电平

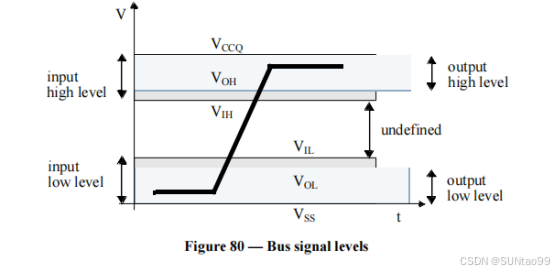

由于母线可以提供一个可变的电源电压,因此所有的信号电平都与电源电压有关。

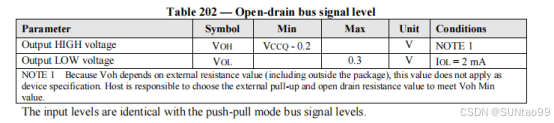

10.5.1 开漏极模式总线信号电平

10.5.2 推拉模式总线信号电平-eMMC

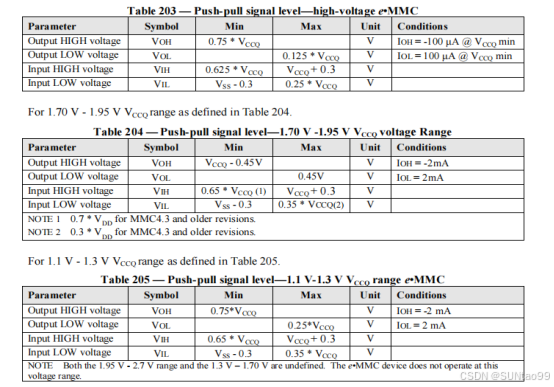

设备的输入电压和输出电压应在以下规定的任何VCCQ的允许电压范围内对于2.7 V - 3.6 V VCCQ范围(与JESD8C.01兼容)

10.5.3 HS200和HS400的总线运行条件

HS200和HS400设备的总线运行条件与10.5.1至10.5.2中规定的相同。唯一的例外是不支持VCCQ = 3.3 V。

10.5.4 HS200和HS400的设备输出驱动程序要求

10.5.4.1驱动程序类型定义

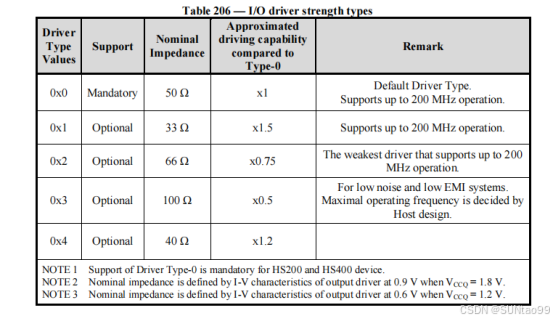

驱动程序类型-0被定义为eMMCHS200和HS400设备的强制性类型,而另外四种驱动程序类型(1、2、3和4)被定义为可选类型,以允许支持更广泛的主机负载。主机可以选择最合适的设备驱动程序类型(如果支持),以实现最佳的信号完整性性能。

注意:1.8 V和1.2 V信号电平的驱动器强度定义相同.

驱动0型是针对传输线路,基于50 Ω标称线路阻抗的分布式系统。因此,它被定义为50 Ω的标称驱动器。

对于HS200,当使用CL = 15pF驱动器进行测试时,类型-0应满足所有交流特性(见10.5.4.2)和HS200设备输出定时要求(见10.8.3)。在10.5.4.3中定义的测试电路用于驱动器类型-0的测试。

对于HS400,在10.3.5中定义的参考负载进行测试时,驱动0型或驱动1型或4型应满足所有交流特性(见10.5.4.2)和HS400设备输出定时要求(见10.10.2)。

可选的驱动程序类型将参照驱动程序类型-0进行定义。

表206总结了五种驱动器类型的标称阻抗特性。

如果设备支持可选的驱动程序类型,主机可以使用它们来优化其系统中的信号完整性。为此,主机设计器可以使用设备驱动程序模型来模拟其特定的系统。主机可以选择最佳的驱动程序类型,可以驱动主机系统负载在所需的工作频率与最小的噪声产生。

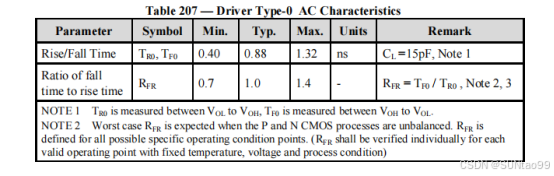

10.5.4.2驱动type-0型交流特性

表207是HS200和HS400设备的强制性要求。

HS200设备的交流要求见10.8。

对HS400设备的交流要求定义在10.10中。

驱动程序类型1、2、3和4的I-V曲线(电流-电压特性)大约为默认驱动程序类型-0中的x1.5、x0.75和x0.5。

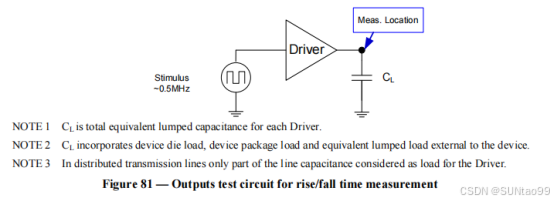

10.5.4.3驱动器type-0型测试电路

图81所示的测试电路用于验证10.5.4.2中定义的驱动器特性。测量特性应在所有角落条件下(工艺和环境)符合规范。

10.5.4.4驱动程序类型选择

该设备支持的驱动程序类型的级别在扩展CSD寄存器的DRIVER_STRENGTH [197]字段中显示。主机通过将(通过CMD6)写入扩展CSD寄存器的HS_TIMING[185]字节中的“选定的驱动程序强度”字段来设置所需的级别。

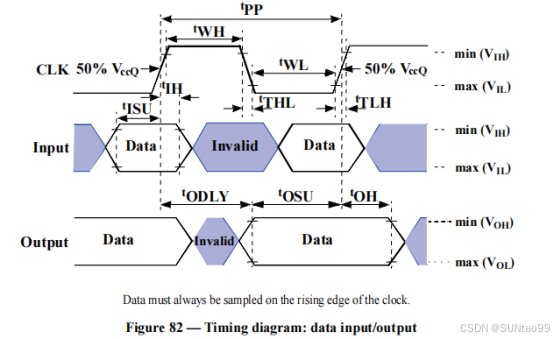

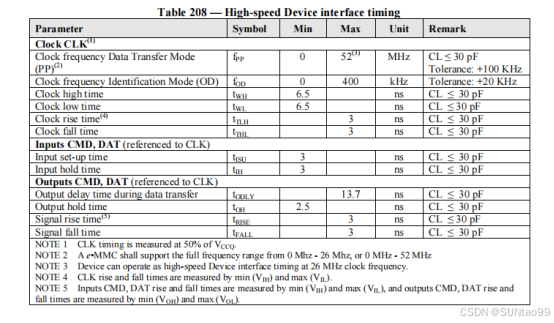

10.6总线定时

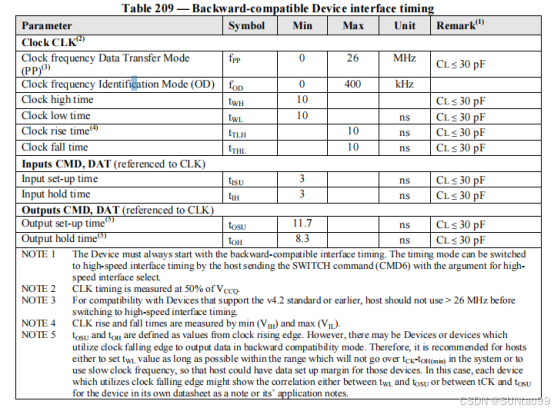

10.6.1设备接口计时

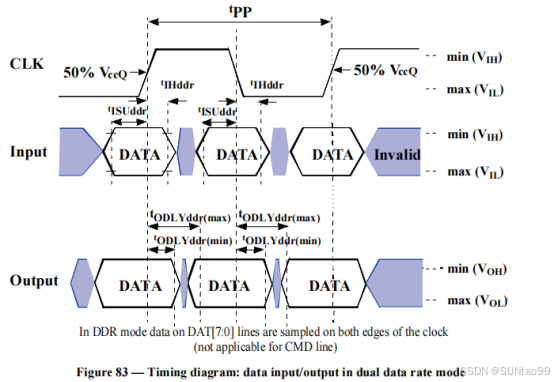

10.7 在2倍数据速率操作期间,DAT信号的总线时序

只有当设备被配置为双数据模式操作时,这些计时才适用于DAT[7:0]信号。在这种双数据模式下,DAT信号与CLK的上升边缘和下降边缘同步运行。CMD信号仍然与CLK的上升边缘同步运行,因此符合10.6中规定的总线定时,因此CMD信号没有定时变化。

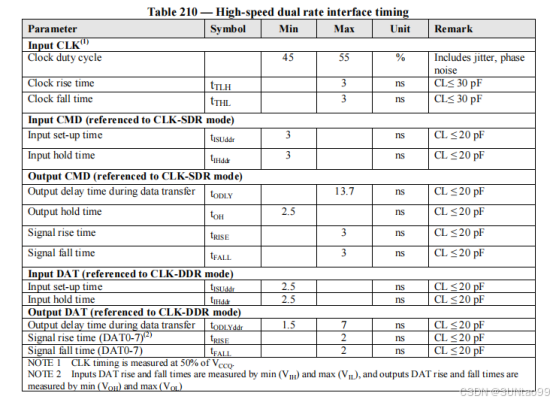

10.7.1双数据速率接口计时

10.8 HS200模式下的总线时序规范

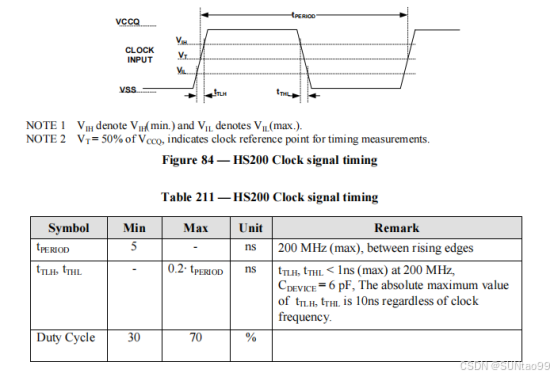

10.8.1 HS200时钟计时

HS200模式下的主机CLK时序应符合图84和表211中规定的时间。CLK输入应满足所有可能的操作和环境条件下的时钟时序。当CMD和DAT线高低稳定时,应尽可能靠近设备,测量CLK输入参数。HS200的最大频率为200 MHz。主机可以使用HS200模式允许的最大频率。

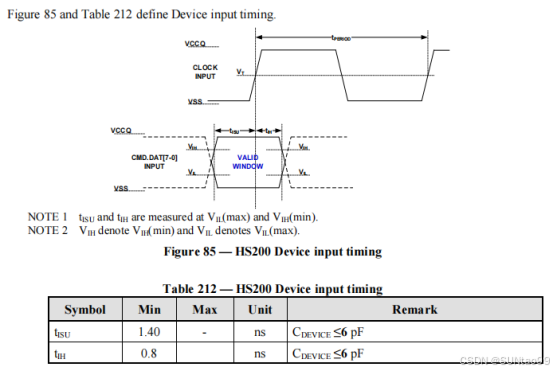

10.8.2 HS200设备输入定时

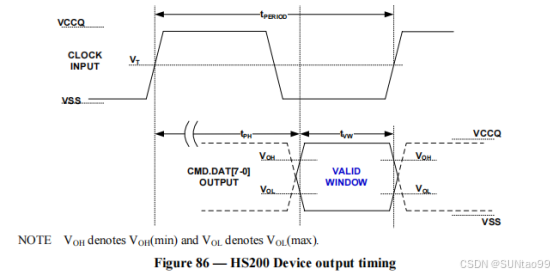

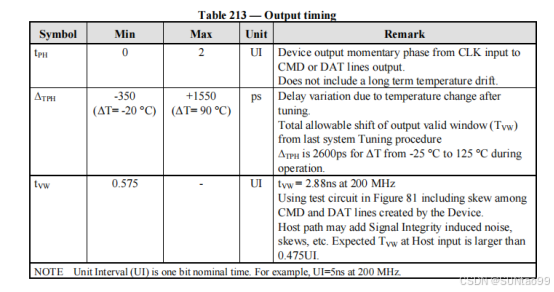

10.8.3 HS200设备输出时序

定义了tPH参数,允许设备输出延迟大于tPERIOD。在初始化后,tPH可能与时钟有随机的相位关系。主机负责在切换到HS200模式时,找到设备输出的最佳采样点。

图86和表213定义了设备的输出时间。

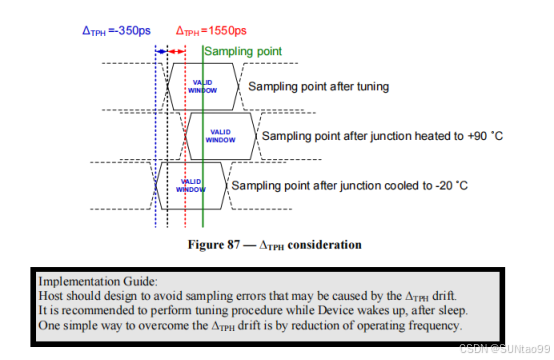

在设置数据的采样点时,应考虑一个主要依赖于温度漂移的长期漂移。温度漂移用∆TPH表示。无论漂移窗口(∆TPH)如何,输出有效数据窗口(tVW)都是可用的,但是数据窗口的位置随漂移而变化,如图87所示。

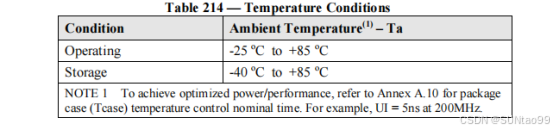

10.9 温度条件

10.10 HS400模式下的总线定时规范

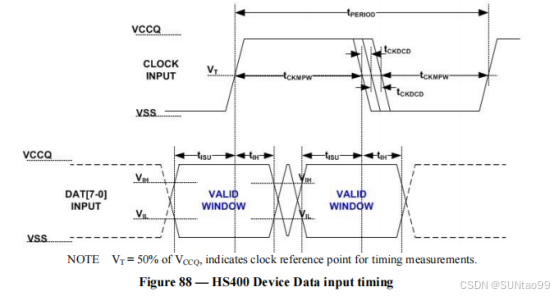

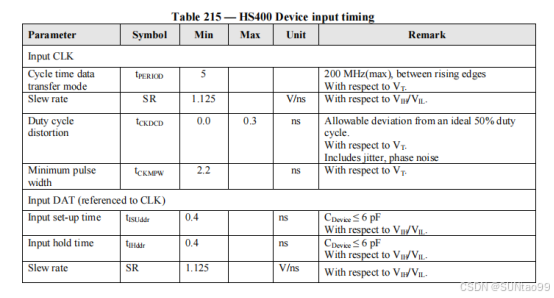

10.10.1 HS400设备输入定时

HS400模式的CMD输入定时与HS200模式的CMD输入定时相同。图88和表215显示了设备输入定时。

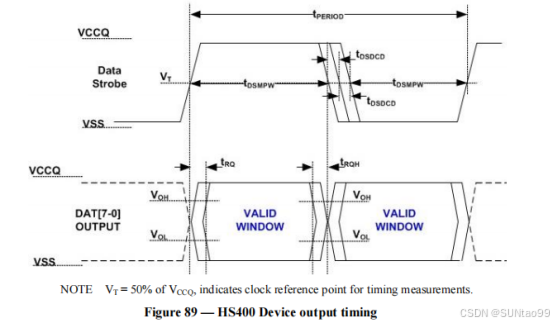

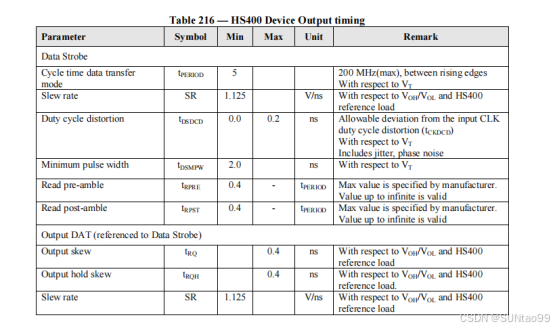

10.10.2 HS400设备输出时序

数据频闪器用于在HS400模式下读取数据。数据闪只在数据读取或CRC状态响应时切换。

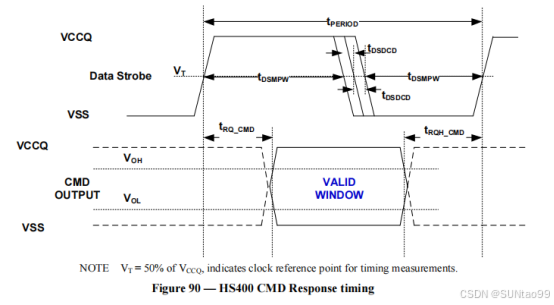

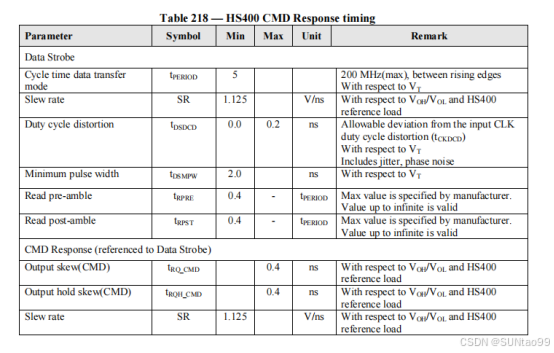

10.10.3 HS400设备命令输出时序

数据频闪器用于响应HS400模式下的任何命令。

11 emmc 标准符合性

eMMC标准提供了媒体可交换性和兼容性所需的所有必要信息。

. 通用设备访问和通信协议(第6条,第7条)·

. 数据完整性和错误处理(第8条)·

. 机械接口参数、设备外形系数(第9条)·

. 电气接口参数,如:电源、峰值和平均电流消耗以及数据传输频率(第10条)

然而,由于有针对性的eMMC应用的广泛范围,从全面的基于PC的应用到非常低的细分市场,在特定的eMMC系统中实现每一个eMMC标准特性并不总是成本效益,也不是有用的。

因此,许多参数都是可配置的,并且可以根据每个实现进行定制。只要设备的所有配置参数都在有效范围内,该设备就符合标准。只要一个eMMC主机支持至少一个如下面定义的eMMC类,它就是兼容的。每个MMC系统组件的供应商都必须明确规定(在其产品手册中)该设备的所有MMC特定限制。

eMMC(从属)在设备特定数据(CSD)寄存器中提供其配置数据(参见7.3)。eMMC协议包括查询此信息和验证系统概念配置的所有必要命令。e需要MMC主机(主主机)(作为系统启动过程的一部分)来验证主机到设备与连接到总线的每个设备的兼容性。

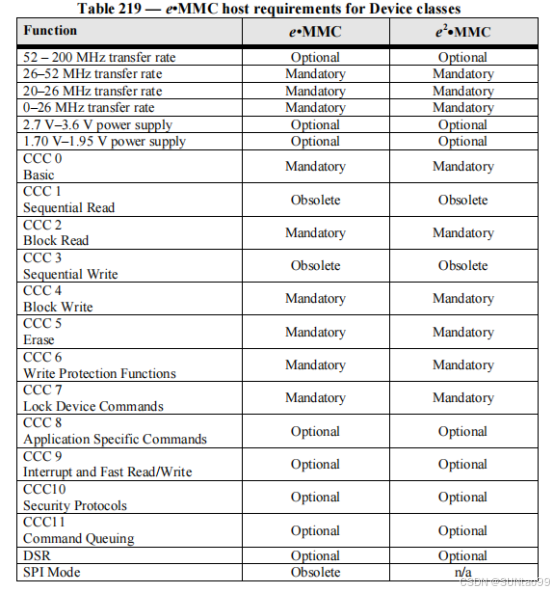

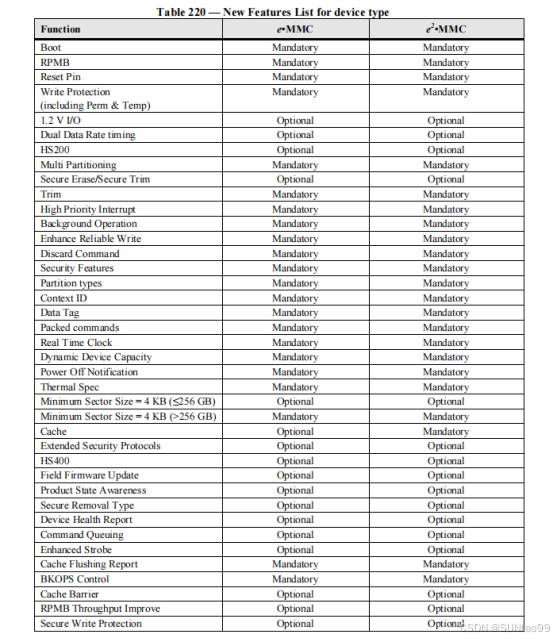

表219总结了来自eMMC主机对每个设备类(CCC = Device命令类,见6.10)的要求。该条目的含义如下:

. 强制要求:任何支持指定设备类的eMMC主机都必须实现此功能。·

. 可选:此功能是一个附加的选项。主机符合指定的设备类,但没有实现此功能。

. 不必需:此函数对指定的设备类没有用处。

对可选功能的说明:

. 中断命令旨在减少在某些事件的轮询期间所需的主机端开销。·

. DSR的设置允许主机以一种非常灵活的、依赖于应用程序的方式配置eMMC总线·

. 主机中的外部ECC允许使用极低成本的设备。·

. 根据支持的类定义了设备状态相关位。·

. 消毒和坏块管理是使该设备能够在安全应用程序中使用的特性。·

. 修剪和丢弃命令允许主机协助优化内部设备垃圾收集操作

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?