基本概念

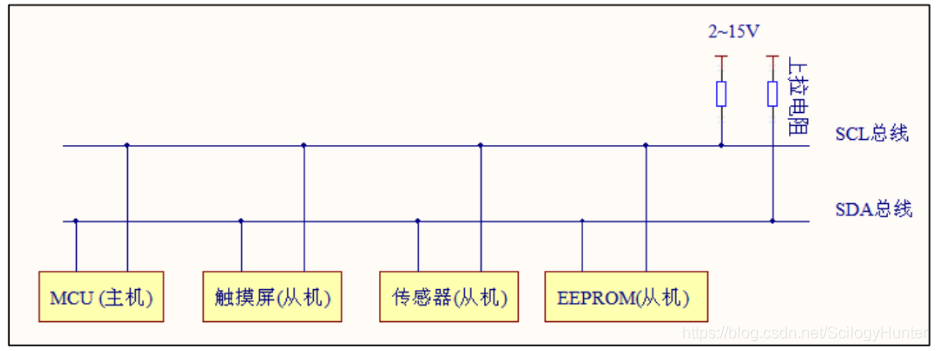

I2C 的英文拼写是“Inter—Integrate Circuit”,即内置集成电路。I2C 是一种由 Philips 公司开发的两线式串行总线,用于连接微控制器及其外围设备。

I2C 总线简单而实用,占用的 PCB(印刷电路板)空间很小,芯片引脚数量少,设计成本低。I2C 总线支持多主控(Multi-Mastering)模式,任何能够进行发送和接收的设备都可以成为主设备。主控能够控制数据的传输和时钟频率,在任意时刻只能有一个主控。

主要特点

- 串行传输,数据是一位一位传输的。

- 同步方式,具有时钟线,依照时钟线节拍同步收发数据。

- 半双工,不能同时收发,为半双工通信。

- 主从模式,只有主机才能主动发起读写过程,从机只能被动响应。

- 多主多从。从机都有唯一地址,地址为7位或10位,通信中只有地址匹配的从机才响应。多主机间可通过仲裁解决冲突。

- 逐字响应,每发送完一个字节对方都会有一个响应位(ACK,NACK),以便发送方进行相应处理。

- 电路简洁,只需要两根线,且使用TTL电平进行通信,所以硬件成本低,实现容易。

- 短距低速,因为是串行TTL电平通信,所以波特率不能很高,带宽较窄,通信距离也不能很远,一般都是用于CPU和板级外设间通信。

信号线

I2C 总线只有两根线分别为:时钟线和数据线 。

- SCL(Serial Clock)时钟线:时钟线是单向的,只能由主机发出由从机接收,用于提供通信时的统一时钟信号,保证主从机能同步处理。官方推出两种通信速率,标准模式 100kbit/s ,快速模式为 400kbit/s,因为是同步方式其他自定义通信速率下也是能正常通信的,速率越高距离越短。

- SDA(Serial Data)数据线:数据线是双向的,依据收发状态主从都可以接收或发送数据。

I2C 总线的SDA 和SCL在输出时都是开漏输出的,都需要接上拉电阻,即都可以是线与模式。主机间仲裁和异常通知都需要线与模式来实现,同时避免了同时输出时线路短路以及方便了不同电平信号间匹配。

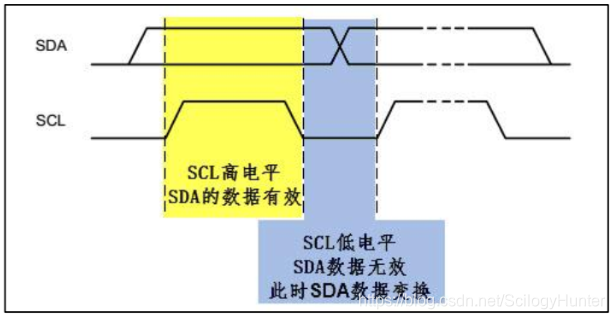

位信号

空闲时,主从都是输入模式,为高阻态,通过上拉电阻上拉,SDA 和SCL都为高电平。

通信时,主机输出时钟信号,SDA 和SCL的不同电平组合实现不同的总线信号。

- SCL为低电平时, SDA的数据无效,一般在这个时候 SDA 进行电平切换,为下一次表示数据做好准备

- SCL为高电平时, SDA表示的数据有效,SDA 和SCL的不同电平组合实现不同的总线信号。

- SDA为高电平时,表示数据“1”。

- SDA为低电平时,表示数据“0”。

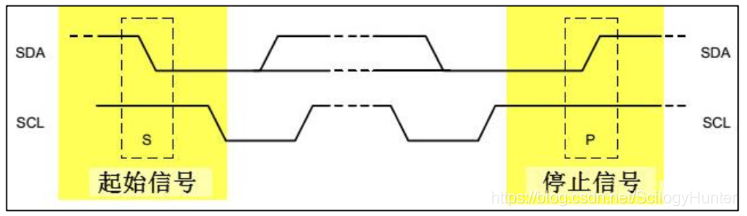

- SDA为下降沿时,表示起始信号(start)。

- SDA为上升沿时,表示结束信号(stop)。

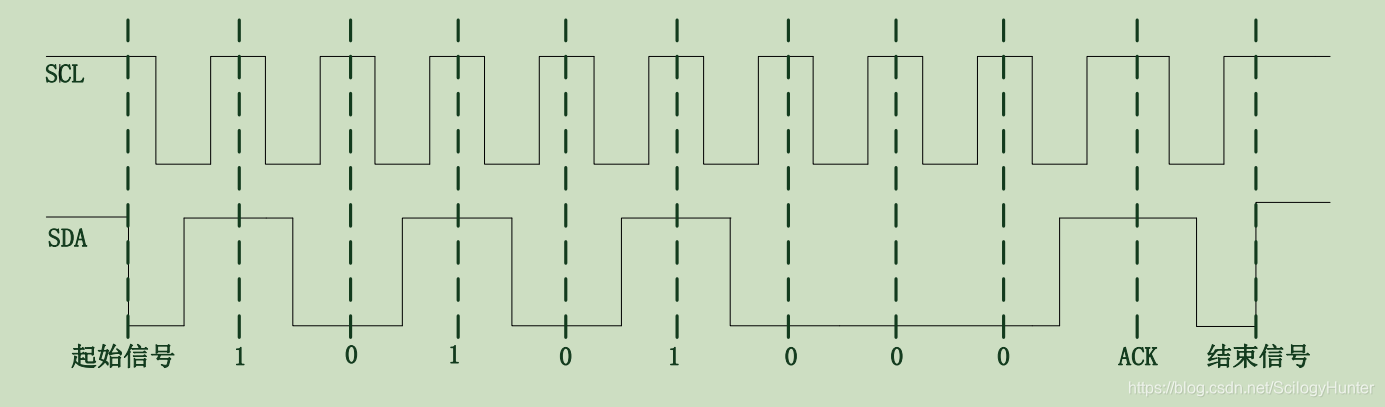

帧时序

- I2C通信以帧为单位,每一帧是一次通信。

- 帧时序从主机发送起始信号开始到主机发送停止信号结束。

- 起始信号和停止信号之间也可以再有起始信号(restart),restart结束前面的帧开启一下帧。

- 起始信号和停止信号之间是若干个通信字,每个通信字有9个数据位,其中前8个位由发送方发送,最后一位由接收方发送,为响应位。

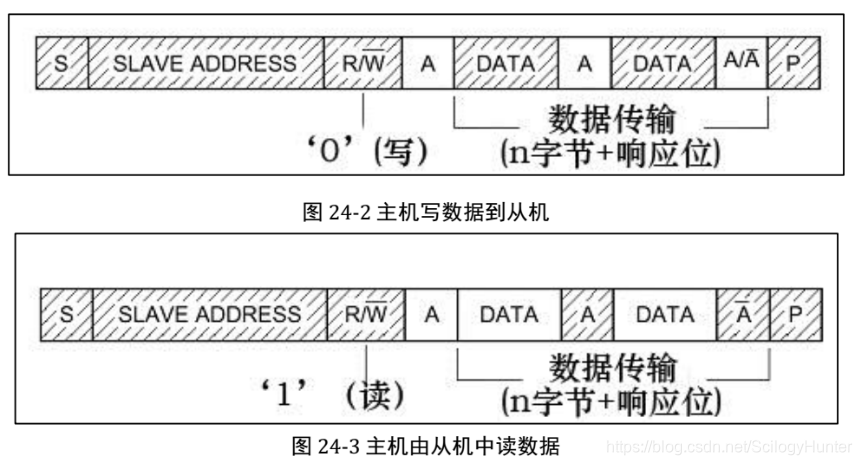

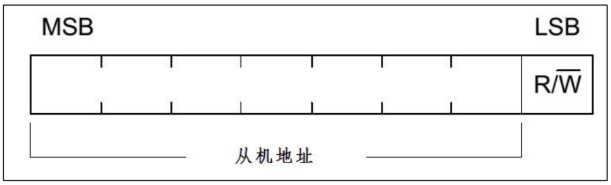

- 起始信号后的第一个通信字为地址字,由主机发出,高7位是从机地址,然后是读写标志位,然后是从机发送的响应位。

- 地址字后是数据字,谁是发送方由地址字的读写位决定。前8位为发送数据字节,从 MSB 开始传输。

地址字

I2C 总线上的每个设备都有自己的独立地址,主机发起通讯时,通过 SDA 信号线发送设备地址来确定本帧是要和哪个从机进行通信。 I2C 协议规定设备地址可以是 7 位或 10 位,实际中 7 位的地址应用比较广泛。紧跟设备地址的一个数据位用来表示数据传输方向,它是读写标志位(R/W)。读写标志位为“1”时表示主机由从机读数据,为“0”时表示主机向从机写数据。主机读时,主机会释放对 SDA 信号线的控制,由从机控制 SDA 信号线,主机接收信号;主机写时, SDA 由主机控制,从机接收信号。

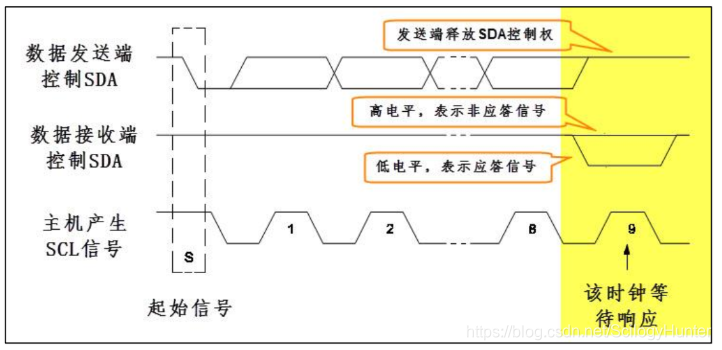

响应位

I2C 的数据和地址传输都带响应。响应包括“应答(ACK)”和“非应答(NACK)”两种信号。

传输时主机产生时钟,在第 9 个时钟时,数据发送端会释放 SDA 的控制权,由数据接收端控制 SDA,若 SDA 为高电平,表示非应答信号(NACK),低电平表示应答信号(ACK)。

当接收端(无论主从机)接收一个字节数据或地址后,若希望对方继续发送,则向对方发送ACK信号,发送方会继续发送下一个数据;若接收端希望结束数据传输,则向对方发送NACK信号,发送方接收到该信号后会产生一个停止信号,结束信号传输。

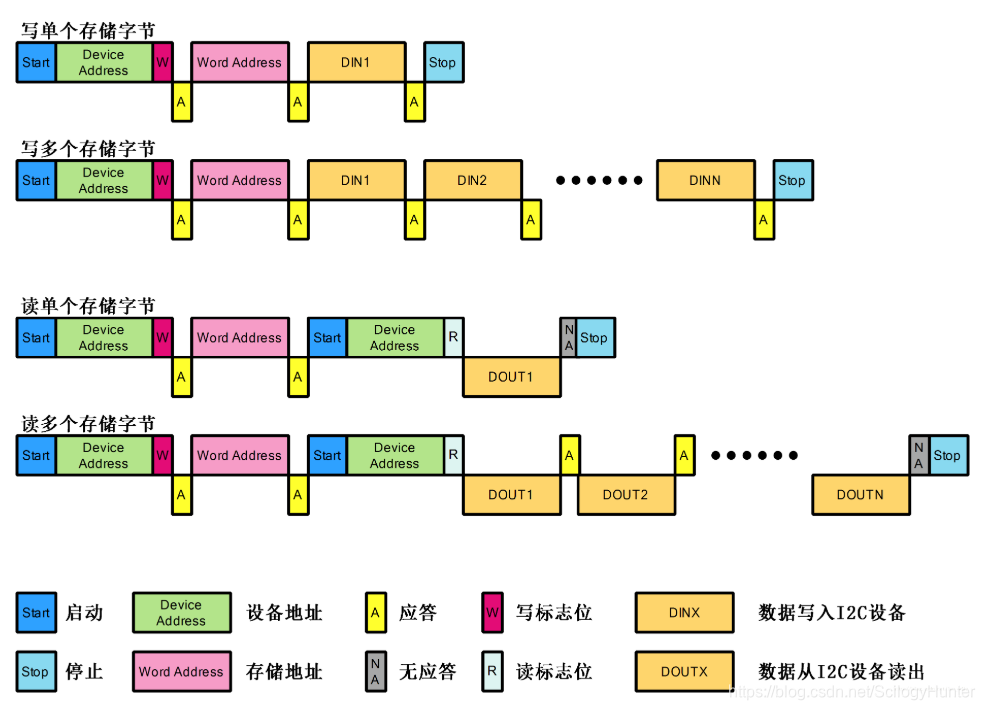

设备访问时序

下面是一个I2C存储器的访问时序图。

297

297

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?