一次X86平台静电整改案例

一、我们知道在电子产品中有一项EMC测试,行业有一定的标准。EMC,大白话讲就是:产品在电磁环境中工作时扛得住,而且还不会产生破坏性的电磁干扰;

静电,就属于EMC(Electronmagnetic Compatibility)中的EMS(Electro Magnetic Susceptibility)一小项;像我们在干燥的冬天从办公椅起身或者衣物摩擦,触摸门把手的,和别人接触,都可能会冷不丁的电一下,这其实对我们的电子产品比如电视,平板,电脑等等,同样会产生相同的挑战。

二、实验做的就是模拟人体的放电,分为接触和空气,对比对产品造成的损害;

2.1 行业一般产品设定4个Level,简单了解到的是一般要求是Level 2及以上。不排除企业制定各自的内部标准,像我了解到的某大牌显示器公司其标准卡在Level 4; 本身是好的,但性能过剩带来的是这个成本的上涨,其实生活中L4级的消费类电子差异和L3级不会给消费者带来很大差异。

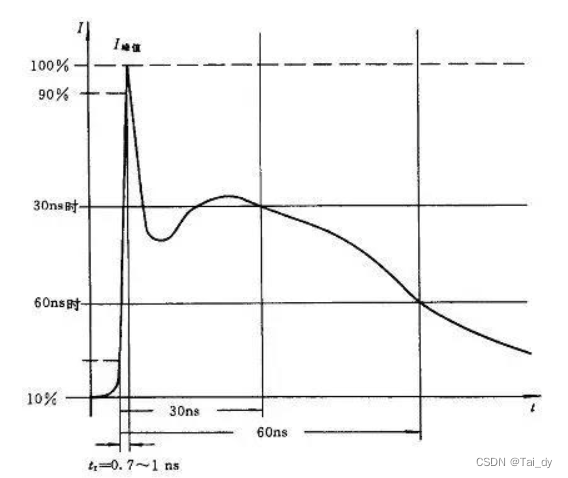

2.2 言归正传,放电波形长啥样?

下图就是IEC制定的标准放电波形参数,操作的是峰值和开关时间,其实有在一处资料中看过研究者对这段波形进行频率分量提取,发现有段300MHz的主能量;这里不多介绍,感兴趣的朋友可以去申请标准文档进一步了解;

2.3 静电释放在产品的哪个位置?

按照标准实验室来测试的话,有水平,垂直耦合版,端子,接触面等;

金属类的可以直接接触到的以接触型测试,非金属或者无法接触或者圆弧以空气放电测试;没有很严格的全照标准给大家解释,因为此文只是个简单分享我遇到的问题;

2.4 哪种程度才叫,不产生破坏性不可恢复性损坏?

实施完静电干扰后,会对产品进行检测,

Class A: 无影响,正常工作;

Class B: 有影响,但可自行恢复;

Class C:有影响,不可恢复;

一般测试时,有连接网络或者播放音视频文件,连接显示器等;观察文件是否读取错误?播放是否终止或者出现杂音或者机器宕机,蓝屏,花屏死机等;B类自行恢复,因为Windos重启这种时间比较长,一般超过自行恢复定义的时间,也就是闪一下屏幕,画面抖动一下这种,算自行恢复;

**三、**我遇到的问题

产品送测试宕机,播放视频中,4K不到接触放电宕机,空气5K宕机;

怀疑的原因:

是否是单端子差异?

是否是接地不良?

3.1 USB端口,RJ45,HDMI都无法通过这个测试;----非单端子差异

3.2 接地的话,就得用上传统意义上的导电材料这些,针对性对USB端口和 LAN 接地,大致改善了500V的提升,但还是Fail;

3.3 参照之前的整改思路,导电材料可以解决85%ESD测试遇到的问题,但是这次他失效了;

3.4 当时做了以下排查:

内存条? 敏感部分?哪些电源没了? 布局?

3.4.1 内存条 当时是同规格的DDR 试了快8个品牌型号,

能承受得住的是一款国外厂商和国产某品牌厂商,实际有对比其板上走线差异,并没有得到很好的信息;当时是暂且定义为NAND性能较好;

3.4.2 因为产品是双内存槽,另一边的ESD性能是这边的近3倍;也有从此对比结果上下手,唯二值得怀疑的点:

①性能较好的DDR 距板边距离远于性能较差的 DDR;

如何去作证我们这个猜想:改版往里缩或者用老虎钳子使机壳变形,尽可能的接近猜想状态;

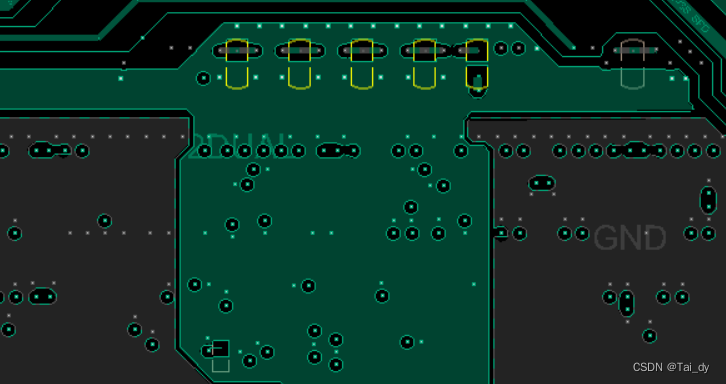

②Layout 与其同布局的另一个案子做对比,无非查到的是主板底面的滤波电容,较好的磷化工一个板子是放在Top面,而此案子是放在底层;

③做过这样一个实验,将Bottom 层的电容全部去件,发现Air ESD可以通过 12KV,但是接触还是剩下 LAN 通过不了,数值还是只能到达3.5K左右,后面不断地针对RJ45 周围的电路去整改;

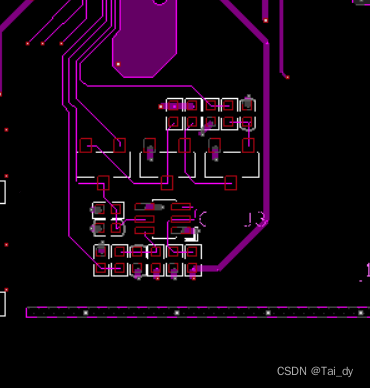

3.4.3 下图是产品的是时序电路部分,很不幸其放置在板边边缘位置,且其电压在0-1.1V,后面在整改测试中,此部分电路损坏,MOS损坏,想这是改版将其移向内部,看过某本资料说过,敏感电路距离板边8mm以上;但后续改版验证这里并没有体现出改善点,说明根结还不在这里。

3.4.5 继续找接触放电Fail的可能性

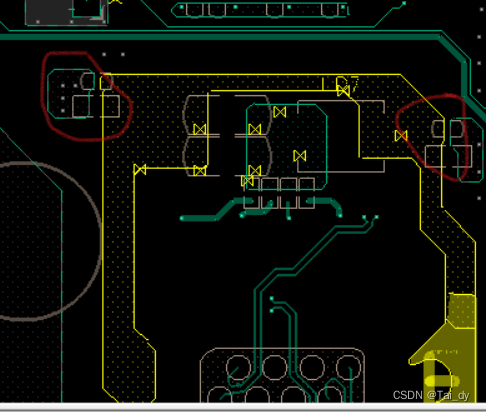

RJ45 是可以分析到什么吗?如下Layout 放置串接阻容做了地隔离,尝试着完全拿掉去研究这个事情,但还是无效,几乎没有效果提升;虽然这种设计更多是面向干扰串到Ethernet上而预留的设计;

四、 继续研究----回到源头

4.1 感觉这个是出发系统宕机,更多的像是DDR或者SSD的问题或者 CPU某部分的问题,反而不像是外设造成的原因,于是先排查DDR, 发现当能量从像是从接触馈到底层;

4.2 我们都常说,干扰源–>传播路径–>被干扰物体。

4.3 我们的所有思路都是基于这一基本准则去执行,本文中的案例属于外置干扰源所以本质上,我们应该是从传播路径和被干扰物体上下手。

传播路径–相关的reset 信号,EN 信号,Power 等,一顿排查下来,最后发现是

- reset信号的串阻比较低,吸收能量能力较差,给其适当增加串阻可以扩大好几倍的防护能力

- reset信号经过bottom层,更加怀疑点一,所以建议敏感线路放置top层,且距离板边较远;

- DDR 处未上件的电源滤波电容,建议都上件;尤其是VDDQ 电源;

- DDR 摆放的位置,建议与板边金属结构件预留8mm以上距离;

4.4 被干扰物体?-----被干扰物体较多,很难立刻判定是具体到哪个部分,然后试着改版调换位置,辅料增加,屏蔽层的参与,并没有很好的解决EMC问题;

**五、**以上的措施导入,确实可以达到标准测试通过,所以针对此现象的宕机更多的是怀疑 内存的数据读写中遭受到静电的大量干扰,从而停止了工作,现象就是宕机无操作反馈;

也不需要增肌辅料类,从而给自己,采购,制造带来一定的繁琐工作量;从源头直接解决问题,一向都应该支持和秉承;

好了,感觉有点虎头蛇尾的写法,改天有机会再补充这份EMC整改内容,网友海涵;

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?