xilinx mig ddr 控制器ip使用代码,包括ddr2,ddr3,ddr4,代码内容为向ddr内部连续写入一串数据,再连续读出,以此测试ddr控制器功能。

均经过下板验证。

ddr3,ddr4工程包括testbench,ddr2基于nexys4 ddr开发板上的ddr完成,此外,提供一份说明文档

ID:5430650468683091

云赐记

标题:Xilinx MIG DDR控制器IP使用代码解析及功能测试

摘要:本文主要介绍了Xilinx MIG DDR控制器IP的使用代码,包括DDR2、DDR3和DDR4版本。通过向DDR内部连续写入一串数据,再连续读出,实现对DDR控制器功能的测试。同时,本文还提供了针对DDR3和DDR4的工程,包括testbench,并附上了详细的说明文档。值得注意的是,由于工程文档的可复制性,一旦售出概不退换。

-

引言

Xilinx MIG DDR控制器IP是一款用于实现DDR存储器控制器的重要工具。本文将通过分析DDR2、DDR3和DDR4版本的MIG DDR控制器IP使用代码,对其功能进行深入解析,并介绍相应的测试方法。 -

Xilinx MIG DDR控制器IP概述

Xilinx MIG DDR控制器IP是一款专门为FPGA设计的DDR存储器控制器,支持DDR2、DDR3和DDR4等多种类型的DDR存储器。其核心功能包括数据读写、控制信号生成与处理、时序控制等。MIG DDR控制器IP的灵活性和可配置性使得其成为设计者在FPGA中使用DDR存储器的理想选择。 -

MIG DDR控制器IP使用代码详解

本文将分别针对DDR2、DDR3和DDR4版本的MIG DDR控制器IP使用代码进行详细解析,包括数据写入和读取过程的具体实现。

3.1 DDR2版本使用代码详解

针对DDR2版本的MIG DDR控制器IP使用代码,本文将介绍其在Nexys 4 DDR开发板上的实现方法。通过详细讲解testbench的搭建和相应的配置参数,读者将能够快速上手并运行DDR2的测试。

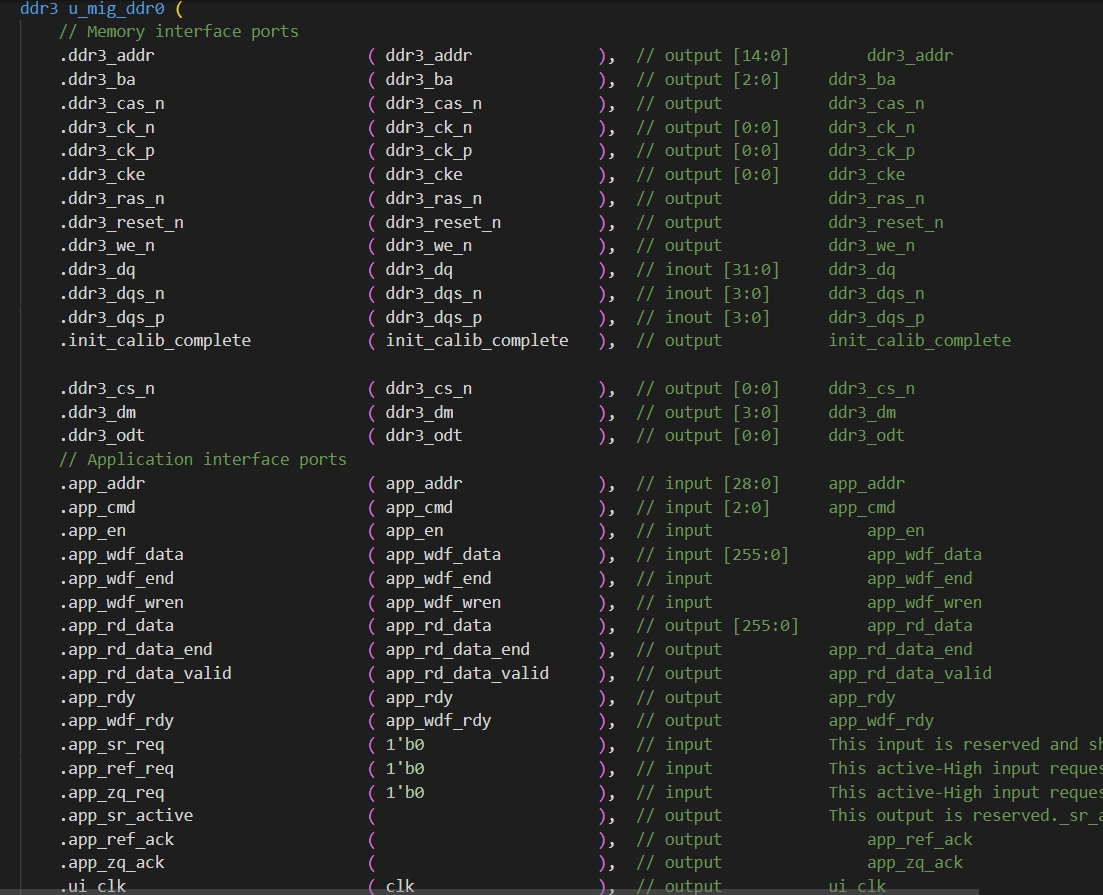

3.2 DDR3版本使用代码详解

对于DDR3版本的MIG DDR控制器IP使用代码,本文将同样介绍其在Nexys 4 DDR开发板上的实现方法。通过详细解释testbench的搭建和必要的配置参数,读者将能够轻松运行DDR3的测试,并深入理解DDR3存储器控制器的工作原理。

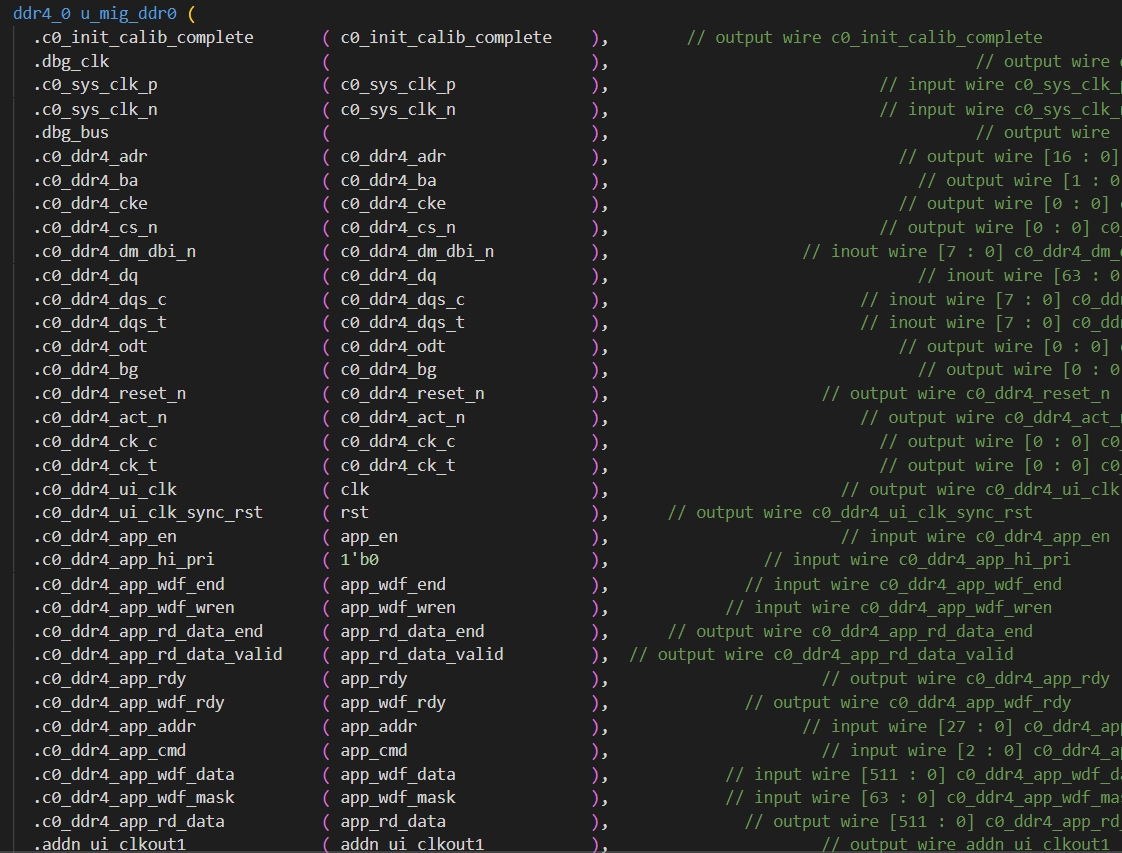

3.3 DDR4版本使用代码详解

最后,本文将对DDR4版本的MIG DDR控制器IP使用代码进行详细讲解。通过解析testbench的构建和关键配置参数,读者将能够顺利运行DDR4的测试,并对DDR4存储器控制器的特性有更加全面的认识。

-

MIG DDR控制器功能测试方法

为了验证DDR控制器的功能和正确性,本文提供了基于连续写入一串数据再连续读出的方法。通过该测试方法,读者可以对MIG DDR控制器IP在不同DDR版本下的功能进行全面的评估。 -

工程文档说明

本文还提供了针对DDR3和DDR4版本的工程文档说明,其中包括详细的搭建步骤、配置参数以及其他必要的说明。这些文档将帮助读者更好地理解和使用MIG DDR控制器IP,并提供相应的技术支持。

相关的代码,程序地址如下:http://coupd.cn/650468683091.html

4421

4421

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?