I-Code 总线和D-Code 总线

在系统中,存在两种主要类型的总线:I-Code 总线和 D-Code 总线,它们基于 AHB-Lite 总线协议。这两种总线在不同的地址范围内进行操作。

I-Code 总线的作用是进行指令的取指和执行。它负责在地址范围 0x0000_0000 到 0x1FFF_FFFF 之间的取指操作。这个总线是一条 32 位的总线,采用字(32 位)的长度进行取指操作,即使是对于 16 位的 Thumb 指令,也是以字的方式处理。这种设计使得 CPU 内核能够一次性取出两条 16 位的 Thumb 指令。

D-Code 总线则用于数据的读写访问。类似于 I-Code 总线,它也是基于 AHB-Lite 总线协议,使用 32 位的数据总线。D-Code 总线负责在与 I-Code 相同的地址范围(0x0000_0000 到 0x1FFF_FFFF)内进行数据访问操作。尽管 Cortex-M3 处理器支持非对齐访问,但是由于总线接口的设计,任何连接到 D-Code 总线上的设备都只需要支持 AHB-Lite 的对齐访问,而不需要支持非对齐访问。

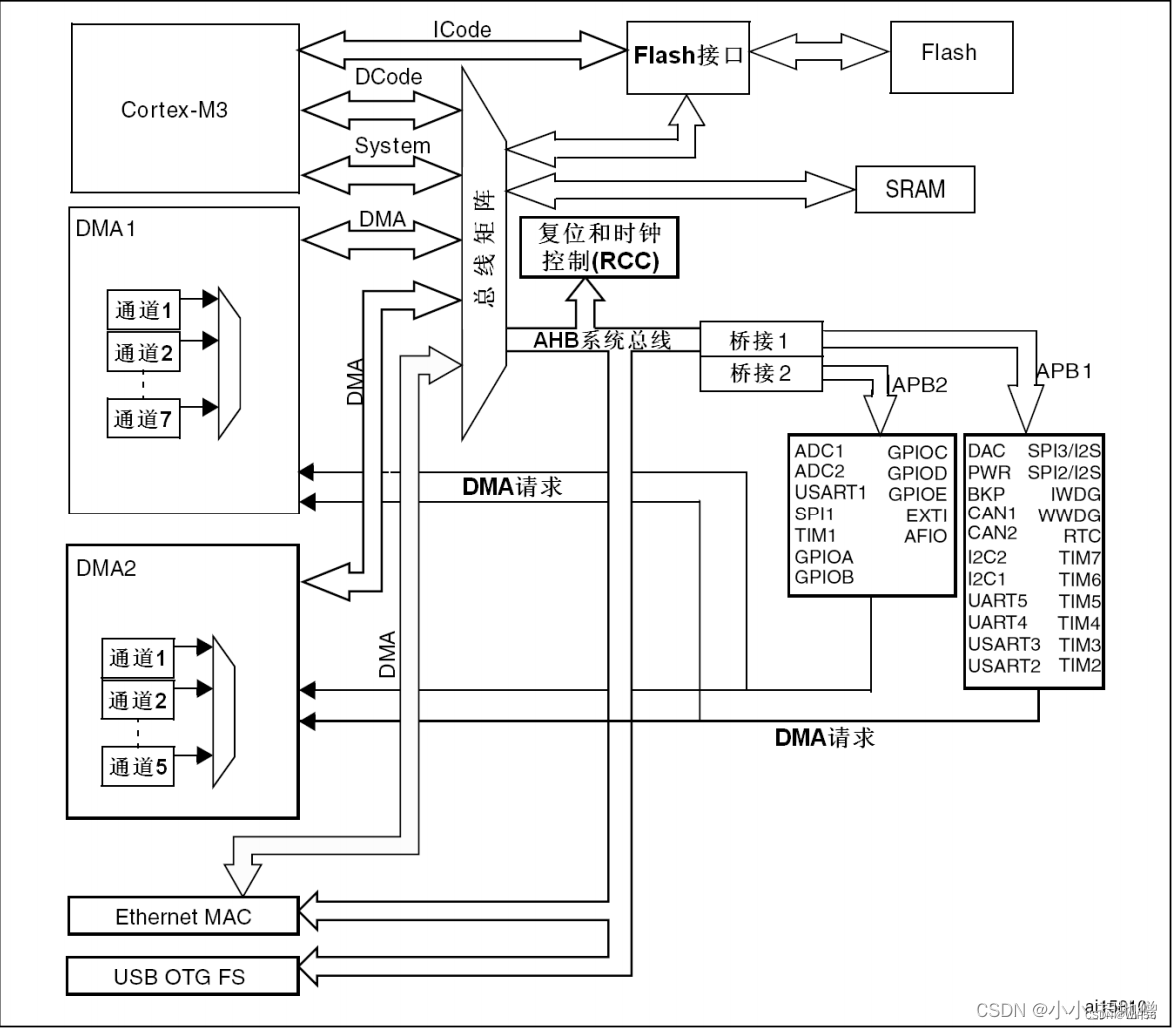

(一)、stm32系统构架

- 主系统由以下部分构成:

●

四个驱动单元:

─ Cortex™-M3内核DCode总线(D-bus)

─ 系统总线(S-bus)

─ 通用DMA1和通用DMA2●

四个被动单元

─ 内部SRAM

─ 内部闪存存储器 ─ FSMC

─ AHB到APB的桥(AHB2APBx),它连接所有的APB设备

- 在互联型产品中,主系统由以下部分构成:

●

五个驱动单元:

─ Cortex™-M3内核DCode总线(D-bus),和系统总线(S-bus)

─ 通用DMA1和通用DMA2

─ AHB到APB的桥(AHB2APBx),它连接所有的APB设备

●三个被动单元:

─ 内部SRAM ─ 内部闪存存储器

─ AHB到APB的桥(AHB2APBx),它连接所有的APB设备

1094

1094

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?