芯片ESD失效分析指南

1. 概述

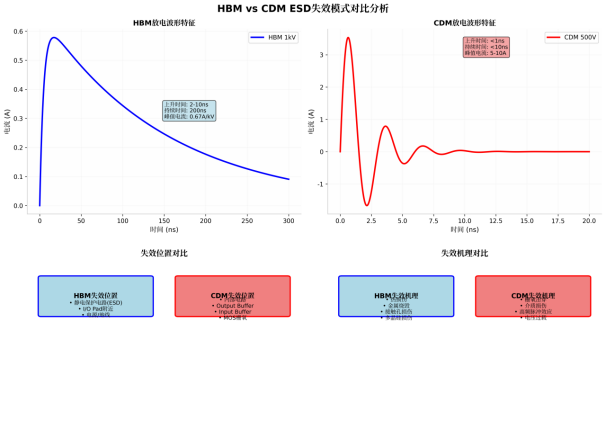

静电放电(ESD)是导致芯片失效的主要原因之一。在半导体制造、组装、测试和运输过程中,芯片可能遭受不同类型的ESD事件。其中,人体放电模式(HBM)和充电器件模式(CDM)是最常见的两种ESD模型。准确判断失效模式对于改进ESD防护措施和提高产品可靠性至关重要。

2. HBM与CDM基础概念

2.1 人体放电模式 (HBM)

定义:模拟人体带电接触芯片时的放电事件

- 等效电路:100pF电容 + 1.5kΩ电阻

- 波形特征:

- • 上升时间:2-10 ns

- • 持续时间:约200 ns

- • 峰值电流:0.67 A/kV

- 常见场景:人工操作、手工装配、维修过程

2.2 充电器件模式 (CDM)

定义:模拟芯片本身带电后向接地导体放电的事件

- 等效电路:芯片自身电容 + 极小电阻(<10Ω)

- 波形特征:

- • 上升时间:<1 ns

- • 持续时间:<10 ns

- • 峰值电流:5-10 A (比HBM高10-20倍)

- 常见场景:自动化产线、SMT贴片、测试分选机

3. HBM与CDM关键区别对比

|

对比项 |

HBM |

CDM |

|

放电机制 |

外部人体放电 |

内部电荷释放 |

|

失效位置 |

ESD保护电路、I/O Pad附近 |

内部电路、Buffer、栅氧 |

|

失效模式 |

热损伤、金属烧毁、接触孔损伤 |

栅氧击穿、介质损伤 |

|

能量特性 |

能量大、持续时间长 |

能量小、瞬时功率高 |

|

防护等级 |

通常较高(≥2000V) |

较低(100-500V) |

|

测试电压 |

2000V (典型) |

250V (典型) |

|

重复性 |

随机性、位置不确定 |

固定位置、易重复 |

4. ESD失效判断方法

4.1 失效位置分析

HBM失效位置特征:

- ✓ 主要发生在ESD保护电路区域

- ✓ I/O Pad附近区域

- ✓ 电源和地线连接处

- ✓ 保护二极管、电阻、MOS管等保护器件

CDM失效位置特征:

- ✓ 内部核心电路区域

- ✓ Output Buffer/Input Buffer

- ✓ MOS管栅氧层

- ✓ 内部逻辑电路

4.2 失效模式识别

HBM典型失效模式:

- • 金属线烧毁 (Metal Burn-out)

- • 接触孔损伤 (Contact Spiking)

- • 结区损伤 (Junction Damage)

- • 多晶硅损伤 (Poly-extrusion)

- • 热损伤痕迹明显

CDM典型失效模式:

- • 栅氧击穿 (Gate Oxide Breakdown)

- • 介质损伤

- • MOS管栅极损坏

- • 高频脉冲导致的局部击穿

- • 无明显热损伤痕迹

4.3 电气特性分析

关键测试参数:

- 1. I-V特性曲线对比

- - HBM: 通常表现为电阻性短路或开路

- - CDM: 栅氧击穿后呈现特定漏电流特征

- 2. 漏电流测试

- - 测试条件: 1μA时的电压变化

- - 判断标准: 变化>30%判定为失效

- 3. 功能测试

- - 参数测试: 静态电流、漏电流

- - 功能测试: 逻辑功能验证

4.4 物理失效分析(FA)

分析步骤:

- ① 热点定位 (Hot Spot Analysis)

- - 使用EMMI或OBIRCH定位失效点

- - 记录失效位置分布

- ② 去层分析 (De-layering)

- - 逐层去除芯片钝化层

- - SEM检查各层结构

- ③ 截面分析 (Cross-section)

- - FIB切割失效区域

- - TEM观察微观结构损伤

- ④ 元素分析

- - EDX分析损伤区域成分

- - 确认失效机制

5. 系统化的失效判断流程

5.1 快速判断检查表

|

检查项 |

HBM倾向 |

CDM倾向 |

|

失效位置 |

I/O区域、保护电路 |

内部电路、Buffer |

|

失效模式 |

热损伤、金属烧毁 |

栅氧击穿、介质损伤 |

|

放电环境 |

人工操作、维修 |

自动产线、SMT |

|

重复性 |

随机、位置不确定 |

固定位置、可重复 |

|

电压等级 |

高电压(>1000V) |

低电压(<500V) |

5.2 决策树分析

- 问题1: 失效发生在哪个区域?

- → I/O Pad附近或保护电路 → 倾向HBM

- → 内部电路或Buffer区域 → 倾向CDM

- 问题2: 失效模式是什么?

- → 金属烧毁、热损伤、接触孔损伤 → 倾向HBM

- → 栅氧击穿、无明显热损伤 → 倾向CDM

- 问题3: 失效发生的场景?

- → 人工操作、维修、手工测试 → 倾向HBM

- → 自动产线、SMT、分选机 → 倾向CDM

- 问题4: 失效的重复性?

- → 随机位置、不可重复 → 倾向HBM

- → 固定位置、可重复 → 倾向CDM

6. 实际案例分析

案例1: CMOS芯片I/O引脚ESD失效

背景:某CMOS芯片在最终测试阶段发现I/O引脚对地短路

分析过程:

- • 电气测试: I/O引脚对地电阻约50Ω,正常应为高阻

- • 热点分析: EMMI在I/O Pad附近发现发光点

- • 物理分析: SEM观察到保护二极管金属线烧毁

- • 失效模式: 金属烧断、有明显热损伤痕迹

- • 发生场景: 人工插拔测试

结论:

✓ 失效位置在保护电路区域

✓ 金属烧毁是典型的热损伤

✓ 人工操作场景符合HBM特征

✓ 综合判断: HBM导致的ESD失效

案例2: 高速数字芯片内部失效

背景:高速数字芯片在SMT贴片后功能异常

分析过程:

- • 电气测试: 输出Buffer漏电流超标

- • 功能测试: 输出端口驱动能力下降

- • 热点分析: OBIRCH定位到Output Buffer区域

- • 物理分析: TEM观察到MOS管栅氧层击穿

- • 失效模式: 栅氧击穿、无明显热损伤

- • 发生场景: SMT贴片过程

结论:

✓ 失效位置在内部Buffer电路

✓ 栅氧击穿是CDM典型特征

✓ SMT贴片是CDM高发场景

✓ 综合判断: CDM导致的ESD失效

案例3: 混合信号芯片复杂失效

背景:混合信号芯片在温湿度老化测试后失效

分析过程:

- • 电气测试: 多引脚功能异常

- • 热点分析: 发现多个热点分布

- • 物理分析: 部分保护电路烧毁,部分内部电路栅氧损伤

- • 失效模式: 混合模式(热损伤+栅氧击穿)

结论:

✓ 存在多种失效模式

✓ 可能同时受到HBM和CDM影响

✓ 需要进一步分析失效时序

✓ 综合判断: 复合ESD失效事件

7. ESD防护措施建议

7.1 HBM防护策略

人员防护:

- • 佩戴防静电手环,确保接地良好

- • 穿戴防静电服装和鞋帽

- • 定期检测人员接地电阻

环境控制:

- • 控制环境湿度(40%-60%RH)

- • 使用防静电地板和工作台

- • 安装离子风机消除静电

操作规范:

- • 避免直接触摸芯片引脚

- • 使用防静电工具操作

- • 建立标准操作流程(SOP)

7.2 CDM防护策略

设备防护:

- • 确保所有设备可靠接地

- • 使用防静电材料制作夹具

- • 定期检测设备接地状态

工艺控制:

- • 降低贴片速度,减少摩擦起电

- • 使用导电性或耗散性材料

- • 优化测试分选机工艺参数

芯片设计:

- • 加强内部电路ESD保护

- • 优化Output Buffer设计

- • 提高栅氧层抗ESD能力

8. 测试验证方法

8.1 HBM测试方法

测试标准:

- • ANSI/ESDA/JEDEC JS-001

- • JEDEC JESD22-A114

- • AEC-Q100-002 (汽车电子)

测试方法:

- 1. Pin-to-Pin测试

- - 每个引脚对其他所有引脚放电

- - 正负极性各测试一次

- 2. Pin-to-VDD测试

- - I/O引脚对VDD引脚放电

- 3. Pin-to-GND测试

- - I/O引脚对GND引脚放电

- 4. VDD-to-GND测试

- - 电源引脚对地引脚放电

失效判据:

- • 参数漂移超过±30%

- • 漏电流超过规格

- • 功能测试失败

- • I-V曲线超出包络线

8.2 CDM测试方法

测试标准:

- • ANSI/ESDA/JEDEC JS-002

- • JEDEC JESD22-C101

- • AEC-Q100-011 (汽车电子)

测试方法:

- 1. 场感应充电法(FI-CDM)

- - 芯片放置在充电板上

- - 通过电场感应充电

- - 探针接触引脚放电

- 2. 直接充电法(D-CDM)

- - 通过高阻电阻直接充电

- - 逐个引脚放电测试

测试要点:

- • 每个引脚都要测试

- • 正负极性各测试一次

- • 从低电压开始逐步升高

- • 记录最小失效电压

8.3 失效阈值对比

|

技术节点 |

HBM阈值 |

CDM阈值 |

|

0.35μm |

>4000V |

>1000V |

|

0.18μm |

2000-4000V |

500-1000V |

|

90nm |

1000-2000V |

250-500V |

|

65nm |

500-2000V |

125-250V |

|

40nm |

500-1000V |

50-125V |

9. 常见问题与解决方案

问题1: 如何区分HBM和CDM的混合失效?

- 解决方案:

- • 分析失效时序,确定哪个是主失效

- • 检查失效位置分布,判断失效源头

- • 结合生产工艺和历史数据

- • 必要时进行失效重现测试

问题2: 为什么CDM阈值越来越低?

- 原因分析:

- • 工艺尺寸缩小,栅氧层变薄

- • 供电电压降低,抗ESD能力减弱

- • 芯片复杂度增加,内部节点增多

- • 封装密度提高,CDM风险增加

问题3: 如何提高CDM防护能力?

- 设计层面:

- • 优化Output Buffer设计,增加栅氧厚度

- • 在关键节点增加内部ESD保护

- • 改善电源网络布局,降低阻抗

- • 使用保护环(Guard Ring)隔离

- 工艺层面:

- • 选择抗ESD能力强的工艺

- • 优化金属层厚度和通孔设计

- • 使用高介电常数材料

- 封装层面:

- • 使用导电性封装材料

- • 优化引脚布局和走线

- • 增加芯片与封装之间的绝缘

10. 总结

准确判断芯片ESD失效是由HBM还是CDM导致,需要综合考虑多个因素:

关键判断要点:

- 1. 失效位置:HBM主要在I/O和保护电路,CDM主要在内部电路

- 2. 失效模式:HBM以热损伤为主,CDM以栅氧击穿为主

- 3. 放电环境:HBM与人工操作相关,CDM与自动化产线相关

- 4. 波形特征:HBM能量大持续时间长,CDM能量小瞬时功率高

通过系统化的失效分析流程,结合电气测试、物理分析和场景分析,可以准确判断ESD失效模式,为改进ESD防护措施提供依据。

在先进工艺节点下,CDM失效越来越成为主要挑战,需要在设计、工艺、封装和测试等各个环节加强CDM防护,提高芯片的ESD可靠性。

附录:参考图表

图1: HBM vs CDM波形特征对比

图2: ESD失效分析流程图

2355

2355

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?