任务描述

设计一个3线-8线译码器。运用Verilog HDL进行设计,完善译码器的功能描述风格代码,具备组合逻辑电路的设计仿真和测试的能力。

相关知识

需要掌握: 1.3线-8线译码器的功能; 2.如何用case语句进行逻辑功能的描述。

( 本文不是枚举, 用到了合并和位运算 )

3线-8线译码器的功能

译码是编码的逆过程,3线-8线译码器可以将n位二进制代码可译成2n种电路状态。译码器框图如下所示。

case语句

case语句是一个多路条件分支形式,其语法如下:

case(case_expr)

case_item_expr{ ,case_item_expr} : procedural_statement

. . . . . .

[default: procedural_statement]

endcase

case语句首先对条件表达式case_expr求值,

然后依次与各分支项求值并进行比较,

第一个与条件表达式值相匹配的分支中的语句被执行。

可以在1个分支中定义多个分支项;

这些值不需要互斥。

缺省分支覆盖所有没有被分支表达式覆盖的其他分支。

case语句的实例如下 :

always@ (A or B or OpCode)

case (OpCode)

2'b00: Y = A + B;

2'b01: Y = A -B;

2'b10: Y = A * B;

2'b11: Y = A / B;

default:Y = 0;

endcase编程要求

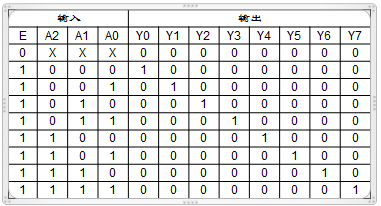

根据提示,在右侧编辑器补充代码,设计具有一位使能端的3线-8线译码器。当使能端为0时,8位输出信号全为0;如果一位使能信号为1,则输出高电平有效的译码信号。该译码器真值表如下所示。

说明

本文仅是在下列的基础上进行优化,方法与C语言类似,通过观察真值表发现,A2A1A0组成的二进制数即表示,当使能端输入信号为1时,其左移多少位得到的Y值(A2、Y7分别为高位)

源代码

//设计具有一位使能端的3线-8线译码器。当使能端为0时,8位输出信号全为0;

//如果一位使能信号为1,则输出高电平有效的译码信号。

module decoder3e_test(a,ena,y);

input [2:0] a;

input ena;

output [7:0] y;

// 请在下面添加代码,完成设计任务

/* Begin */

wire[2:0] a;

wire ena;

reg [7:0] y;

always@ (ena or a)

begin

case(ena)

1'b0: y = 8'b00000000;

1'b1: y = ena << {a[2], a[1], a[0]};

endcase

end

/* End */

endmodule

其中{a[2], a[1], a[0]} 即表示一个拼接而成的以a[2]为高位的顺位的二进制数

本文介绍了如何使用VerilogHDL设计一个具有一位使能端的3线-8线译码器。在使能端为0时,输出全为0;当使能端为1且任意一位输入信号为1时,输出对应的高电平译码信号。设计中运用了case语句进行逻辑功能描述,并提供了相应的源代码示例。

本文介绍了如何使用VerilogHDL设计一个具有一位使能端的3线-8线译码器。在使能端为0时,输出全为0;当使能端为1且任意一位输入信号为1时,输出对应的高电平译码信号。设计中运用了case语句进行逻辑功能描述,并提供了相应的源代码示例。

5313

5313

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?