频域滤波FPGA设计实现,采用Verilog语言设计。

该模块可自动搜索输入信号频率并滤除带外噪声

ID:53600658054188493

FPGA信号处理算法设计

频域滤波是一种常用的数字信号处理技术,在许多应用领域都有广泛的应用。本文将围绕频域滤波在FPGA设计中的实现展开讨论,重点介绍使用Verilog语言设计的一种自动搜索输入信号频率并滤除带外噪声的模块。

随着现代通信技术和嵌入式系统的快速发展,对信号质量的要求越来越高。然而,由于环境噪声、传输干扰以及设备自身引入的噪声等原因,输入信号往往会被附加上一些无用的噪声,从而影响到系统的性能和可靠性。频域滤波技术通过在信号的频域上进行处理,可以有效地消除这些带外噪声,从而提高信号的质量。

在FPGA设计中实现频域滤波需要借助硬件描述语言来描述滤波器的结构和功能。Verilog是一种常用的硬件描述语言,具有语法简洁、易于理解和便于调试等优点,因此在本文中我们选择使用Verilog语言进行设计。

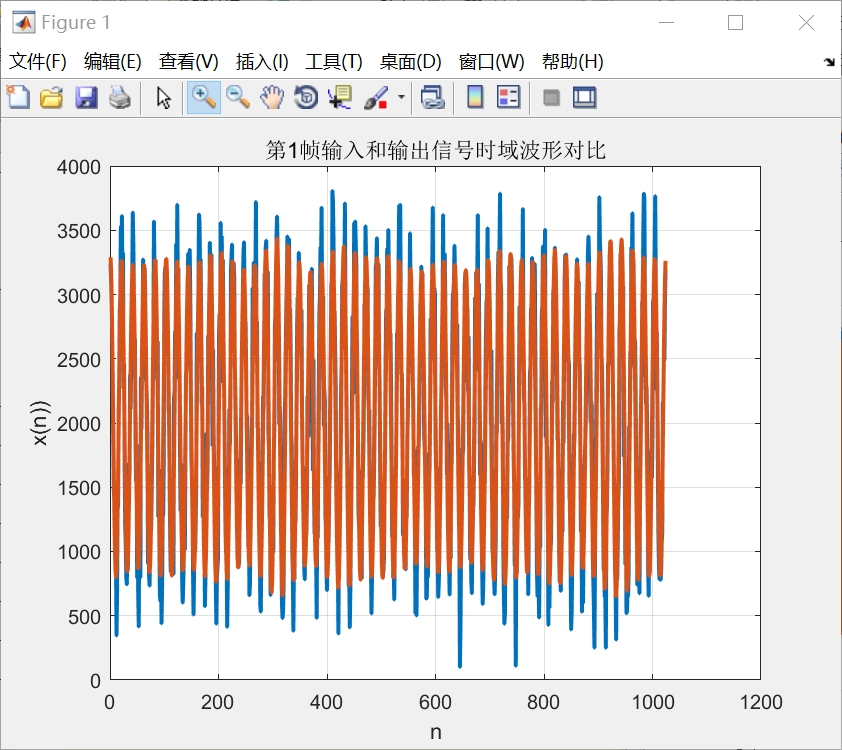

首先,我们需要确定滤波器的处理范围和要达到的滤波效果。根据输入信号的频率范围和带外噪声的幅度,可以选择合适的滤波算法和参数。常见的滤波算法包括低通滤波、高通滤波、带通滤波和带阻滤波等。根据实际需求,本设计选择了带通滤波算法,并采用了自动搜索输入信号频率的方法来确定滤波器的中心频率和带宽。

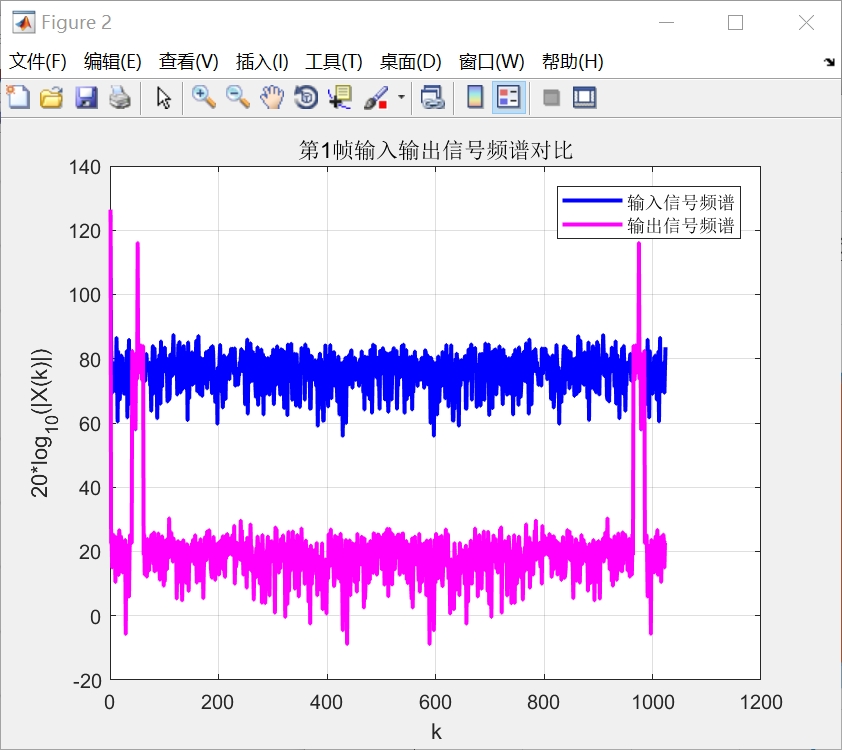

在Verilog设计中,我们可以使用FFT(快速傅里叶变换)算法来实现频域滤波。FFT算法能够快速计算信号的频谱,并将其分为多个频带进行处理。通过对FFT输出的频谱进行分析和处理,我们可以得到输入信号的频率成分和幅度,从而确定滤波器的参数。

为了实现自动搜索输入信号频率的功能,我们需要设计一个能够自动调整滤波器参数的控制模块。这个控制模块可以通过监测输入信号的频率变化来动态调整滤波器的中心频率和带宽,从而实现自适应滤波的效果。在Verilog设计中,我们可以使用有限状态机(FSM)来实现这个控制模块,通过监测输入信号的周期和幅度变化来判断信号的频率,并根据频率的变化来调整滤波器的参数。

除了自动搜索输入信号频率,我们还可以通过设计滤波器的增益和频率响应曲线来进一步优化滤波效果。在Verilog设计中,我们可以使用IIR(无限脉冲响应)滤波器来实现增益调整和频率响应控制。通过调整滤波器的增益和频率响应曲线,我们可以根据实际需求来优化滤波器的性能,从而实现更好的滤波效果。

通过以上设计和实现,我们可以得到一个具有自动搜索输入信号频率并滤除带外噪声功能的频域滤波模块。这个模块可以广泛应用于各种数字信号处理和通信系统中,提供高质量的信号处理和传输能力。

综上所述,本文围绕频域滤波在FPGA设计中的实现展开讨论,重点介绍了使用Verilog语言设计的一种自动搜索输入信号频率并滤除带外噪声的模块。通过对滤波器结构和功能的详细描述,我们可以清楚地了解到这个模块的工作原理和优势。相信这个模块将成为程序员社区中的热门话题,并为广大技术爱好者和工程师带来实用的设计思路和方法。

相关的代码,程序地址如下:http://coupd.cn/658054188493.html

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?