JTAG有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的,各个引脚的定义如下。

一、引脚定义

Test Clock Input (TCK) -----强制要求1

TCK在IEEE1149.1标准里是强制要求的。TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。

Test Mode Selection Input (TMS) -----强制要求2

TMS信号在TCK的上升沿有效。TMS在IEEE1149.1标准里是强制要求的。TMS信号用来控制TAP状态机的转换。通过TMS信号,可以控制TAP在不同的状态间相互转换。

Test Data Input (TDI) -----强制要求3

TDI在IEEE1149.1标准里是强制要求的。TDI是数据输入的接口。所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。

Test Data Output (TDO) -----强制要求4

TDO在IEEE1149.1标准里是强制要求的。TDO是数据输出的接口。所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。

Test Reset Input (TRST) ----可选项1

这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。TRST可以用来对TAPController进行复位(初始化)。因为通过TMS也可以对TAP Controll进行复位(初始化)。所以有四线JTAG与五线JTAG之分。

(VTREF) -----强制要求5

接口信号电平参考电压一般直接连接Vsupply。这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?)

Return Test Clock ( RTCK) ----可选项2

可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地。

System Reset ( nSRST)----可选项3

可选项,与目标板上的系统复位信号相连,可以直接对目标系统复位。同时可以检测目标系统的复位情况,为了防止误触发应在目标端加上适当的上拉电阻。

USER IN

用户自定义输入。可以接到一个IO上,用来接受上位机的控制。

USER OUT

用户自定义输出。可以接到一个IO上,用来向上位机的反馈一个状态

由于JTAG经常使用排线连接,为了增强抗干扰能力,在每条信号线间加上地线就出现了这种20针的接口。但事实上,RTCK、USER IN、USER OUT一般都不使用,于是还有一种14针的接口。对于实际开发应用来说,由于实验室电源稳定,电磁环境较好,干扰不大。

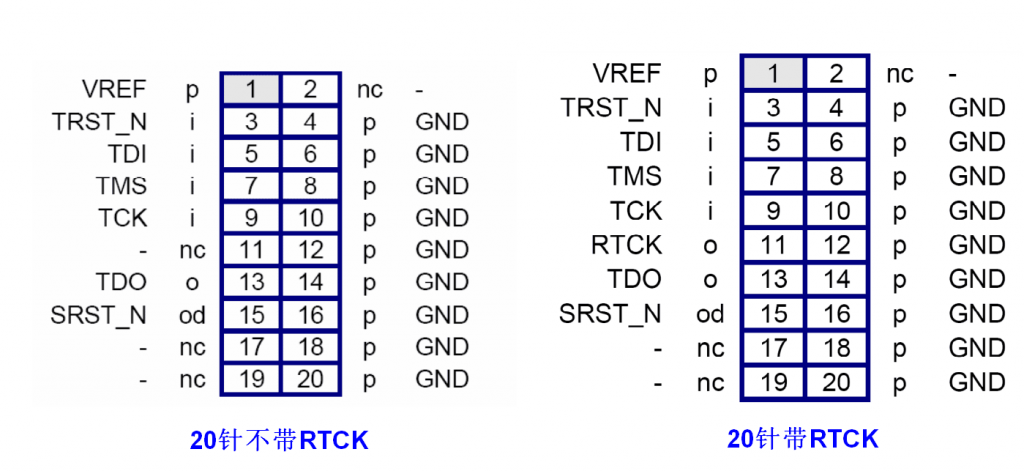

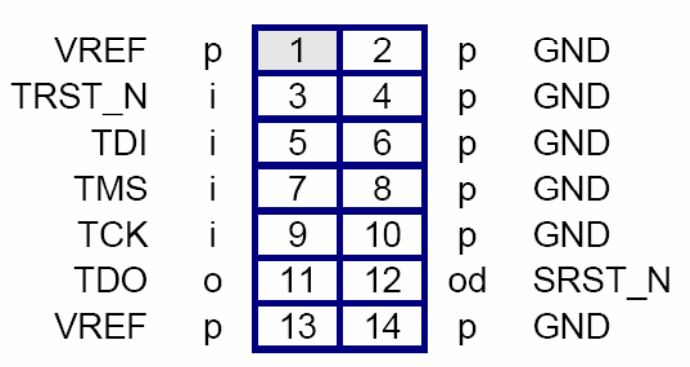

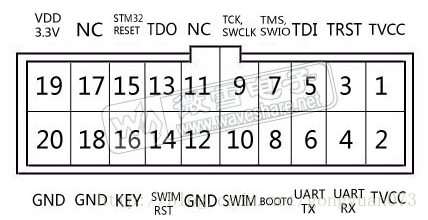

二、20、14、10pin JTAG的引脚名称与序号对应关系

值得注意的是,不同的IC公司会自己定义自家产品专属的Jtag头,来下载或调试程序。嵌入式系统中常用的20、14、10pin JTAG的信号排列如下:

需要说明的是,上述Jtag头的管脚名称是对IC而言的。例如TDI脚,表示该脚应该与IC上的TDI脚相连,而不是表示数据从该脚进入download cable。

实际上10针的只需要接4根线,4号是自连回路,不需要接,1,2接的都是1管脚,而8,10接的是GND,也可以不接。

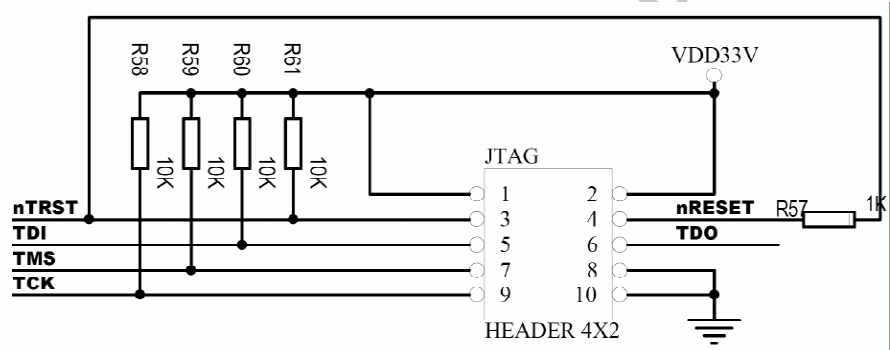

附转接板电路:

JTAG接口的SWD接线方式

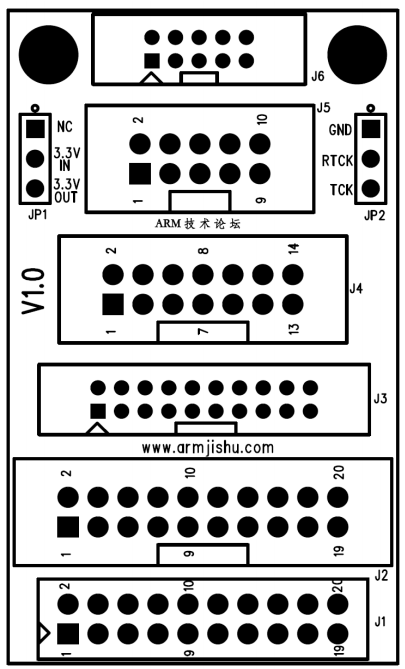

JTAG引脚示意图:

一、SWD 和传统的调试方式区别

1. SWD 模式比 JTAG 在高速模式下面更加可靠

2. GPIO 刚好缺一个的时候, 可以使用 SWD 仿真, 这种模式支持更少的引脚

3. 在板子的体积有限的时候推荐使用 SWD 模式

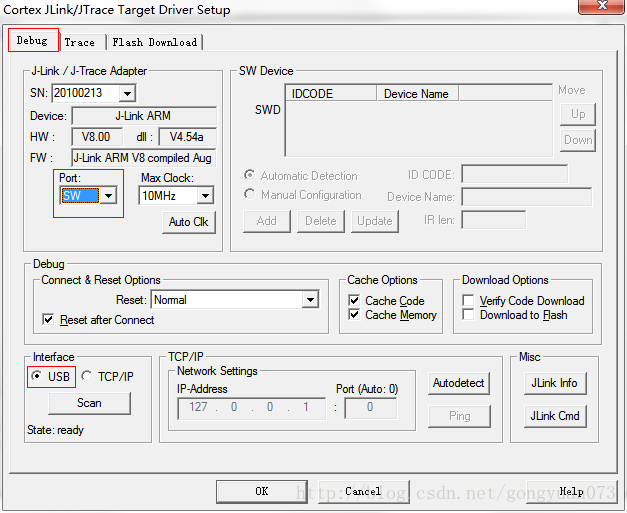

二、仿真器对 SWD 模式支持情况

1. 市面上的常用仿真器对 SWD 模式支持情况

JLINKV8 非常好的支持 SWD 仿真模式, 速度可以到 10M

ULINK2 非常好的支持 SWD 模式, 速度可以达到 10M

2. SWD 硬件接口上的不同

(1) JLINKV7 需要的硬件接口为: GND, RST, SWDIO, SWDCLK

(2) JLINKV8 需要的硬件接口为: VCC, GND, RST, SWDIO, SWDCLK (注:下面有我自己用JLINKV8的实际连线及相应实验结果)

(3) ULINK1 不支持 SWD 模式

(4) ULINK2 需要的硬件接口为: GND, RST, SWDIO, SWDCLK

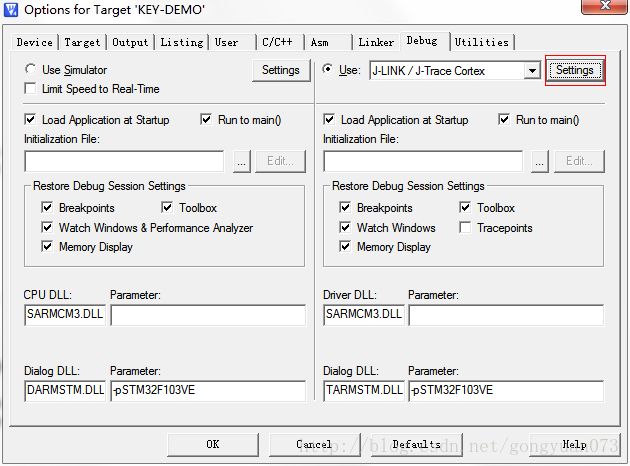

三、在 MDK 中SWD 模式的设置

正常的JTAG需要20管脚,而J-Link 的SWD只需要2根线(PA13/JTMS/SWDIO、PA14/JTCK/SWCLK)就够了(加上电源线也就4根),这样就节省了3个I/O口(PA15/JTDI、PB3/JTDO、PB4/JNTRST)为其它所用,并且可节省一部分板子的空间(只需4个口就可以了)

第一步:

第二步:

另外, JTAG引脚可以被复用为IO口,但是这样一来,JLINK就不能够连上芯片了。解决的方法有两种:

(1)另写一段程序,不要将JTAG复用为I/O口,然后将这段程序用串口工具写入芯片中

(2)将BOOT0/BOOT1设置成为内部RAM启动,那么上电后就不会执行FLASH中的程序,这样JLINK就能顺利“接管”JTAG引脚

实例应用:

10针JTAG与20针JTAG的连接:

下面说一下接法,其实根本不需要什么转接板什么的,直接把相应的几根线对接就可以用了,所以要参考电路图,上面为TQ2440开发板的JTAG电路图,下面为JLINK的20针电路图,下面的JLINKV7电路图是标准接口,网上到处都能找到

10针JTAG针序 | 20针JTAG针序 | 信号 |

| 1,2 | 1 | VTref |

| - | 2 | NC |

| 3 | 3 | nTRST |

| - | 4 | GND |

| 5 | 5 | TDI |

| - | 6 | GND |

| 7 | 7 | TMS |

| 8 | 8 | GND |

| 9 | 9 | TCK |

| 10 | 10 | GND |

| - | 11 | RTCK |

| - | 12 | GND |

| 6 | 13 | TDO |

| - | 14 | GND |

| 4 | 15 | RESET |

| - | 16 | GND |

| - | 17 | DBGRQ |

| - | 18 | GND |

| - | 19 | 5V-Supply |

| - | 20 | GND |

实际上只需要接4跟线,4号是自连回路,不需要接,1,2接的都是1管脚,而8,10接的是GND,也可以不接

4596

4596

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?