电容对高速电路的贡献非常大,即便是在一块最普通的单板上,电容也随处可见。因此,电容是电路设计中最为常见的器件。但同时,电容也是最容易被忽视的器件。在设计中,设计者们往往知道需要放置电容,但对电容的选型却随心所欲。事实证明,很多单板的设计失败,根本原因就在电容。

一、高速电路设计中电容的作用

1、电荷缓冲池

在高速电路设计中,电源的负载是动态的,即高速运行器件的电流和功耗是不断变化的。为了保证器件工作的稳定,希望器件的工作电压不随电流和功耗的剧烈变化而同程度变化,即希望器件电压尽量稳定。在这种情况下,需要为器件提供一种缓冲池,以便当外界环境剧烈变化时,器件的工作电压能保持相对的稳定。电容的本质是储存电荷和释放电荷,当外界环境变化时,电容中的电荷能被迅速积累或释放。根据公式(

表示电容两端电压的变化量,

表示电容两端电荷的变化量,C为电容的容值),当外部环境的变化驱使器件的工作电压增加或减少时,电容能通过积累或者释放电荷以吸收这种变化,即将器件工作电压的变化转变为电容中电荷的变化,从而保持器件工作电压的稳定。因此,电容的作用之一就是电荷缓冲池,以使高速运行器件的工作电压保持稳定。

2、高频噪声的重要泄放通路

对高速运行的电路而言,无时无刻不存在状态的转变。例如,信号的状态不断在1和0之间切换,器件的电流方向不断在输出和输入之间切换。这种高速的转变,将在电路上产生大量的噪声等干扰。从频谱上看,这些干扰在相当大程度上处于有效信号的2次、3次等倍需要将这些干扰泄放到相对稳定的地平面上,以免影响器件的频频率。在电源传输路径上,当频率较高时,电容表现为低阻抗,因此,可将电容作为高频工作。根据公式 ),噪声的重要泄放通路。

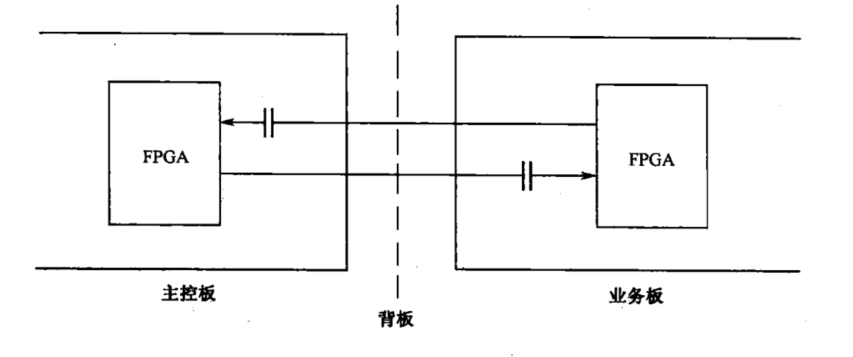

3、实现交流耦合

当两个器件通过高速信号互连时,信号两端的器件可能对直流分量有不同的要求。例如,A和B两个器件之间通过高速差分对信号互连,但A器件工作于1.8V,B器件工作于3.3V,则 A器件驱动的差分对信号将携带 1.8V 直流分量,导致信号到达接收端 B器件时无法被正确识别;反之,B 器件驱动的信号,到达 A 器件,其电平可能超过 A 器件所允许的最大输入电平。对于这种情况,需要将信号所携带的发送端的直流分量在达到接收端前,予以滤除,即隔离信号两边器件的直流分量。基于电容的通交流、阻直流的天然特性,电容具有这种隔离功能。因此,电容的作用之三是实现交流耦合(ACCouple),以实现对直流的隔离(DC Blocking)。

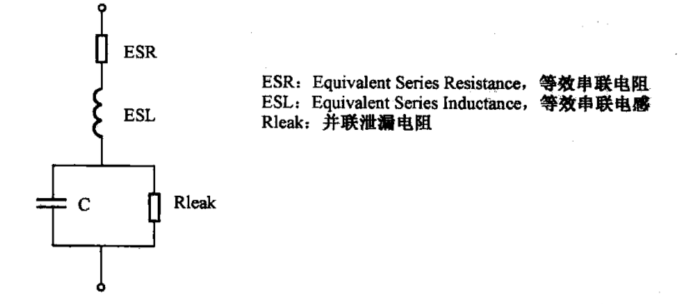

二、电容的等效电路分析

其中 ESL由电容器件的引脚电感和电容器件两极间等效电感串联而成,主要取决于封装;ESR 由电容器件的引脚电阻和电容器件两极间等效电阻构成,主要取决于电容工作温度、工作频率以及电容体本身的导线电阻等;Rleak 则取决于电容器件本身特有的泄漏特性。可以认为,电容器件的特性同时取决于电容分量、ESL分量、ESR 分量及泄漏特性。通过几个案例分别来分析电容器件各分量对高速设计的影响。

(1)电容分量

经测试发现,发送某些码型时,接收方经常检测到数据帧出错。仔细研究出错的码型,发现它们都有一个共同的特性,即存在较长连续0和连续1比特位的情况。从逻辑设计工程师处获知,FPGA 并没有对发送的数据帧进行扰码处理,而是将原始数据帧直接发送到外部信号线上。交流耦合电容在正常工作时,处于平衡的充放电状态,但原始数据帧中较长连0和连1比特位的出现,打破了这种平衡,使得信号通过判决门限的时间发生抖动,导致接收端判决出错。

在交流耦合中,电容串接在线路中,阻抗。容值越小的电容,对低频信号所表现出的阻抗越大,使低频信号的衰减越严重。定义

为每比特位的数据周期,NUM为最大容许连0或连1比特位的数目,负载的抗为 R(一般取 50Ω),C为交流耦合电容容值。则有经验公式:

同时,耦合电容取值也不能太大,如果容值太大,将无法满足高速信号变换的边沿斜率要求。在高速设计中,一般取耦合电容的容值为 0.1μF,这样既可以满足数据帧中可能出现的长1长0情况,又能满足高速信号变换的要求。

(2)ESL分量

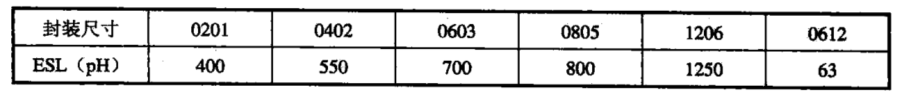

ESL的取值取决于电容器间的类型和封装。

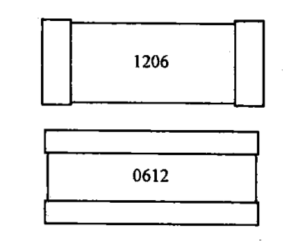

随着封装的增大,ESL 值将随之增大。比较特殊的是0612 封装的贴片电容,其ESL值不仅远远小于相同外形尺寸的1206的ESL值,甚至小于目前业界尺寸最小的0201封装的ESL值。

0612封装的电容,其长边为焊接边,连接PCB上的焊盘,相比1206封装,一方面可以有更大的、能直接和 PCB 焊盘贴合的面积;另一方面,其内部电容体到PCB 焊盘的距离也更近,因此 ESL 值最小。就成本而言,在相同容值的条件下,0612封装比1206封装只是略微贵一些。

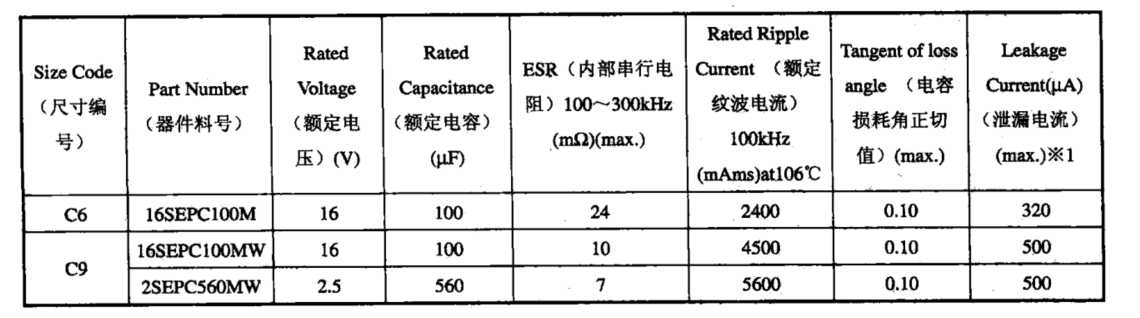

(3)ESR分量、泄露特性及其他信息

提到电容的 ESR,设计者往往想到的都是其负面影响。

第一,根据电容损耗角正切值的定义,较大的ESR会产生较大的损耗功率P,如果P大到一定程度,且单板上该类型的电容器件数目较多时,功耗预算就不得不考虑电容上的损耗,这往往是电子设计工程师最不希望看到的。

第二,对于高速电路设计,往往希望电容的阻抗越小越好。这有两个含义,一方面,对于高频信号的交流耦合,电容串联在高频信号上,目的是隔断高频信号收发两端的直流分量,同时又希望高频信号的衰减越小越好,如果电容的 ESR 较大,对于交流耦合的高频信号,相当于在信号中间串联了一个不小的电阻,将产生一定的衰减;另一方面,对于并联在电源和地之间的滤波电容,其作用是为噪声等干扰信号提供一个极低阻抗的回路,ESR较大的电容,显然无法起到这个作用。对于高速电路,即使 ESR 很小的电容,其 ESR 值仍不能满足低阻抗要求。

不过情况也有例外,本例中电容的 ESR就被用于LDO 芯片的高频补偿。其原理在于当 LDO 电源的负载电流发生瞬时变化时,利用ESR 能立即产生电压波动,从而引起LDO电源反馈电路的动作,以便LDO电源针对负载变化做出快速的调整。

三、滤波电容阻抗随频率变化特性的分析

“低频噪声选用大电容,高频噪声选用小电容”,这是许多工程师达成的共识。然而在实际工作中,这种说法并不完全成立。

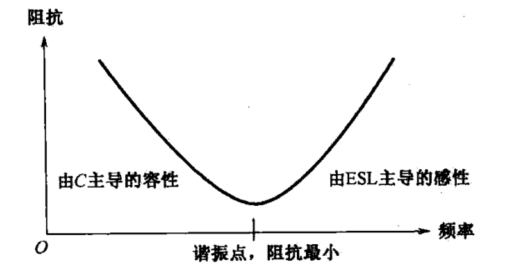

对电容器件而言,由于电容分量的存在,电容器件的阻抗随着频率的升高而逐渐降低,这是电容器件的本体属性;ESL分量则使阻抗随着频率的升高而逐渐增加。这两种作用正好相反。在电容分量和ESL 分量的共同作用下,电容器件的整体阻抗表现为,随着频率的升高,首先是电容分量起主导作用,使阻抗逐步变小,器件表现为电容的阻抗特性,滤波效果渐强;当达到某一频点时发生谐振,此时电容分量和ESL分量对阻抗的效果正好抵消,在谐振点上,电容器件阻抗最小,等于ESR分量;此后,随着频率继续升高,BSL分量起主导作用,使阻抗逐步增大,器件表现为电感的阻抗特性,滤波效果渐弱。

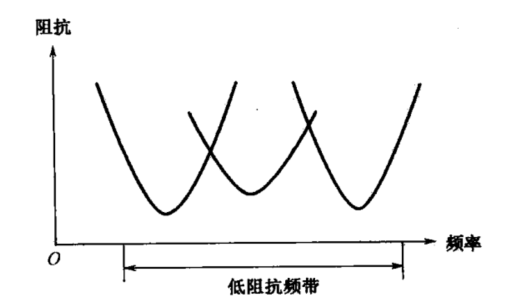

高速设计中,噪声等干扰往往不是处在一个频率点上,而是占据一段频带。在实际工作中,期望电路上每一处的噪声频带都得到准确定位并不现实,这就要求设计者在电路设计中,利用多种不同的电容构造一个比较宽的低阻抗频带,以尽可能地覆盖噪声频带。

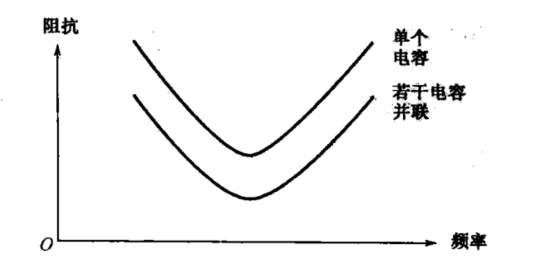

此处需做一些补充,设计者们常喜欢把若干相同的电容并联在一起,共同为某一电源滤波。这样做的目的,一方面是起到去耦电容的本地“小池塘”作用(参见2.2.4节),另一方面是为了在谐振点上得到更低的阻抗。需要说明的是,这样做,并没有展宽低阻抗频带。

四、高速电路设计常用电容及其应用要点

1、陶瓷电容及其应用要点

陶瓷电容是以陶瓷作为介质,在陶瓷的两面喷涂金属作为极板构成的,其优势是体积小、价格低、稳定性好,但容量小。目前常用的陶瓷电容,其容值小的可以到几十皮法,大的可以到几十微法。

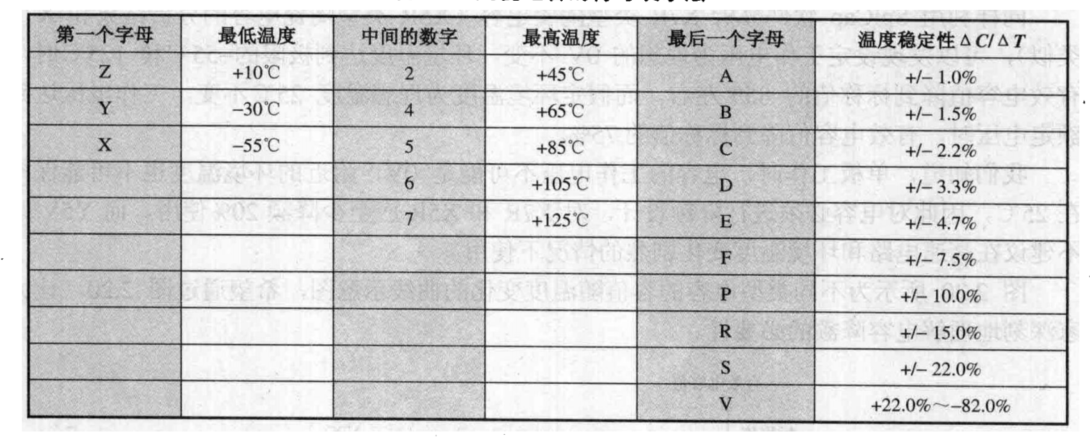

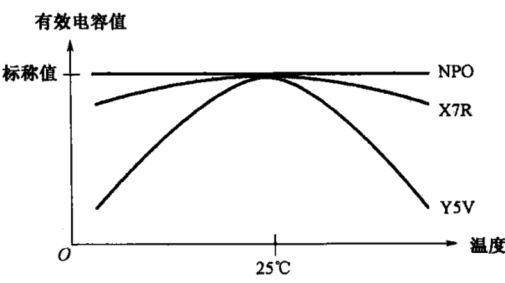

在高频电路设计中,推荐选用 NPO、X7R、X5R 类型,尽量不选用 Y5V类型。

2、钽电容及其应用要点

钽电容使用金属钽作为介质,基于钽的固态特质,具有温度特性好、ESL值小、高频滤波性能好、体积小、节省 PCB 面积、容值较大等特点。因此钽电容一般被应用在需要大容量电容滤波的场合,如为CPU等高耗能器件滤波。在设计中,往往将若干小容值的钽电容并联以提供和大容值钽电容相同的容量,这样做,一方面有利于设计的可靠性,一方面也有利于成本的降低。

钽电容的缺点是耐电压和耐电流的能力较弱。一般要求钽电容的工作电压相对额定电压降额 50%以上。遇到以下三种场合之一,钽电容的额定电压需降额 70%以上使用:

(1)负载呈现较强的感性;

(2)串联电阻小;

(3)瞬变电流较大。

其原因在于,感性负载或较小的串联电阻会导致较大的瞬变电流,造成钽电容的金属钽介质被击穿。这使得在以下环节,钽电容的失效概率增大:ICT 测试、老化测试、系统开机瞬间、单板热插拔瞬间。

3、铝电解电容及其应用要点

铝电解电容使用电解液作为介质,外壳的铝制圆简作为负极,内部插入一块金属板作为正极。铝电容容量大、耐压高,但温度稳定性差、精度差、高频滤波性能差,仅适用于低频滤波。

在对钽电容的介绍中提到,钽电容不适用于有较大瞬变电流的场合,而在这种场合下,就需要用到铝电解电容。

在应用中,铝电解电容的电压降额要求至少为20%。铝电解电容一般都是插装式,因此ESR、ESL 值都比较大,同时由于其采用液体作为介质,在极高温和极低温环境下,性能也极不稳定。

从产品的长期稳定性来说,铝电解电容也可能成为隐患。因为随着产品使用时间的增铝电解电容内部的电解液将逐渐干涸,容量逐渐减小,ESR 逐渐增大,滤波效果减弱加,所以在高速电路设计的电容选型中,应尽量避免选择铝电解电容。

4、OSCON 电容及其应用要点

严格地说,OSCON 并不是一种电容的类型,而是SANYO 公司的一种性能比较好的电

解电容的品牌。

OSCON 电容外形酷似铝电解电容,其优点在于,OSCON电容 ESR较小、温度稳定性相对铝电解电容较好、价格相对钽电容较低。缺点在于对绝大多数OSCON 电容而言,引脚都是插装形式,并且体积比较大。

在电路设计中,DC/DC 电源的输入和输出部分往往需要布放大容量的钽电容,成本较高。在这种情况下,可以同样容值的 OSCON 电容取代,其成本仅为对应钽电容的几分之一。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?