10bit 100MS s 流水线Pipelined ADC电路,采用0.18um工艺,直接可以用,直接可以跑仿真,包含实际电路和各模块的测试电路,有效位9.5bit,适合学习。

题目:10bit 100MS/s 流水线 ADC 电路设计与实现

摘要:本文介绍了一种基于流水线 Pipelined 架构的 10bit 100MS/s ADC 电路设计与实现。该电路采用了 0.18um 工艺,并提供了实际电路和各模块的测试电路。通过对电路的分析和仿真验证,本文详细阐述了电路的设计思路、搭建流程以及性能指标。最终得出,该电路的有效位达到 9.5bit,适合学习和实际应用场景。

一、背景

高速高精度的 ADC 电路在工业控制、通讯和娱乐等多个领域有着广泛的应用。其中,流水线 ADC 电路因其具有高速度、高精度、低功耗等优势而备受青睐。流水线 ADC 电路的设计涉及到多个模块的设计和协同工作,其设计难度较大,但具有可扩展性和灵活性,可以适应不同分辨率和速率的要求。

二、设计思路

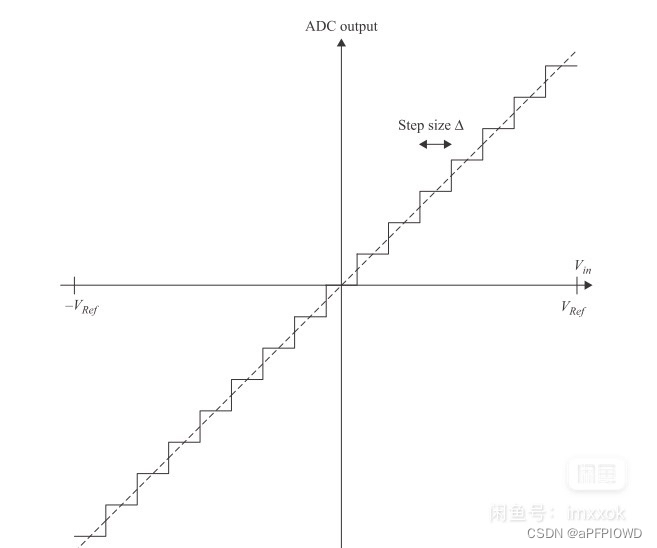

本文采用的是基于流水线 Pipelined 架构的 ADC 电路设计。该架构将 ADC 电路分为多个流水段,通过多级时钟同步实现对输入信号的逐级采样和转换,从而提高了转换速率和精度。此外,本文采用了 0.18um 工艺,以实现高速、高精度和低功耗的要求。

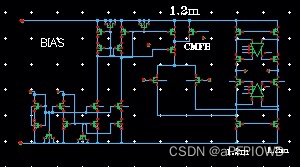

三、电路设计与实现

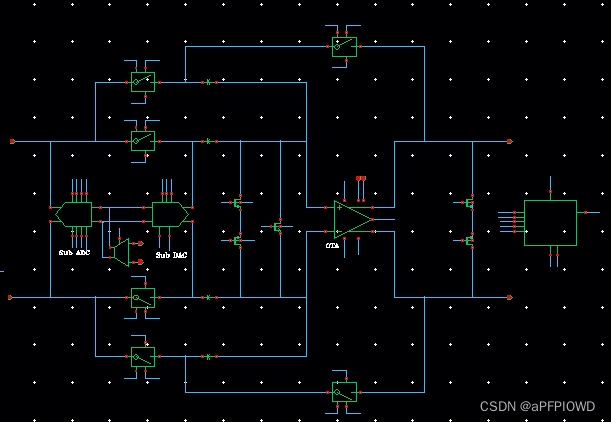

- 采样保持电路

采样保持电路是 ADC 电路的第一个模块,其功能是对输入信号进行采样、保持和转换到模拟电压。在本文中,采用了基于运放的采样保持电路。根据需求,采样保持电路的带宽要大于采样频率的一半,以确保采样精度。

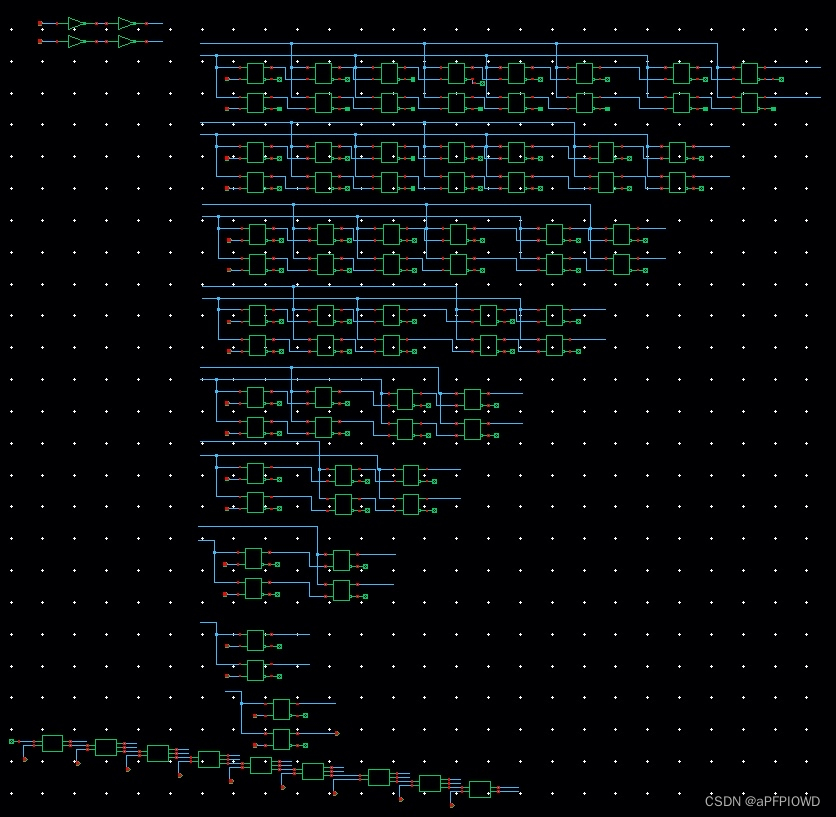

- 流水线 ADC 电路

流水线 ADC 电路由多个流水段组成,每个流水段负责对采样保持后的电压进行转换和处理。在本文中,采用了 4 个流水段的结构,以实现 10bit 的分辨率和 100MS/s 的速率。其中,每个流水段由一个比较器和一个 2bit 的 MDAC 模块组成,负责将输入电压转换为数字量。

- 数字电路

数字电路包括逻辑电路和时序电路。本电路采用的是基于 FPGA 的数字电路,采用 Verilog 语言编写,以实现对 ADC 电路的控制和输出。其中,时序电路根据时钟信号实现对数字电路的同步和控制,逻辑电路实现数字信号的编解码和输出。

四、性能指标

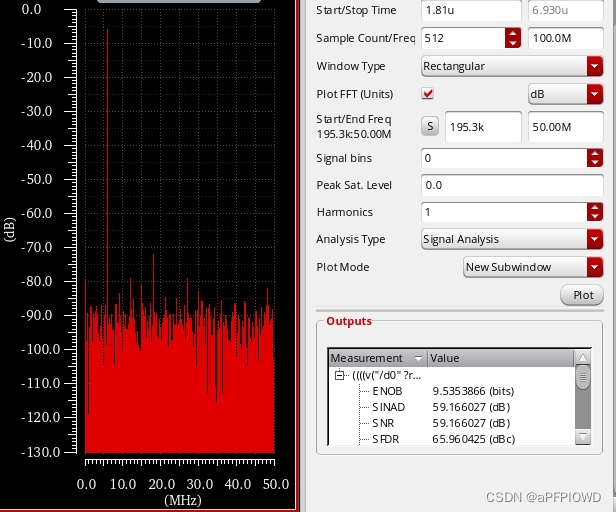

通过对 ADC 电路的仿真和测试,本文得出以下性能指标:

-

有效位数:9.5bit

-

采样率:100MS/s

-

差分非线性误差(DNL):±0.5LSB

-

积分非线性误差(INL):±1.5LSB

五、结论

本文介绍了一种基于流水线 Pipelined 架构的 10bit 100MS/s ADC 电路设计与实现。通过对电路的分析和仿真验证,得出了有效位数为 9.5bit,适合学习和实际应用场景。该电路的高速、高精度和低功耗特性,能够满足各种领域的需求。

相关代码,程序地址:http://lanzouw.top/677347530443.html

1830

1830

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?