笔记以及图片来源于

存储容量的拓展

计算机组成原理(哈工大刘宏伟)

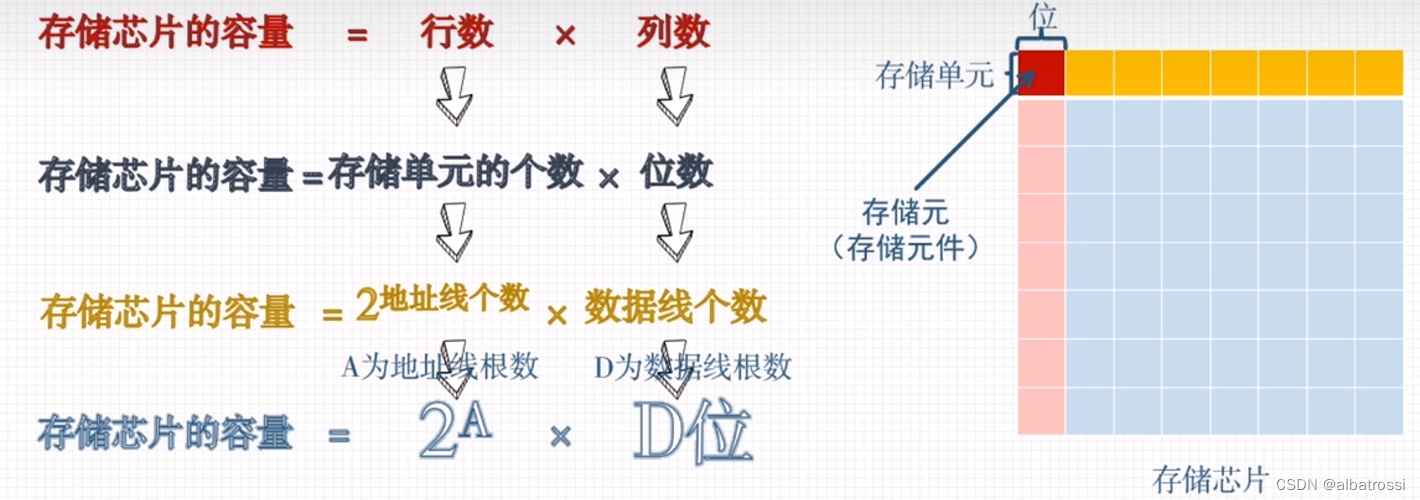

存储容量的扩展

单个存储芯片的地址空间是有限的,因此需要进行存储容量的扩展,主要有以下三种扩展方式

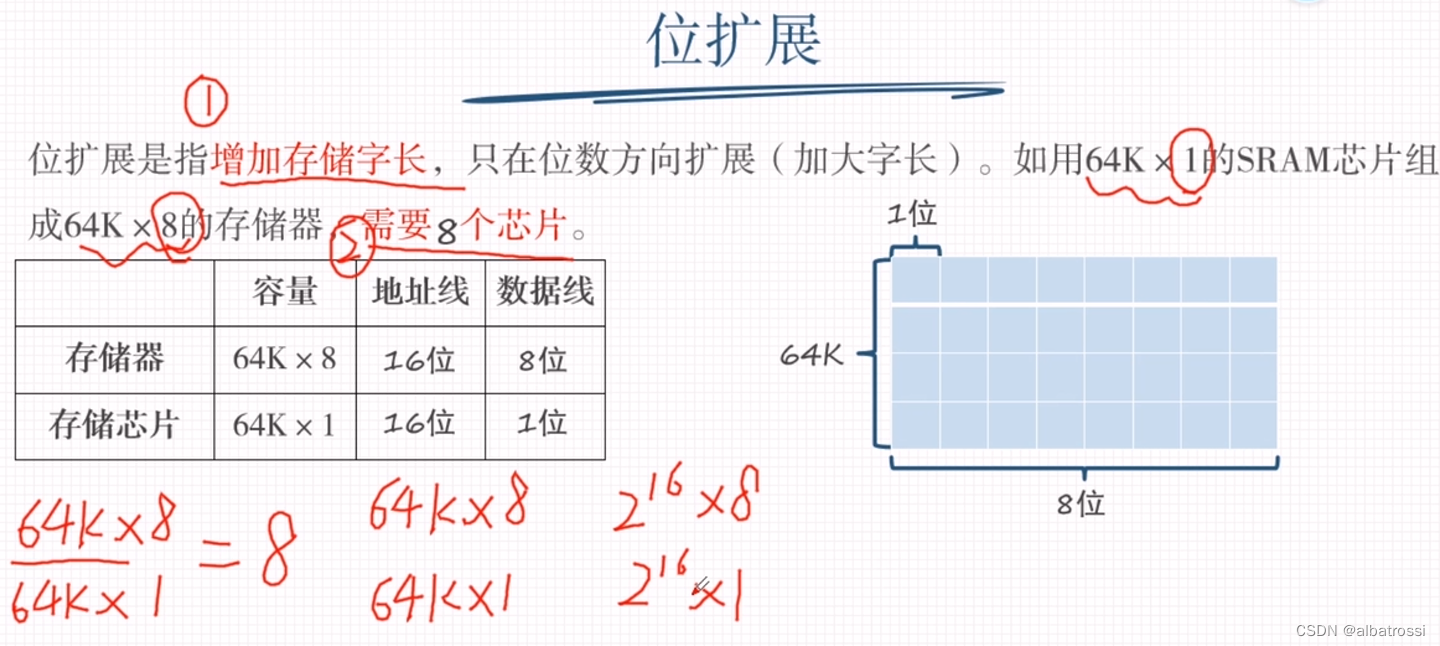

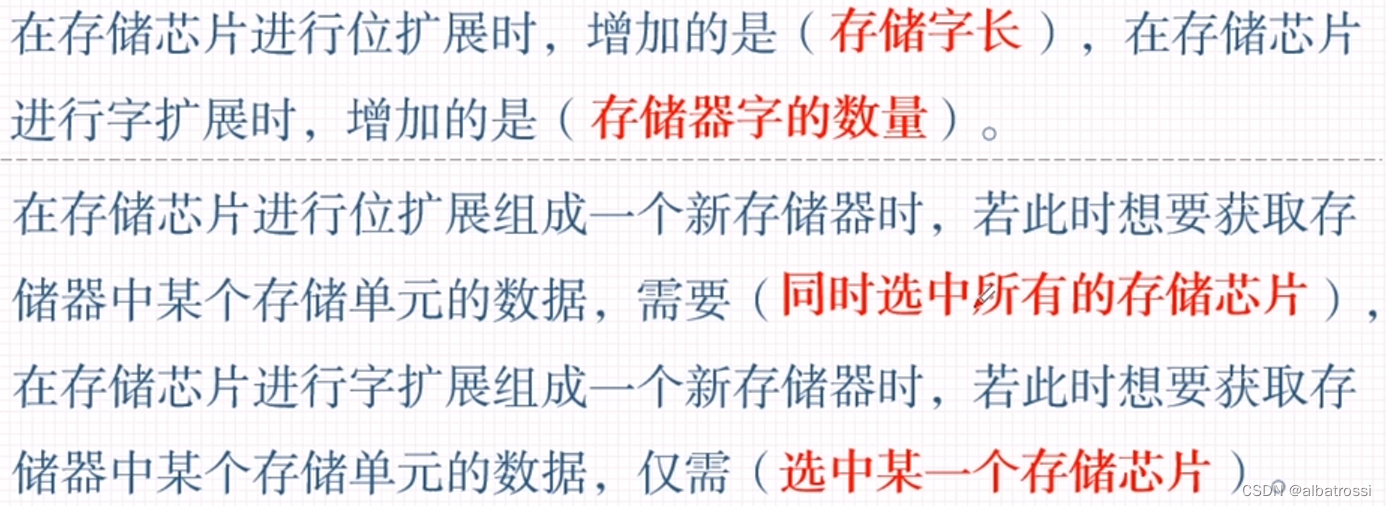

位扩展

增加存储字长,只在位数方向拓展(加大子长)

位扩展的连接方式是将各存储芯片的地址线,片选线(CS)和读/写(WE)线相应地并联起来而将个芯片的数据线单独列出。当CPU访问该存储器时,将发出的地址和控制信号同时传给8个芯片,选中每个芯片的同一单元,其单元的内容被同时读至总线的相应位,或将总线上的内容分别同时写入相应单元。

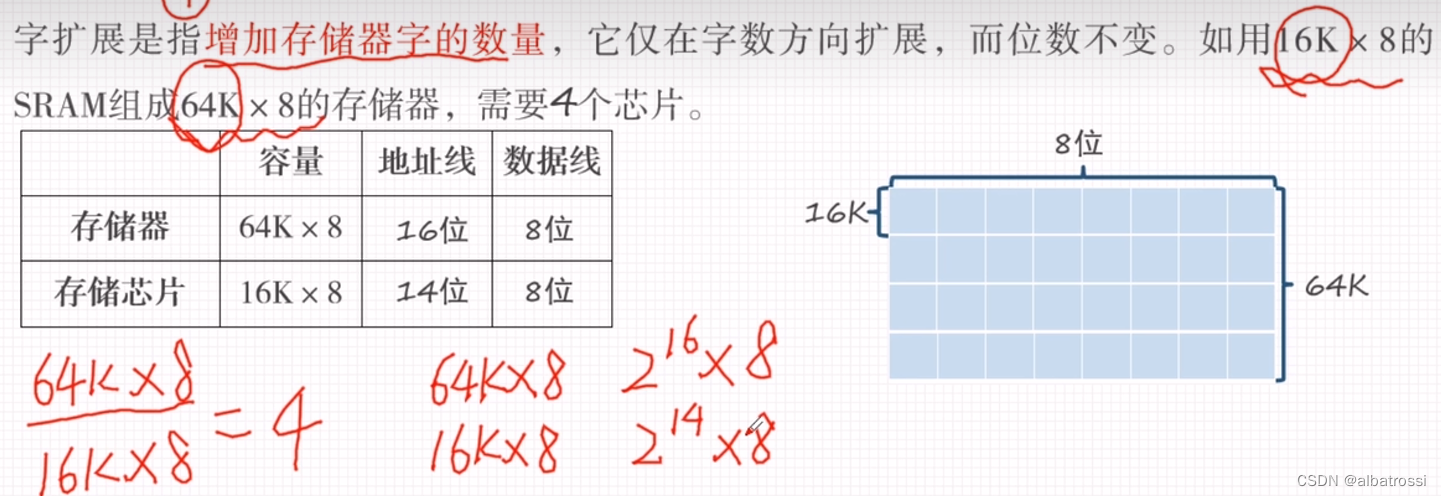

字扩展

增加存储器字的数量,仅在字数方向拓展,而位数不变。

扩充了两根地址线,也就是说有四种不同的状态

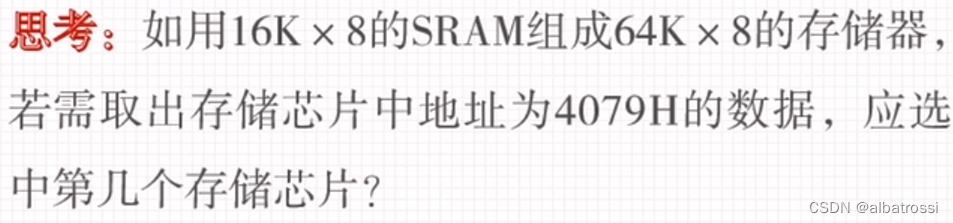

第一种方式: 存储器的容量/存储芯片的容量=芯片数量

第二种方式 :分析

字拓展芯片的地址线,数据线,读/写线并联,由片选信号来区分各个芯片,在同一时间内四个芯片只能有一个芯片被选中。

计算题:

由于存储空间是连续的,第二篇存储芯片的最低地址,在第一片存储芯片的最高地址上再加上1,并且最高地址与最低地址之间的差值是固定的,以此类推可得

而我们需要寻找的地址就在第二片最高地址和最低地址之间。

字和位同时拓展

字和位同时拓展是指既增加存储字的数量,又增加存储字长。当构成一个容量较大的存储器时,往往需要在字数和位数方向上同时拓展。

1MB = 2的20次方

一个字节 = 8位

存储器的校验

编码的最小距离

任意两组合法代码之间二进制位的最少差异。

编码的检测能力和纠错能力和最小距离有关。

L - 1 = D + C (D≥C)

L —— 编码的最小距离

D —— 检测错误的位数

C —— 纠正错误的位数

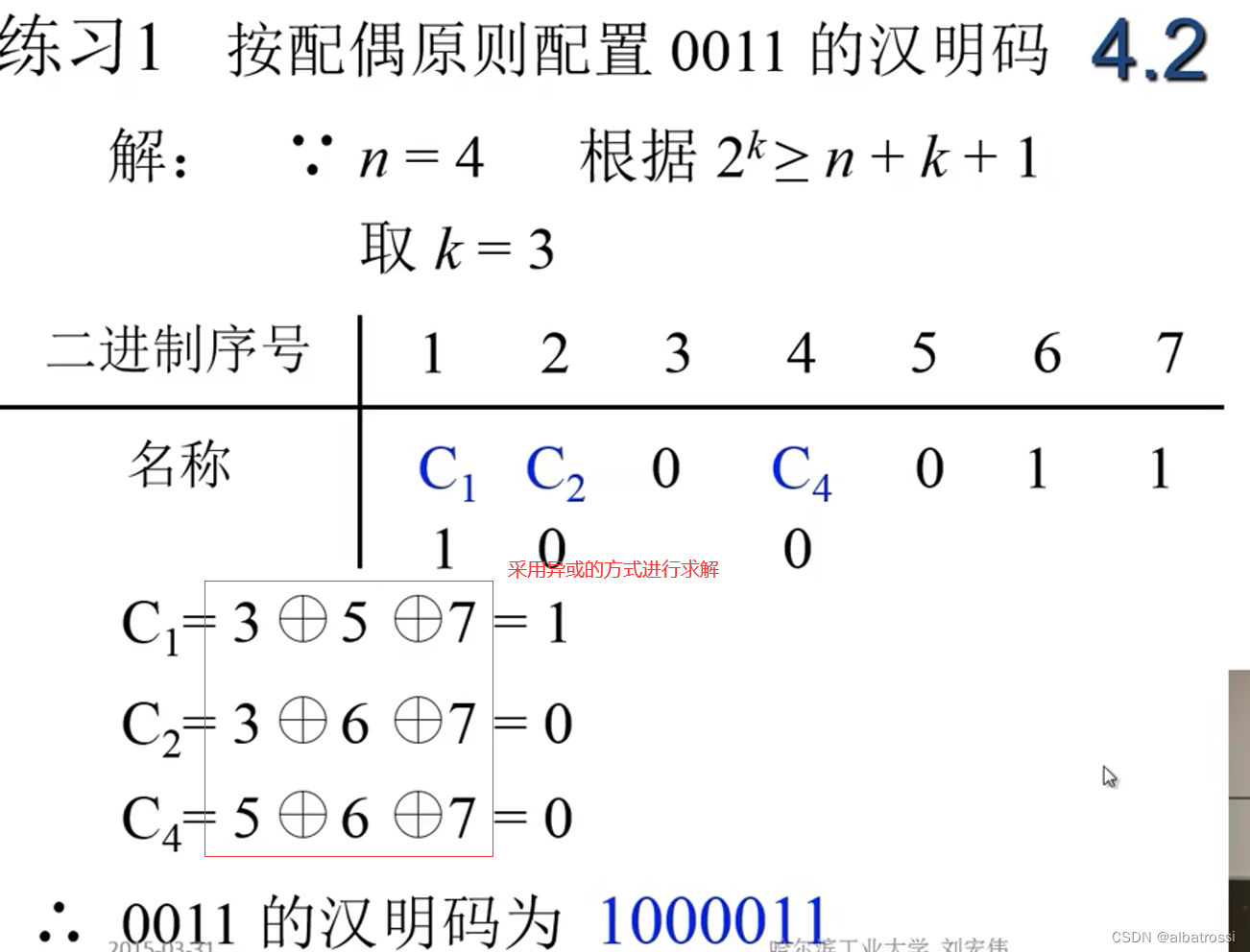

汉明码的组成

- 汉明码采用奇偶检验

- 汉明码采用分组校验

- 汉明码的分组是一种非划分方式

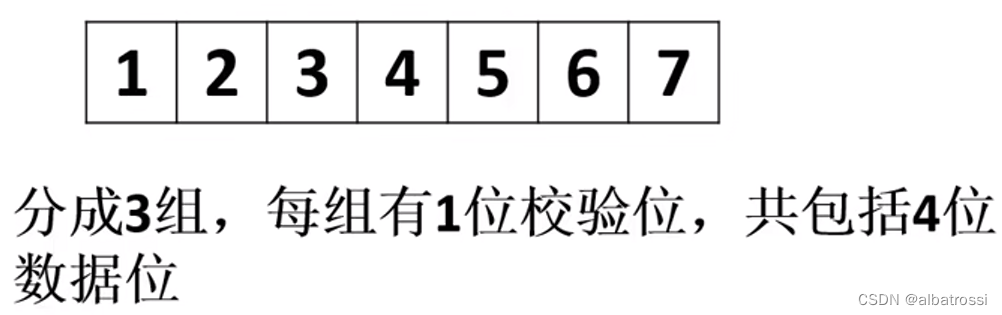

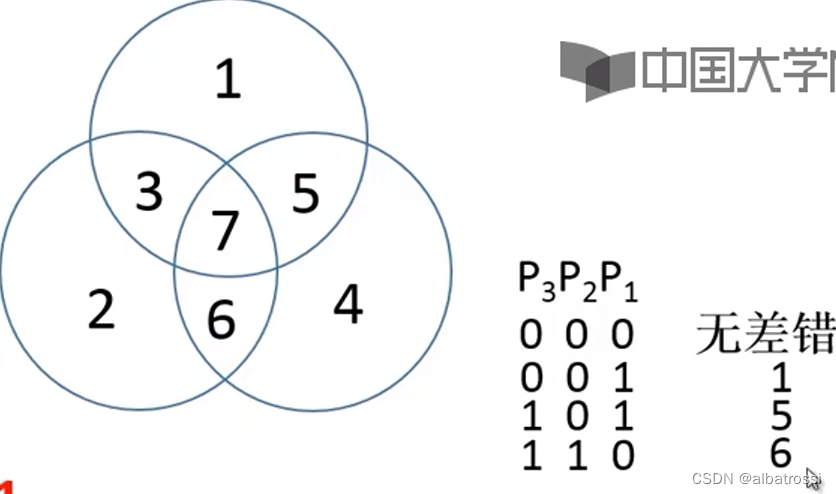

将以上数据分为三组,每组有1位校验位,共包括4位数据位,根据错误的校验码和重叠的情况,能够很快的找到出现差错的位置。

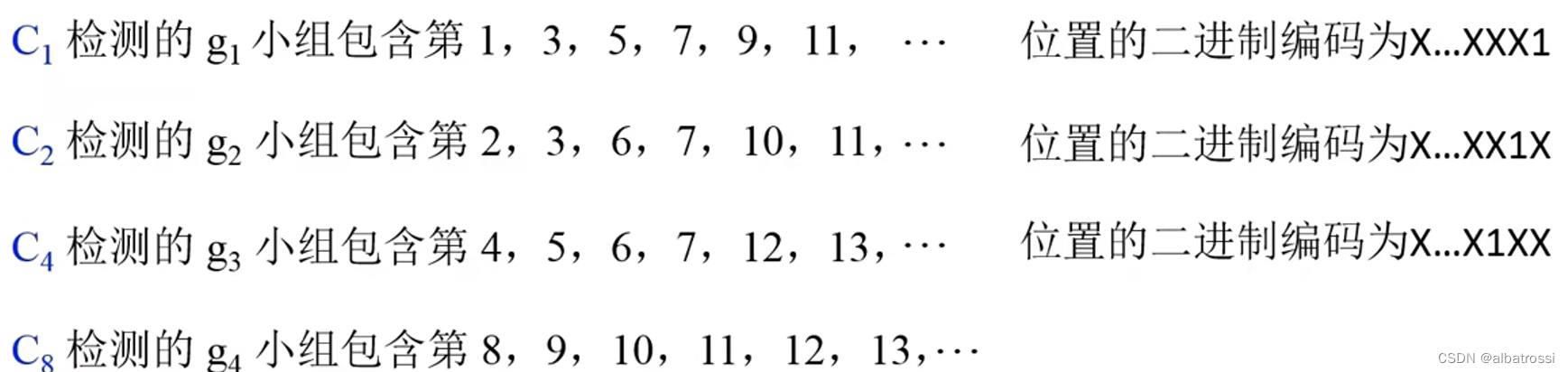

那么如何进行分组呢?

第1组 XXXX1

第2组 XXX1X

第3组 XX1XX

第4组 X1XXX

第5组 1XXXX

既根据二进制编码的位置 ,对应1,2,4,8

汉明码的组成

汉明码的组成需要增添k位检测位

检测位的位置

检测位的取值

检测位的取值与该位所在检测“小组”承担的奇偶校验任务有关。

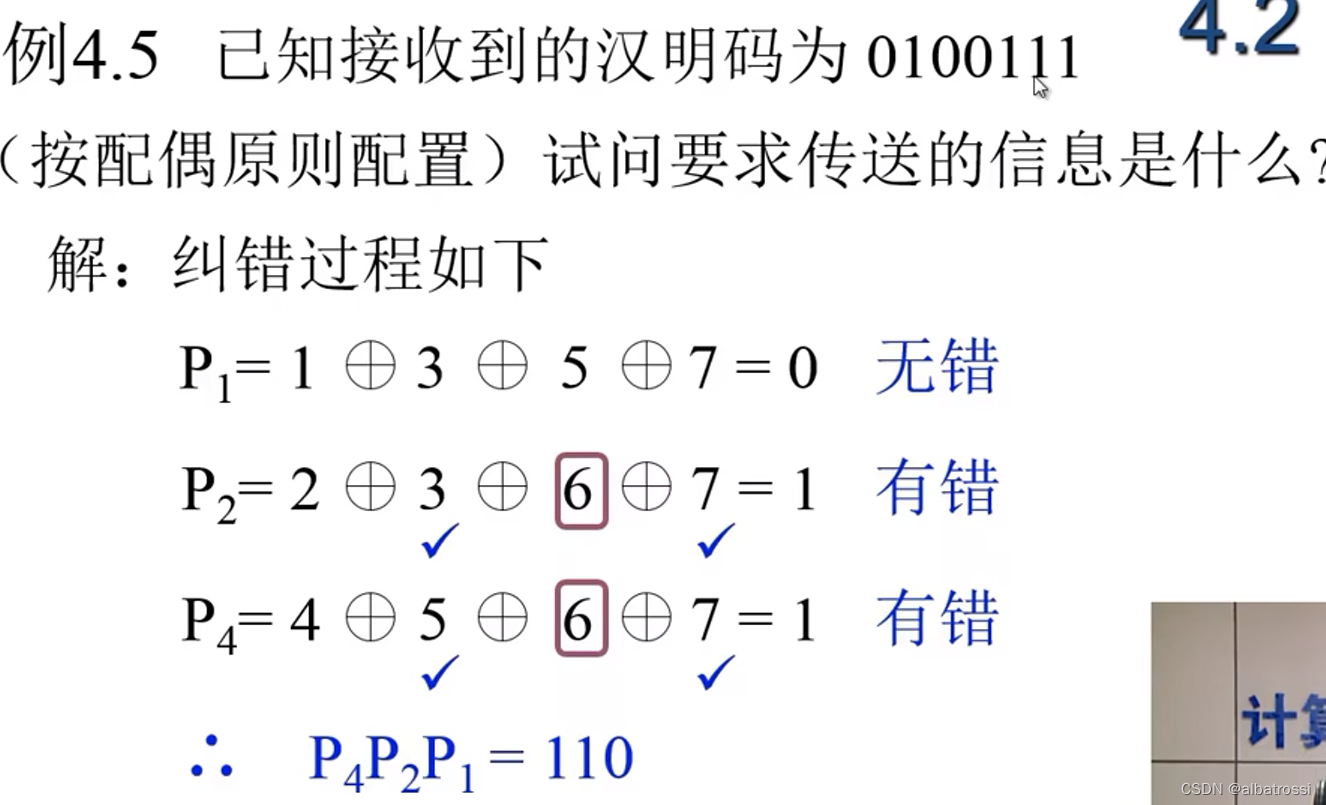

汉明码的纠错过程

形成新的检测位Pi,其位数与增添的检测位有关。

对于按“偶校验”配置的汉明码,不出错时,所有的校验位的值为1。

为什么能确定出错位置不是6而是1呢?

因为位置7在第一组中也出现了,然而第一组的校验结果是正确的。

故可知是第六位出错,可纠正为0100101,故要求传送的信息为0101。

如果是按照奇校验的方法则刚好相反。

提高访存速度的的措施

- 采用高速器件

- 采用层次结构Cache —— 主存

- 调整主存结构

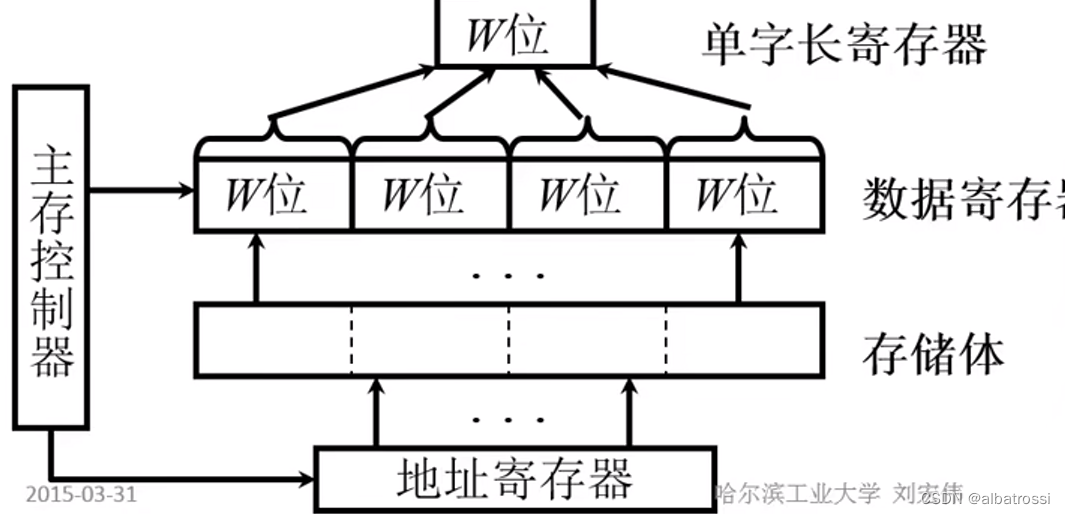

单体多字系统

原假设存储字长等于机器字长,也就是说CPU一次从存储器当中只能取出一条指令(与机器字长相等的数据)

单体多字系统:把存储器的存储字长加长(增加存储器的带宽),比如,CPU为16位,存储字长我们可以设计成64位,CPU每一次访问存储器,都可以访问出4个机器字(4条指令),下一次再取指令时,就可以从数据寄存器当中读取指令。

单体多字系统的缺陷:

(1)CPU如果需要存储16位数据,需要先把数据放在单字长寄存器中,再放入数据寄存器中,然后再存储到存储体中,我们可能只想要写入16位,但是其他的48位也会被写入,并且这48位数据很可能是错的,如果需要改善这种情况,还需要用硬件来实现这个功能,因此比较复杂。

(2)指令和数据在主存内必须是连续存放的,一旦遇到转移指令或者操作数不能连续存放,则方法的效果就不明显。

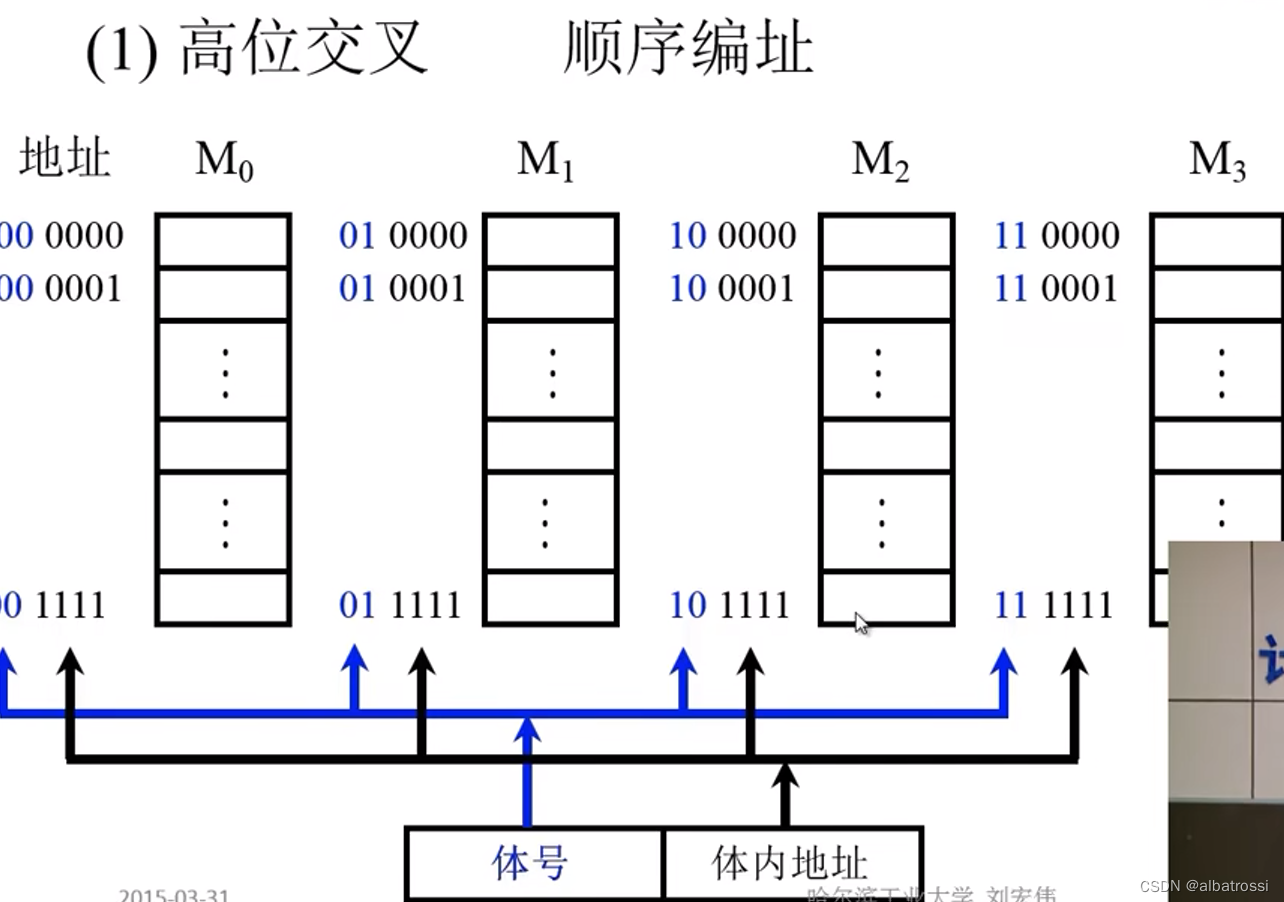

多体并行系统

- 高位交叉

顺序对存储体进行编码(编完第一个存储体,再编第二个存储体),前两位00为存储体的编号,后四位为存储体中的地址的编号,每一个存储体都有单独的数据寄存器和地址寄存器,能独立处理读写信号,从而达到4个存储体并行工作的效果。

不足:如果按序存储和按序读取,那么4个存储体中,可能存在有一个存储体非常繁忙,而其他几个存储体非常空闲的情况。

这种方式适合存储器容量扩展,但是并不适合提高存储器带宽。

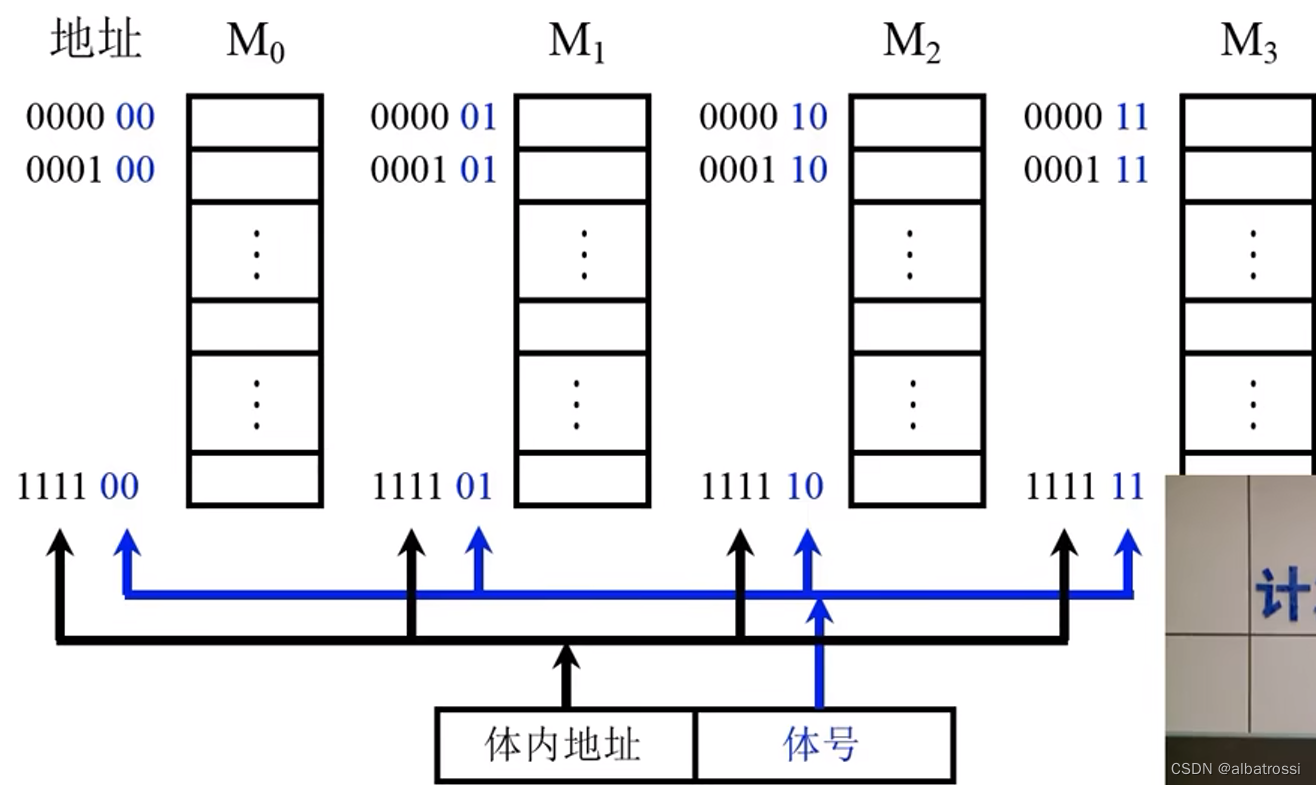

- 低位交叉——用于带宽访问速度提高

对高位交叉进行改进,横向对存储体进行编码(各个体轮流编址),前四位为存储体中的地址的编号,后两位为存储体的地址。

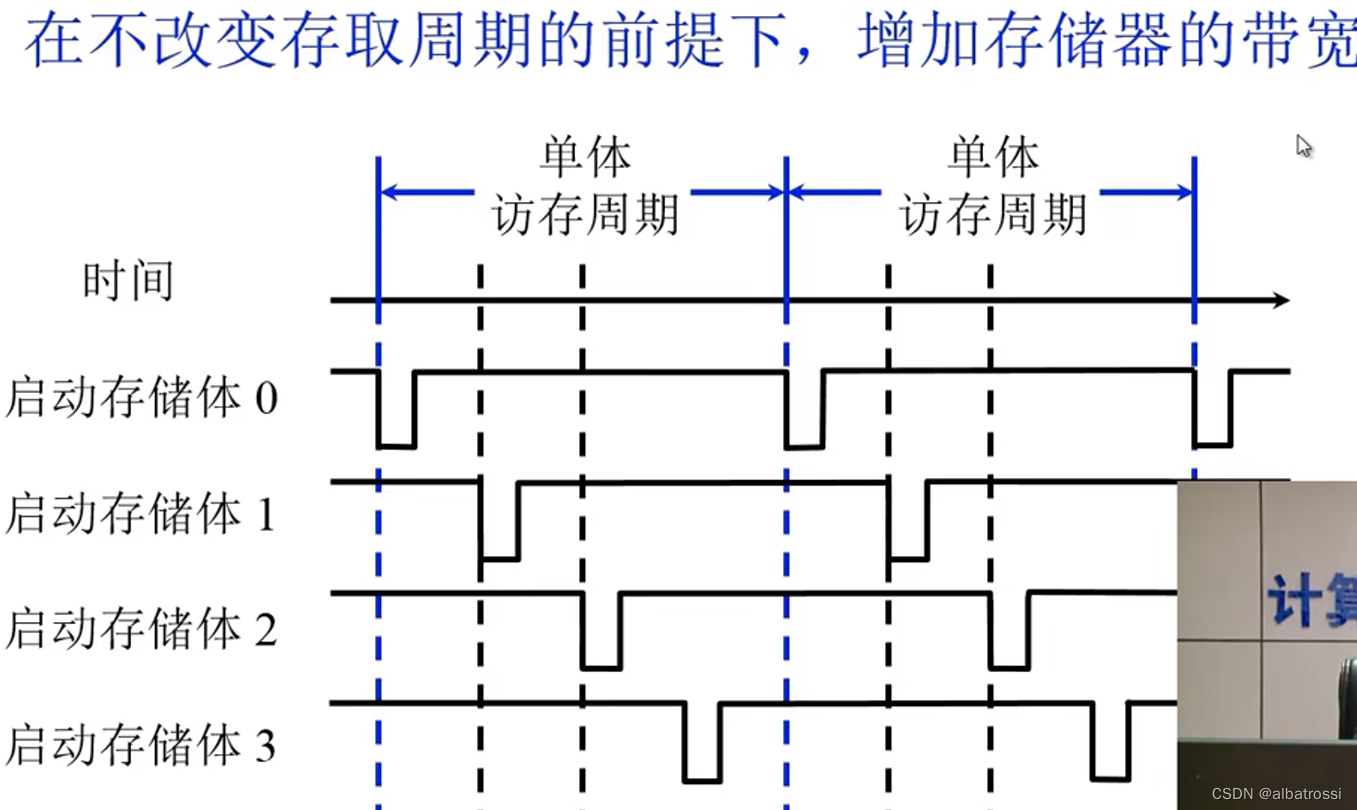

低位交叉的特点: 在不改变存取周期的前提下,增加存储器的带宽

上图显示了,低位用来选择存储体,高位选择每个存储体对应的存储单元。

低位交叉的特点:不改变存取周期的前提下,增加存储器的带宽。

设四体低位交叉存储器,存取周期为 T,总线传输周期为 τ ,为实现流水线方式存取,应满足 T = 4 τ 。

连续读取 4 个字所需的时间为 t1 = T + (4 - 1) τ

若采用高位交叉编址,则连续读取n个字所需时间为 t2 = nT。

高性能存储芯片

(1)SDRAM (同步 DRAM)

在系统时钟的控制下进行读出和写入—— CPU 无须等待

(2)RDRAM

由 Rambus 开发,主要解决 存储器带宽 问题

(3)带 Cache 的 DRAM

在 DRAM 的芯片内 集成 了一个由 SRAM 组成的 Cache ,有利于猝发式读取 (连续的存储单元进行读取)

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?