本章将开始总结多路复用的相关器件

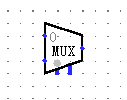

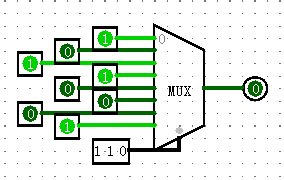

1. Multiplexer

多路输入选择器,一个梯形的器件,表示其具有方向性。

作用

通过控制门来控制左侧的多个输入,哪一个能在右侧输出端输出。

下侧有两个输入接口,左侧为控制门,通过不同二进制数控制输出哪一个值;右侧为使能端,控制该元件能否生效。

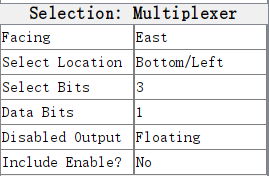

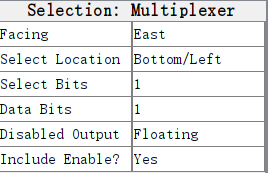

属性

disabled output:控制当使能端输入0时,即元件失效时,输出端该显示什么值。可以浮动(x),也可以置0.

include enable?:控制使能端的存在,可以设置为no,即屏蔽使能端,保证原件有效。

说明:此处的select bits控制选择对象的个数,但是也决定着控制门的输入位数(请读者思考为什么)。由于控制门需要对应每一个数据,所以控制门的位数需要能满足一一对应关系,事实上,select bits 等于控制门的位数。

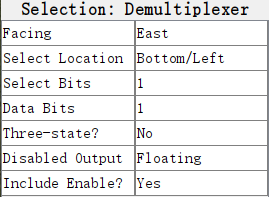

2.Demultiplexer

多路输出选择器,容易猜到,其作用与多路输入选择器相反。

作用

同一输入,通过控制门选择输出到右侧的某一个输出端。

属性

three-state?:用来控制未被选择的输出端应该置什么值,yes——浮动;no——0

其余属性与多路选择输入器一致

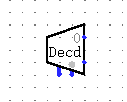

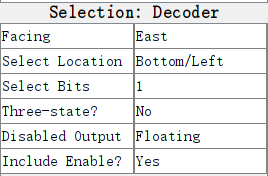

3.Decoder

解码器,是多路选择输出器的简化版,等价于多路选择输出器的输入端置1.

作用

通过选择门,决定右侧哪一个输出 1 。原理与多路选择输出器一致。

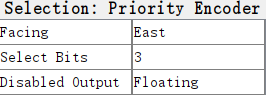

4.Priority Encoder

优先解码器

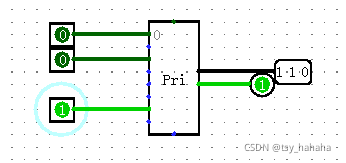

作用

接受多个输入,输入的值只能是1和0,在元件右侧有两个接口,上侧接口的输出为左侧最后一个输入为1的接口的位置(二进制表示,并且编号图中的0开始依次增大);下侧接口输出是否存在1,如果输入全为0,则该输出为0,存在输入为1,则该输出为1.

属性

disabled output:如果左侧全为0时,右侧应该输出的值,0或浮动(x)

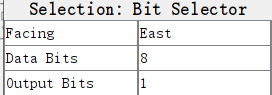

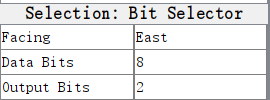

5.Bit Selector

位选择器

作用

将输入的多位数据按位平均分配,得到一组位数相同的数据,并以此按位的低到高顺序排列。然后通过控制门(其位数也要满足前面所讲的对应条件),控制输出哪一个数据

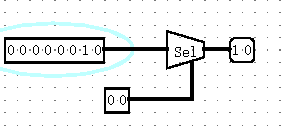

如这个例子,设置输出的位数为2,于是输入的八位数据被平均分为四个数据,每个数据都是两位:10,00,00,00.并且顺序是按八位输入数据的低到高排列的,而控制门输入为00,所以输出第一个数据也就是10.另外,如果输出的位数不能整除输入的位数,那么会在输入数据前端补0,直至整除。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?